一种提高单向TVS浪涌电流性能的方法与流程

实施例涉及电路保护器件(包括瞬态电压抑制器器件)领域。

背景技术:

1、半导体器件,例如瞬态电压抑制器(tvs)器件,可制成单向器件或双向器件。在许多应用中,tvs二极管可用于保护敏感电路节点免受一次性和限时过电压故障的影响。这种tvs二极管也用于现代大功率igbt电路中,以防止集电极电路中的过载。为了获得高电流密度性能,通常使用p型或n型si作为基极(base)材料,同时用不同类型杂质掺杂基板以形成pn结。在这种情况下,浪涌电流性能主要取决于pn结尺寸、串联电阻和接触电阻。对于给定芯片尺寸的特定工艺,浪涌电流性能(ipp)几乎是固定的。

2、关于这些和其他考虑,提供了本公开。

技术实现思路

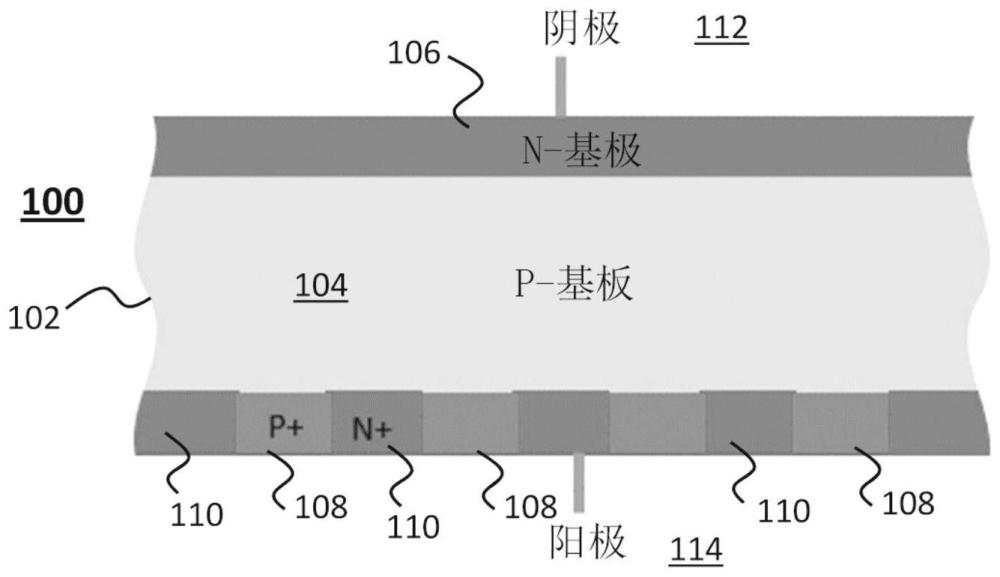

1、在一个实施例中,提供了瞬态电压抑制(tvs)器件。tvs器件可以包括基板,该基板包括第一类型的极性、第一掺杂剂层,第一掺杂剂层设置在基板的第一主表面上并包括第二类型的极性,其中,第一掺杂剂层与基板形成p/n结。tvs器件还可以包括设置在与第一主表面相对的基板的第二主表面上的第二掺杂剂层和设置在基板的第二主表面上的图案化层,第二层包括第一类型的极性,图案化层包括第二类型的极性,其中,图案化层散布于第二层。

2、在另一个实施例中,单向瞬态电压抑制(tvs)器件可以包括基板,该基板包括第一类型的极性。单向tvs器件还可以包括第一掺杂剂层,其作为覆盖层(blanket layer)被设置在基板的第一主表面上,第一层包括第二类型的极性,其中,第一掺杂剂层与基板形成p/n结。单向tvs器件还可以包括第二掺杂剂层,其设置在与第一主表面相对的基板的第二主表面上,第二层包括第一类型的极性。单向tvs器件还可以包括设置在基板的第二主表面上的图案化层,图案化层包括第二类型的极性,其中,图案化层散布为被第二层包围的隔离岛的二维阵列。

3、在另一个实施例中,提供了一种形成瞬态电压抑制(tvs)器件的方法。该方法可以包括提供包括第一类型的极性的基板;在基板的第一主表面上形成第一掺杂剂层,第一掺杂剂层包括第二类型的极性,其中,第一掺杂剂层与基板形成p/n结。该方法可以包括在与第一主表面相对的基板的第二主表面上形成第二掺杂剂层,第二层包括第一类型的极性,并且用第二类型的掺杂剂选择性地掺杂基板的第二主表面以形成散布于第二层的图案化层。

技术特征:

1.一种瞬态电压抑制(tvs)器件,包括:

2.根据权利要求1所述的tvs器件,

3.根据权利要求2所述的tvs器件,其中,所述tvs器件包括npp+结构和npn+结构的组合。

4.根据权利要求1所述的tvs器件,

5.根据权利要求4所述的tvs器件,其中,所述tvs器件包括pnn+结构和pnp+结构的组合。

6.根据权利要求1所述的tvs器件,其中,所述图案化层包括彼此隔离的多个区域,并且被由所述第二掺杂剂层形成的矩阵包围。

7.根据权利要求6所述的tvs器件,其中,所述多个区域具有矩形形状、椭圆形形状或多边形形状。

8.根据权利要求1所述的tvs器件,其中,所述第二掺杂剂层和所述图案化层具有在5微米至50微米范围内的厚度。

9.一种单向瞬态电压抑制(tvs)器件,包括:

10.根据权利要求9所述的单向tvs器件,

11.根据权利要求10所述的单向tvs器件,包括npp+结构和npn+结构的组合。

12.根据权利要求9所述的单向tvs器件,

13.根据权利要求12所述的单向tvs器件,包括pnn+结构和pnp+结构的组合。

14.根据权利要求9所述的单向tvs器件,其中,所述隔离岛的二维阵列具有矩形形状、椭圆形形状或多边形形状。

15.根据权利要求9所述的单向tvs器件,其中,所述第二掺杂剂层和所述图案化层具有在5微米至50微米范围内的厚度。

16.一种形成瞬态电压抑制(tvs)器件的方法,包括:

17.根据权利要求16所述的方法,

18.根据权利要求16所述的方法,

19.根据权利要求16所述的方法,其中,所述图案化层包括彼此隔离的多个区域,并且被由所述第二掺杂剂层形成的矩阵包围。

20.根据权利要求19所述的方法,其中,所述多个区域具有矩形形状、椭圆形形状或多边形形状。

技术总结

公开了一种提高单向TVS浪涌电流性能的方法。TVS器件可以包括基板,该基板包括第一类型的极性、设置在基板的第一主表面上的第一掺杂剂层,并且包括第二类型的极性,其中,第一掺杂剂层与基板形成P/N结。TVS器件还可以包括设置在与第一主表面相对的基板的第二主表面上的第二掺杂剂层和设置在基板的第二主要表面上的图案化层,第二层包括第一类型的极性,图案化层包括第二类型的极性,其中,图案化层散布于第二层。

技术研发人员:周继峰,张环,高超

受保护的技术使用者:力特半导体(无锡)有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!