半导体器件及其制造方法与流程

1.本发明涉及半导体技术领域,特别涉及一种半导体器件及其制造方法。

背景技术:

2.随着人们生活水平的提高,电子产品的应用越来越广泛,而电子产品中通常会用到各种半导体产品。随着科技的发展及人们需求的增加,人们对半导体产品的性能要求也越来越高。

3.金属互连工艺是半导体工艺中常用的工艺,而传统的金属互连工艺中,去胶工艺通常是在高温高压的环境中,采用大流量的氧气来灰化光阻层。然而,在双大马士革(dd,dual damascus)工艺中广泛应用低介电材料,此时,若使用传统的灰化工艺将会使得低介电材料层的侧壁损伤,导致半导体结构的性能降低,良率损失。

技术实现要素:

4.本发明的目的在于提供一种半导体结构及其制造方法,以解决现有金属连接结构品质不佳导致短路且电阻增大,而导致的产品性能差及良率低的问题。

5.为解决上述问题,本发明提供一种半导体结构的制造方法,所述方法包括:

6.提供衬底;

7.在所述衬底上形成第一金属层;

8.在所述第一金属层上依次形成低介电常数介质材料层和第一掩膜层,其中,所述第一掩膜层具有第一开口;

9.以所述第一掩膜层为掩膜对所述低介电常数介质材料层执行刻蚀工艺,以使所述第一开口延伸至所述低介电常数介质材料层;

10.在低压环境中对所述第一掩膜层执行第一灰化工艺以去除所述第一掩膜层。

11.可选的,所述低压环境的压力范围为:40mt~100mt。

12.可选的,所述第一灰化工艺的气体包括二氧化碳。

13.可选的,所述二氧化碳的流量大于1000sccm。

14.可选的,所述第一灰化工艺的功率为:200w~500w。

15.可选的,形成所述第一金属层的材料为铜。

16.可选的,在执行所述第一灰化工艺之后,所述方法还包括:继续刻蚀所述低介电常数介质材料层直至所述第一开口延伸至所述金属层顶表面,并形成低介电常数介质层。

17.可选的,在所述衬底上形成第一金属层之后,所述方法还包括在所述第一金属层上形成金属阻挡材料层;

18.以及,在继续刻蚀所述介电常数材料层的同时,所述方法还包括:

19.刻蚀所述金属阻挡材料层以形成金属阻挡层,并使所述第一开口延伸穿过所述金属阻挡层。

20.可选的,在形成所述第一掩膜层之前,所述方法还包括:

21.在所述低介电常数介质材料层上形成第一抗反射材料层;以及,

22.在以所述第一掩膜层为掩膜对所述低介电常数介质材料层执行刻蚀工艺的同时,所述方法还包括:以所述第一掩膜层为掩膜对所述第一抗反射材料层执行刻蚀工艺,以形成第一抗反射层,并使所述第一开口延伸至所述第一抗反射层;

23.以及,在低压环境中对所述第一掩膜层执行第一灰化工艺的同时,所述方法还包括:

24.对所述第一抗反射层执行所述第一灰化工艺,以同时去除所述第一抗反射层。

25.为解决上述问题,本发明还提供一种半导体结构,所述半导体结构根据如上述任意一项所述的半导体结构的制造方法制备而成。

26.本发明的一种半导体结构及制造方法,由于在低压环境中对位于低介电常数介质材料层上的第一掩膜层执行第一灰化工艺以去除第一掩膜层,如此则使得在执行第一灰化工艺时的离子大部分能够沿着垂直于衬底的方向运动,从而减少了离子的横向运动,进而避免了离子横向作用于位于第一开口侧壁的低介电常数介质材料层,进而避免了低介电常数介质材料层的损坏,提升最终制备而成的半导体结构的性能。

附图说明

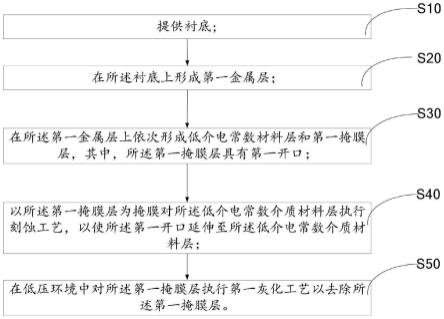

27.图1是本发明一实施例中的半导体结构的制造方法的流程示意图;

28.图2~图7是本发明一实施例中的半导体结构的制造方法的结构示意图;

29.其中,附图标记如下:

30.1-衬底;

31.2-第一介质层;

32.3-第一金属层;

33.4-金属阻挡层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40-金属阻挡材料层;

34.5-低介电常数介质层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

50-低介电常数介质材料层;

35.6-第二介质层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

60-第二介质材料层;

36.7-第二金属层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

70-第二金属材料层;

37.8-第二抗反射层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

80-第二抗反射材料层;

38.9-第二掩膜层;

39.10-第一抗反射层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

100-第一抗反射材料层;

40.11-第一掩膜层;

41.a-第一开口;

42.b-第二开口;

43.c-第三开口;

44.100-沟槽。

具体实施方式

45.以下结合附图和具体实施例对本发明提出的一种半导体结构及其制造方法作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。本发明的核心思想在于,在低压环境中对位于低介电常数介质材料层上的第一掩膜层执行第一灰化工艺以去除第一掩膜层,如此则使得在执行第一灰化工艺时的离子大部分能够沿着垂直于衬底的方向运动,从而减少了离子的横向运动,进而避免了离子横向作用于位于第一开口侧壁的低介电常数介质材料层,进而避免了低介电常数介质材料层的损坏,提升最终制备而成的半导体结构的性能。

46.图1是本发明一实施例中的半导体结构的制造方法的流程示意图;图2~图7是本发明一实施例中的半导体结构的制造方法的结构示意图;下面结合图1~图7说明本实施例中的半导体结构的制造方法,下述半导体结构的制造方法不脱离上述核心思想。

47.在步骤s10中:如图1并结合图2所示,提供衬底1。

48.在本实施例中,所述衬底1可以包括半导体材料、绝缘材料、导体材料或者它们的任意组合,可以为单层结构,也可以包括多层结构。因此,衬底可以是诸如si、sige、sigec、sic、gaas、inas、inp和其它的iii/v或ii/vi化合物半导体的半导体材料。也可以包括诸如,例如si/sige、si/sic、绝缘体上硅(soi)或绝缘体上硅锗的层状衬底。

49.在步骤s20中在所述衬底1上形成第一金属层3。

50.继续参图1并结合图2所示,在本实施例中形成所述金属层3的方法包括:在所述衬底1上形成第一介质层2,所述第一介质层2上具有开槽,在所述开槽内填充金属材料层以形成第一金属层3,其中,形成所述金属层3的材料为铜。

51.在步骤s30中,继续参图1并结合图4所示,在所述第一金属层3上形成低介电常数介质材料层50和第一掩膜层11,其中,所述第一掩膜层11具有第一开口a。在本实施例中,形成所述第一掩膜层11的材料为光刻胶。

52.其中,在本实施例中,在形成所述第一掩膜层11之前,且在形成所述第一金属层3之后,所述方法还包括:在所述第一金属层3上形成金属阻挡材料层40。在本实施例中,形成所述金属材料阻挡层40的材料为:碳化硅材料。其中,所述金属材料阻挡层40的厚度为:

53.继续参图4所示,在本实施例中,在形成所述第一掩膜层11之前所述方法还包括:在所述低介电常数介质材料层50上形成第一抗反射材料层60。

54.参图2~图4所示,在形成低介电常数介质材料层50之后,所述方法还包括:在所述低介电常数介质材料层50上形成第二金属层7。

55.其中,形成第二金属层7的方法包括如下步骤一和步骤二。

56.在步骤一中:参图2所示,在所述低介电常数介质材料层50上依次形成第二介质材料层60、第二金属材料层70和第二掩膜层9,所述第二掩膜层9具有第二开口b。

57.其中,在本实施例中,形成所述第二介质材料层60的材料为四乙氧基硅烷或二氧化硅,形成所述第二金属材料层70的材料为锡,以及形成所述第二掩膜层9的材料为光刻胶。所述第二掩膜层9的厚度为:

58.在步骤二中,继续参图2并结合图3所示,以所述第二掩膜层9为掩膜刻蚀所述第二金属材料层70以形成第二金属层7,并使所述第二开口b延伸至所述第二金属层7以形成第三开口c。此外,在本实施例中,所述第二金属层7的厚度为:继续参图3所示,在本实

施例中,在刻蚀所述第二金属材料层70的同时,还刻蚀部分所述第二介质材料层60,并使所述第三开口c延伸至所述第二介质材料层60。

59.此外,在本实施例中,在形成所述第二掩膜层9之前所述方法还包括:形成第二抗反射材料层80。以及,在刻蚀所述第二金属材料层70的同时,所述方法还包括:以所述第二掩膜层9为掩膜刻蚀所述第二抗反射材料层80以形成第二抗反射层8。在本实施例中,所述第二抗反射层8的厚度为

60.继续参图2和图3所示,在形成所述第二金属层7之后,所述方法还包括:执行第二灰化工艺,以去除所述第二掩膜层9和所述第二抗反射层8。

61.进一步的,继续参图4所示,在去除所述第二掩膜层9和所述第二抗反射层8之后,且在形成所述第一掩膜层11之前,所述方法还包括:在所述第二金属层7上依次形成第一抗反射材料层100和所述第一掩膜层11,所述第一抗反射材料层100填充在所述第三开口c中且形成在所述第二金属层7的上表面上,其中,位于所述第一掩膜层11内的第一开口a的宽度小于所述第三开口c的宽度。

62.在步骤s30中,参图1并结合图4到图6所示,以所述第一掩膜层11为掩膜对所述低介电常数介质材料层50执行刻蚀工艺,并使所述第一开口a延伸至所述低介电常数介质材料层50。

63.在本实施例中,所述刻蚀工艺为干法刻蚀,在可选的实施例中,所述刻蚀工艺也可以为湿法刻蚀。所述刻蚀工艺在此不做具体限定,以实际情况为定。

64.此外,在以所述第一掩膜层11为掩膜刻蚀所述低介电常数介质材料层50的同时,所述方法还包括:刻蚀所述第一抗反射材料层100以形成第一抗反射层10,所述第一开口a同时还延伸至所述第一抗反射层10。此外,由于所述低介电常数介质材料层50上形成有第二介质材料层60,则在刻蚀所述低介电常数介质材料层50的同时,所述方法还包括:刻蚀所述第二介质材料层60,以形成第二介质层6并使所述第一开口a延伸穿过所述第二介质层6。即在以所述第一掩膜层11为掩膜刻刻蚀时,依次刻蚀所述第一抗反射材料层100、第二介质材料层60和低介电常数介质材料层50,以形成所述第一抗反射层10、所述第二介质层6,并使所述第一开口a延伸穿过所述第一抗反射层10、所述第二介质层6并伸入所述低介电常数介质材料层50。

65.在本实施例中,由于所述第一开口a的宽度小于所述第二开口b,因此形成在第一抗反射层10内的第一开口a的宽度小于所述第二开口b,如此则将使得所述第二金属层7和第二介质6的侧壁上形成有所述第一抗反射层10,位于所述第二金属层7和第二介质6的侧壁上的所述第一抗反射层10可用于保护所述第二金属层7和所述第二介质层6的侧壁。

66.在步骤s40中,继续参图5和图6所示,在低压环境中对所述第一掩膜层11执行第一灰化工艺,以去除所述第一掩膜层11。

67.在本实施例中,由于在低压环境中对所述第一掩膜层11执行第一灰化工艺以去除所述第一掩膜层11,如此则使得在执行第一灰化工艺时的离子大部分能够沿着垂直于衬底1的方向运动,从而减少了离子的横向运动,进而避免了离子横向作用于位于第一开口a侧壁的低介电常数介质材料层50,进而避免了低介电常数介质材料层50的损坏,提升最终制备而成的半导体结构的性能。

68.进一步的,在本实施例中,所述低压环境的压力范围为:40mt~100mt。所述第一灰

化工艺的气体包括二氧化碳。其中二氧化碳中的碳在低压条件下,会在位于第一开口a侧壁的低介电常数介质材料层50上形成保护层,同时二氧化碳中的氧原子也在动态去除第一掩膜层11、第一抗反射材料层10以保护层,如此则在动态平衡下,位于第一开口a侧壁的低介电常数介质材料层50还是保持原样,不会遭到损伤。此外,在本实施例中,所述二氧化碳的流量大于1000sccm。进一步的,在本实施例中,所述第一灰化工艺的功率为:200w~500w。由于较低的功率及环境压力进一步降低了刻蚀速度,则相应的横向的刻蚀速度也相应降低,进一步的避免了刻蚀位于第一开口a侧壁的低介电常数介质材料层50。

69.进一步的,继续参图7所示,在本实施例中,在执行所述第一灰化工艺之后,所述方法还包括:继续刻蚀所述低介电常数介质材料层50直至所述第一开口a延伸至所述第一金属层2的顶表面,并形成低介电常数介质层5。其中,在本实施例中,可使用所述第二金属层7作为掩膜层掩膜以继续刻蚀所述低介电常数材料介质层50。继续参图6和图7所示,由于第一开口a的宽度小于第三开口c的宽度,因此位于所述第一开口a侧壁的所述低介电常数材料介质层50和所述第二抗反射层6形成台阶,故在以所述第二金属层7为掩膜刻蚀时,所述台阶被刻蚀,则所述第三开口c延伸至所述低介电常数介质层5。此外,所述第一开口a延伸至所述第一金属层3的顶表面。刻蚀后形成的所述第三开口c和第一开口a构成沟槽100,所述沟槽100用于填充金属材料以形成金属插塞,所述金属插塞连接所述第一金属层3和所述第二金属层7。

70.进一步的,本实施例还公开一种半导体结构,所述半导体结构根据如上述所述的半导体结构的制造方法制备而成。

71.需要说明的是,本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可,此外,各个实施例之间不同的部分也可互相组合使用,本发明对此不作限定。

72.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1