一种充分外露芯片组并联封装体、封装方法及PCB板与流程

一种充分外露芯片组并联封装体、封装方法及pcb板

技术领域

1.本发明涉及半导体封装领域,特别涉及一种充分外露芯片组并联封装体、封装方法及pcb板。

背景技术:

2.传统典型的mosfet功率芯片封装,一般都采用一个封装体中放置单一mosfet功率芯片为封装体型态,而mosfet功率芯片封装过程的关键工序会因为应用的不同,分成数种的封装工艺方法与步骤。比较关键的工序变化,主要是从芯片正面的功能区域引出芯片外的金属引线框内引脚键合的方式,而键合的方式不外乎是纯金属丝键合、金属带加金属丝混合键合、金属片搭配金属锡膏键合加金属丝混合键合以及全金属片搭配金属锡膏键合。

3.上述不同的键合技术其工艺流程与方法也都有所不同,但无论何种键合方式,其基本都存在单一封装体中装置单一mosfet功率芯片为传统的主流封装模式。

4.现有传统单mosfet功率芯片封装体模式存在如下缺陷:

5.1.传统单一功率芯片的封装型式如果应用在更高功率的情况下,则需要特别再开发单一更高功率的mosfet功率芯片再进行单一mosfet功率芯片封装,如此需要增加开发的费用增加生产成本、延长产品开发周期;

6.2.增加更高功率mosfet功率芯片的开发,就会增加不同mosfet功率芯片的库存成本;

7.3.另一种方式就是采用多颗单一mosfet功率芯片封装体,再进行多个低功率的mosfet功率芯片进行并联,并焊接在pcb板(pcb),以增加电流量,如此会增加单一封装体的数量,亦增加了封装体的数量及塑封体的生产成本;

8.4.多颗单一mosfet功率芯片的封装体并联焊接在pcb板(pcb)上的同时,又增加了pcb板的使用面积,如此又增加了pcb板面积的生产成本与库存成本。

9.5.现有mosfet功率芯片的封装体均为通过塑封体将芯片完全包覆,当功率较高时,散热不及时,极易因为由于芯片温度过高而导致损坏。

10.所以上述现有传统的单一mosfet功率芯片,所呈现的缺陷亦是目前业界急待克服与降低成本的趋势,也是目前需要mosfet高功率甚至更高功率加速快充电领域想要降低成本的难点。

技术实现要素:

11.本发明提供一种充分外露芯片组并联封装体,可以解决现有技术中单一芯片封装方式所存在的成本较高、开发周期长、散热效果差的问题。

12.本发明还提供了一种充分外露芯片组并联封装体的封装方法,用于制备上述封装体。

13.本发明还提供了一种pcb板,可以减小线路板面积,降低pcb板生产成本。

14.一种充分外露芯片组并联封装体,包括引线框架、第一塑封体和第二塑封体,还包

括第一芯片组、第二芯片组、第一漏极导电板、第二漏极导电板、第一源极导电板、第二源极导电板、第一栅极导电板和第二栅极导电板;

15.所述第一芯片组包括第一芯片和第二芯片,所述第二芯片组包括第三芯片和第四芯片,所述第二芯片组和所述第一芯片组上下层叠布置;其中,

16.所述第一漏极导电板、所述第二芯片、所述第一源极导电板及所述第一栅极导电板、所述第一芯片和所述引线框架由上至下依次布置,所述第一源极导电板和所述第一栅极导电板均位于所述第一芯片和所述第二芯片之间;

17.所述第一芯片的漏极和所述第二芯片的漏极分别通过基岛和所述第一漏极导电板连接至漏极引脚;所述第一芯片的源极和所述第二芯片的源极均通过所述第一源极导电板连接至源极引脚;所述第一芯片的栅极和所述第二芯片的栅极均通过所述第一栅极导电板连接至栅极引脚;

18.所述第二漏极导电板、所述第四芯片、所述第二源极导电板及所述第二栅极导电板、所述第三芯片和所述第一漏极导电板由上至下依次布置,所述第二源极导电板和所述第二栅极导电板均位于所述第三芯片和所述第四芯片之间;

19.所述第二漏极导电板连接至所述第一漏极导电板;所述第二栅极导电板连接至所述第一栅极导电板;所述第二源极导电板连接至所述第一源极导电板;其中,

20.所述第一芯片组封装在所述第一塑封体内,所述第一漏极导电板外露于所述第一塑封体;

21.所述第二芯片组封装在所述第二塑封体内,所述第二漏极导电板外露于所述第二塑封体。

22.更优地,所述第一漏极导电板朝向所述引线框架的端面与所述第一塑封体远离所述引线框架的端面处于同一平面;所述第二漏极导电板朝向所述引线框架的端面与所述第二塑封体远离所述引线框架的端面处于同一平面。

23.更优地,所述第一源极导电板、所述第二源极导电板、所述第一栅极导电板、所述第二栅极导电板、所述第一漏极导电板和所述第二漏极导电板均由铜或铝制成。

24.更优地,所述第一漏极导电板的一侧延伸设置有第一连接部,所述第一连接部连接至所述引线框架的基岛;所述基岛上开设有第一收纳槽,所述第一收纳槽与所述第一连接部相匹配;

25.所述第二漏极导电板的一侧延伸设置有第二连接部,所述第二连接部连接至所述第一漏极导电板;所述第一漏极导电板上开设有第二收纳槽,所述第二收纳槽与所述第二连接部相匹配。

26.一种充分外露芯片组并联封装体的封装方法,包括如下步骤:

27.s1,在基岛上涂覆可导电性质的粘结物质,使第一芯片的漏极通过粘结物质与所述基岛相连接;

28.s2,在第一芯片的源极区域和栅极区域以及引线框架的源极内引脚和栅极内引脚上涂覆粘结物质;

29.s3,将第一源极导电板通过粘结物质连接第一芯片的源极区域和源极内引脚;将第一栅极导电板通过粘结物质连接第一芯片的栅极区域和栅极内引脚;

30.s4,在第一源极导电板和第一栅极导电板背离所述第一芯片的一侧涂覆粘结物

质,将第二芯片的源极连接至第一源极导电板、栅极安装至第一栅极导电板;

31.s5,在所述第二芯片的漏极涂覆粘结物质,使第一漏极导电板连接基岛和第二芯片的漏极区域;

32.s6,将所述第一芯片组和所述第一源极导电板封装在所述第一塑封体内,并使所述第一漏极导电板外露于所述第一塑封体;

33.s7,在所述第三芯片的漏极涂覆粘结物质,使所述第三芯片的漏极通过粘结物质与所述第一漏极导电板相连接;

34.s8,在第三芯片的源极区域和栅极区域上涂覆粘结物质,将第二源极导电板通过粘结物质连接第三芯片的源极区域和第一源极导电板;将第二栅极导电板通过粘结物质连接第三芯片的栅极区域和第一栅极导电板;

35.s9,在第二源极导电板和第二栅极导电板背离所述第三芯片的一侧涂覆粘结物质,将第四芯片的源极连接至第二源极导电板、栅极安装至第二栅极导电板;

36.s10,在所述第四芯片的漏极涂覆粘结物质,使第二漏极导电板连接第一漏极导电板和第四芯片的漏极;

37.s11,将所述第二芯片组和所述第二源极导电板封装在所述第二塑封体内,并使所述第二漏极导电板外露于所述第二塑封体;

38.s12,切单,得到充分外露芯片组并联封装体。

39.一种pcb板,包括至少一个上述任意一项所述的封装体。

40.本发明提供一种充分外露芯片组并联封装体,至少可以达到如下效果之一:

41.1.可实现相同电压、相同面积的塑封体的情况下,提高电流和/或功率;

42.2.借助芯片同极性并联键合封装结构,可以减少至少一个芯片塑封体的制造成本;

43.3.采用功率芯片同极堆叠键合封装结构,可以减少不同功率芯片的开发、生产及封装体的库存成本。

44.4.通过使第一漏极导电板和第二漏极导电板外露,可以提高散热效率。

45.本发明提供一种充分外露芯片组并联封装体封装方法,工艺流程简单。

46.本发明提供了一种pcb板,可实现同面积的塑封体,减少使用pcb板因为需要增加更高功率而导致使用面积及成本的增加。

附图说明

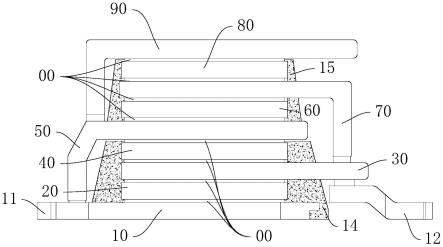

47.图1为本发明提供的一种充分外露芯片组并联封装体的结构示意图一;

48.图2为本发明提供的一种充分外露芯片组并联封装体的结构示意图二;

49.图3为本发明提供的一种充分外露芯片组并联封装体的结构示意图三;

50.图4为本发明提供的一种充分外露芯片组并联封装体的结构示意图四;

51.图5为本发明提供的一种充分外露芯片组并联封装体的结构示意图五;

52.图6为本发明提供的一种充分外露芯片组并联封装体的结构示意图六;

53.图7为本发明提供的一种充分外露芯片组并联封装体的剖面结构示意图。

54.附图标记说明:

55.00粘结物质;10基岛;11漏极引脚;12源极引脚;13栅极引脚;14第一塑封体;15第

二塑封体;20第一芯片;30第一源极导电板;31第一栅极导电板;40第二芯片;50第一漏极导电板;60第三芯片;70第二源极导电板;71第二栅极导电板;80第四芯片;90第二漏极导电板。

具体实施方式

56.下面结合附图,对本发明的一个具体实施方式进行详细描述,但应当理解本发明的保护范围并不受具体实施方式的限制。

57.实施例一:

58.如图1至图7所示,本发明实施例提供的一种充分外露芯片组并联封装体,包括引线框架、第一塑封体14、第二塑封体15、第一芯片组、第二芯片组、第一漏极导电板50、第二漏极导电板90、第一源极导电板30、第二源极导电板70、第一栅极导电板31和第二栅极导电板71,第一芯片组和第二芯片组层叠布置。

59.第一芯片组包括第一芯片20和第二芯片40,第一芯片20的漏极和第二芯片40的漏极相背布置并键合至漏极引脚11;第一芯片20的源极和第二芯片40的源极相对布置并键合至源极引脚12;第一芯片20的栅极和第二芯片40的栅极相对布置并键合至栅极引脚13;第二芯片组包括第三芯片60和第四芯片80,第三芯片60的漏极和第四芯片80的漏极相背布置并键合至漏极引脚11;第三芯片60的源极和第四芯片80的源极相对布置并键合至源极引脚12;第三芯片60的栅极和第四芯片80的栅极相对布置并键合至栅极引脚13。

60.本实施例中,以第一芯片20、第二芯片40、第三芯片60和第四芯片80均为mosfet功率芯片为例进行说明。

61.如图1和图2所示,其展示了第一芯片组的结构示意图,如图5,展示了整体内部结构示意图(第一芯片组和第二芯片组)。如图7所示,第二漏极导电板90、第四芯片80、第二源极导电板70及第二栅极导电板71、第三芯片60、第一漏极导电板50、第二芯片40、第一源极导电板30及第一栅极导电板31、第一芯片20和引线框架由上至下依次布置,第一源极导电板30和第一栅极导电板31均位于第一芯片20和第二芯片40之间,第一源极导电板30和第一栅极导电板31位于同一水平面上,第二源极导电板70和第二栅极导电板71均位于第三芯片60和第四芯片80之间,第二源极导电板70和第二栅极导电板71位于同一水平面上。

62.具体的,如图1所示,第一芯片20的漏极涂覆有粘结物质00,粘结物质00可选用金属锡膏、导电银胶或其他可导电性质的粘结物质00。第一芯片20的漏极通过粘结物质00连接至基岛10,与基岛10电性导通;第一芯片20上方设置有第一源极导电板30和第一栅极导电板31,第一源极导电板30和第一栅极导电板31上均涂覆有粘结物质00,第一源极导电板30的一侧面通过粘结物质00连通第一芯片20的源极和源极引脚12,而第一栅极导电板31则通过粘结物质00连通第一芯片20的栅极和栅极引脚13;第二芯片40位于第一源极导电板30和第一栅极导电板31上方,第二芯片40的栅极和源极涂覆有粘结物质00并连通至第一栅极导电板31和第一源极导电板30;第一漏极导电板50位于第二芯片40的上方,第一漏极导电板50通过粘结物质00连通漏极引脚11和第二芯片40的漏极;如图3所示,第一漏极导电板50背离第二芯片40的一侧涂覆有粘结物质00,第三芯片60的漏极通过粘结物质00连通至第一漏极导电板50,第三芯片60的上方设置有第二源极导电板70和第二栅极导电板71,第二源极导电板70和第二栅极导电板71上均涂覆有粘结物质00,第二源极导电板70的一侧面通过

粘结物质00连通第三芯片60的源极和源极引脚12,而第二栅极导电板71则通过粘结物质00连通第三芯片60的栅极和栅极引脚13;如图4所示,第四芯片80位于第二源极导电板70和第二栅极导电板71上方,第四芯片80的栅极和源极涂覆有粘结物质00并分别连通至第二栅极导电板71和第二源极导电板70;如图7所示,第二漏极导电板90位于第四芯片80的上方,第二漏极导电板90通过粘结物质00连通漏极引脚11和第四芯片80的漏极。

63.其中,如图7所示,第一芯片组封装在第一塑封体14内,第一漏极导电板50外露于第一塑封体14,第一源极导电板30部分或全部封装在第一塑封体14内(图7中仅展示了第一源极导电板30部分封装在第一塑封体内的情况),第二芯片组封装在第二塑封体15内,第二漏极导电板90外露于第二塑封体15,第二源极导电板70部分或全部封装在第二塑封体15内(图7中仅展示了第二源极导电板70部分封装在第二塑封体内的情况),以提高散热效率。

64.具体的,第一源极导电板30、第二源极导电板70、第一栅极导电板31、第二栅极导电板71、第一漏极导电板50和第二漏极导电板90由铜或铝制成。

65.由于mosfet功率芯片的源极采用导电板与源极引脚12相连,栅极导电板与栅极引脚13相连,漏极导电板与漏极引脚11和/或基岛10连接,这样,相对于现有的金属丝键合,具有更小的导通电阻,另外,导电板相较于金属丝键合,具有更大的容积,可以提高吸热能力,进而改善运行时的瞬时温度波动。

66.在实际生产的过程中,一个芯片处于正装,一个芯片处于倒装;两者的方向对称,因此,主要可以分成三种情况,下面以第一芯片组为例介绍设置芯片的形式:

67.(1)第一种形式,第一芯片20和第二芯片40的规格相同,栅极区域处于芯片中心线的区域,并相对中心线对称,这样,在封装时,可以使得第一芯片20的栅极和第二芯片40栅极直接相对;

68.(2)第二种形式,第一芯片20和第二芯片40的规格相同,但是,两个芯片的栅极,均处于同一侧的拐角部位,这样,在一个芯片正装和一个芯片倒装时,可以延长栅极导电板的长度,使得栅极导电板与两个芯片的栅极同时相连;

69.(3)第三种形式,第一芯片20和第二芯片40的规格不同,一个芯片的栅极处于一侧拐角,另一个芯片的栅极处于另一个拐角,这样,两个芯片封装时,同样可以使得第一芯片20的栅极和第二芯片40的栅极处于正好相对的部位。

70.需要说明的是:上述三种形式,是比较容易实现芯片并联形式,在双mosfet功率芯片进行并联时,mosfet功率芯片也可采用其他的形式,通过改变漏极导电板和栅极导电板的形状,和/或改变源极内引脚和栅极内引脚的位置和形状,对mosfet功率芯片进行适配,实现mosfet功率芯片并联过程。可以理解的是,第二芯片组的结构形式与第一芯片组类似,不再赘述。

71.可以理解的是,基岛10本身也可以起到第二漏极导电板90相同的功能。

72.实施例二:

73.在实施例一的基础上,第一漏极导电板50的一侧向下延伸设置有第一连接部,第一连接部连接至引线框架的基岛10;基岛10上开设有第一收纳槽,第一收纳槽与第一连接部相匹配。

74.第二漏极导电板90的一侧向下延伸设置有第二连接部,第二连接部连接至第一漏极导电板50;第一漏极导电板50上开设有第二收纳槽,第二收纳槽与第二连接部相匹配。

75.通过第一收纳槽和第一连接部以及第二收纳槽和第二连接部的配合,使得第一漏极导电板50的第一连接部可贴装入第一收纳槽中,第二漏极导电板90的第二连接部可贴装入第二收纳槽中,并利用可导电的粘结物质00进行连接,这样,在安装第一漏极导电板50和第二漏极导电板90时,即可对第一漏极导电板50和第二漏极导电板90进行限位,这样,可以达到更加精准的对位,且封装时,可改善因可导电的粘结物质00流动所导致的第一漏极导电板50和/或第二漏极导电板90偏转、旋转或翘曲的问题。

76.实施例三:

77.一种充分外露芯片组并联封装体的封装方法,包括如下步骤:

78.s1,在基岛10上涂覆可导电性质的粘结物质00,使第一芯片20的漏极通过粘结物质00与所述基岛10相连接;

79.s2,在第一芯片20的源极区域和栅极区域以及引线框架的源极内引脚和栅极内引脚上涂覆粘结物质00;

80.s3,将第一源极导电板30通过粘结物质00连接第一芯片20的源极区域和源极内引脚;将第一栅极导电板31通过粘结物质00连接第一芯片20的栅极区域和栅极内引脚;

81.s4,在第一源极导电板30和第一栅极导电板31背离所述第一芯片20的一侧涂覆粘结物质00,将第二芯片40的源极连接至第一源极导电板30、栅极安装至第一栅极导电板31;

82.s5,在所述第二芯片40的漏极涂覆粘结物质00,使第一漏极导电板50连接基岛10和第二芯片40的漏极区域;

83.s6,将所述第一芯片组和所述第一源极导电板30封装在所述第一塑封体14内,并使所述第一漏极导电板50外露于所述第一塑封体14;

84.s7,在所述第三芯片60的漏极涂覆粘结物质00,使所述第三芯片60的漏极通过粘结物质00与所述第一漏极导电板50相连接;

85.s8,在第三芯片60的源极区域和栅极区域上涂覆粘结物质00,将第二源极导电板70通过粘结物质00连接第三芯片60的源极区域和第一源极导电板30;将第二栅极导电板71通过粘结物质00连接第三芯片60的栅极区域和第一栅极导电板31;

86.s9,在第二源极导电板70和第二栅极导电板71背离所述第三芯片60的一侧涂覆粘结物质00,将第四芯片80的源极连接至第二源极导电板70、栅极安装至第二栅极导电板71;

87.s10,在所述第四芯片80的漏极涂覆粘结物质00,使第二漏极导电板90连接第一漏极导电板50和第四芯片80的漏极;

88.s11,将所述第二芯片组和所述第二源极导电板70封装在所述第二塑封体15内,并使所述第二漏极导电板90外露于所述第二塑封体15;

89.s12,切单,得到充分外露芯片组并联封装体。

90.需要说明的是,塑封完成后,处于第一塑封体14和第二塑封体15内侧部分的引脚称为内引脚,反之则为外引脚。

91.通过此种封装方式,两组mosfet功率芯片共享同极性的源极、漏极和栅极的导电板,实现两组mosfet功率芯片的并联,其中每组mosfet功率芯片中的两个mosfet功率芯片共享同极性的源极、漏极和栅极的导电板,实现单组内的两个mosfet功率芯片的并联。

92.实施例四:

93.一种pcb板,包括至少一个上述的封装体,具体封装体的数量根据pcb板的设计确

定。在封装过程中,即完成内埋芯片组并联封装体,当应用需要更高功率更高电流需求的时候,pcb板上只要安装焊接一个内埋芯片组并联封装体,即可避免了pcb板上,贴装更多个单颗mosfet功率芯片的封装体,除了可以节省pcb板所需要占用的面积成本之外,还可以减少mosfet功率芯片封装体的使用与生产成本。

94.以上公开的仅为本发明的几个具体实施例,但是,本发明实施例并非局限于此,任何本领域的技术人员能思之的变化都应落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1