带缓冲漏极的晶体管器件的制作方法

带缓冲漏极的晶体管器件

背景技术:

1.半导体器件(诸如硅器件)具有广泛的应用。例如,横向扩散金属氧化 物半导体(ldmos)或漏极扩展功率晶体管被用于许多应用,诸如开关直流 (dc)-dc转换器和其它应用。

技术实现要素:

2.本公开的各种公开的方法和器件可以有益地应用于开关dc-dc转换器和 需要耐用性以使器件能够在负载瞬态、短路电流、负电流流动和其它异常情 况期间幸存的其它应用。虽然可以预期此类实施例提供性能上的改进(诸如 改进的安全操作区(soa)和耐用性,同时保留或甚至降低了比导通电阻), 但除非在特定的权利要求中明确记载,否则特定的结果都不是本发明的要求。

3.在本公开的一个方面中,一种半导体器件包括在半导体衬底中的源极区 域。漏极区域与源极区域间隔开,具有第一导电类型和第二掺杂剂浓度。第 一漂移区域位于源极区域和漏极区域之间,并且具有第一导电类型和低于漏 极区域的第二掺杂剂浓度的第一掺杂剂浓度。沟道区域在源极区域和第一漂 移区域之间,具有不同的第二导电类型。氧化物结构在沟道区域和漏极区域 之间并且包括在第一漂移区域上或上方的第一部分以及在第一部分和漏极区 域之间的锥形部分。衬底表面延伸部在锥形部分和漏极区域之间。栅极结构 在氧化物结构上或上方并且包括在沟道区域上方的部分。缓冲区域在第一漂 移区域和漏极区域之间并且在氧化物结构的锥形部分下方,具有第一导电类 型。缓冲区域具有在漏极区域的第二掺杂剂浓度和第一漂移区域的第一掺杂 剂浓度之间的第三掺杂剂浓度。

4.在本公开的另一方面中,一种半导体器件包括在半导体衬底中的n型源 极区域。n型漏极区域与源极区域间隔开,具有第一掺杂剂浓度。n型漂移区 域位于源极区域和漏极区域之间并且具有低于第一掺杂剂浓度的第二掺杂剂 浓度。p型沟道区域在源极区域和漂移区域之间。locos结构在沟道区域和 漏极区域之间,包括在漂移区域上或上方的第一部分以及在第一部分和漏极 区域之间的锥形部分。衬底表面延伸部在锥形部分和n型漏极区域之间。栅 极结构在氧化物结构上或上方并且包括在沟道区域上方的部分。缓冲区域在 漂移区域和漏极区域之间,并且在氧化物结构的锥形部分下方。缓冲区域具 有的掺杂剂浓度从漂移区域向漏极区域增加不超过9倍。

5.在另一方面,一种形成半导体器件的方法包括形成硅局部氧化(locos) 结构。locos结构包括第一部分和锥形部分。通过使用第一注入通过图案化 抗蚀剂层中的开口形成具有第一掺杂剂浓度的漂移区域。通过使用第二注入 通过图案化抗蚀剂层中的开口同时形成缓冲区域和漂移过渡区域。第二注入 具有低于第一注入的注入能量,并且第二注入的掺杂剂穿透锥形部分以形成 缓冲区域。在沟道区域上或上方形成栅极结构。形成源极区域。形成具有第 二掺杂剂浓度的漏极区域,第二掺杂剂浓度高于漂移区域的第一掺杂剂浓度。 缓冲区域的第三掺杂剂浓度介于漂移区域的第一掺杂剂浓度和漏极区域的第 二掺杂剂浓度之间。锥形部分在locos结构的第一部分和漏极区域之间。

附图说明

6.对于各种示例的详细描述,现在将参考附图,其中:

7.图1图示了基线半导体器件的一部分;

8.图2图示了本公开的示例半导体器件的一部分;

9.图3a图示了基线半导体器件的部分俯视图;

10.图3b图示了图3a的基线半导体器件的截面图;

11.图4a图示了另一示例半导体器件的部分俯视图;

12.图4b图示了图4a的半导体器件的截面图;

13.图5图示了图1的基线半导体器件的沿着从漂移区域到漏极区域的方向 的掺杂剂浓度;

14.图6图示了图2的示例半导体器件的沿着从漂移区域到漏极区域的方向 的掺杂剂浓度;

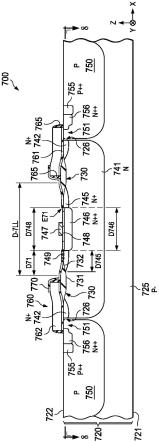

15.图7图示了根据所描述的示例的另一示例半导体器件的截面图;

16.图8图示了图7的半导体器件的另一示例截面图;

17.图9图示了基线半导体器件的电流-电压特性;

18.图10图示了示例半导体器件的电流-电压特性;

19.图11图示了示例半导体器件与基线半导体器件相比的比导通电阻 (specific on-resistance);

20.图12图示了示例半导体器件与基线半导体器件相比的回弹(snapback) 电流-电压特性;以及

21.图13至图22图示了形成图7的示例半导体器件的各个阶段的示例结构 的截面图。

具体实施方式

22.横向扩散金属氧化物半导体(ldmos)或漏极扩展功率晶体管用于开关 dc-dc转换器和需要耐用性以使器件能够在负载瞬态、短路电流、负电流流 动和其它异常情况期间幸存的其它应用。此外,需要维持低的比导通电阻 (rsp)以最小化成本,因为在给定漏源导通电阻(rds-on)下rsp决定了管 芯尺寸。对于先进的低rsp ldmos或漏极扩展晶体管架构,通常难以维持良 好的耐用性,例如,在漏极经历雪崩击穿的瞬态事件期间的器件幸存率。

23.本公开涉及具有改进的安全操作区(soa)和耐用性同时具有保留或甚 至降低的比导通电阻的半导体器件(例如,ldmos或漏极扩展晶体管器件)。 此类半导体器件可以有益地被采用于开关dc-dc转换器和需要耐用性以使器 件能够在负载瞬态、短路电流、负电流流动和其它异常情况期间幸存的其它 应用中。尽管可以预期此类实施例提供相对于常规ldmos或漏极扩展晶体 管器件的改进,但除非在特定的权利要求中明确记载,否则特定的结果都不 是本发明的要求。

24.所描述的示例包括一种半导体器件,其具有第一漂移区域、漏极区域和 硅局部氧化(locos)结构,该locos结构包括主要部分和逐渐变细并保 留在主要部分和漏极区域之间的锥形(tapered)部分(有时称为“鸟喙部”)。 保留的锥形部分可以用作筛选(screening)氧化物部分以允许浅注入(例如, 低能量注入)的掺杂剂穿透其中以形成在第一漂移区域和漏极区域之间的缓 冲区域,并且因此形成从轻掺杂的第一漂移区域到重掺

杂的漏极区域的平滑 掺杂浓度过渡。

25.图1图示了基线半导体器件100的一部分;并且图2图示了本公开的示 例半导体器件200的一部分。基线半导体器件100包括漏极区域146、在漏极 区域146上或上方的硅化物接触件148、第一漂移区域141、管体区域150、 源极区域157和locos结构130。示例半导体器件200包括漏极区域246、 在漏极区域246上或上方的硅化物接触件248、第一漂移区域241、管体区域 250、源极区域257、locos结构230和缓冲区域245。

26.locos结构130包括主要部分131和逐渐变细的锥形部分132。然而, 在基线半导体器件100的主要部分131和漏极区域146之间或在主要部分131 和硅化物接触件148之间,存在可忽略的或短的锥形部分132,或者可能没有 锥形部分。这是因为与硅化物接触件148重叠的锥形部分在基线半导体器件 100的形成期间可能被蚀刻掉。相比之下,在本公开的半导体器件200(例如, ldmos器件或漏极扩展晶体管)中,通过增加在locos结构230和硅化物 接触件248的相应边缘e21之间的距离,在locos结构230的主要部分231 和漏极区域246之间(或在locos结构230的主要部分231和硅化物接触件 248之间)保留了锥形部分232。如图1和图2所示,在locos结构230的 主要部分231和硅化物接触件248的边缘e21之间的距离d21大于在locos 结构130的主要部分131和硅化物接触件148的边缘e11之间的距离d11。

27.在示例器件200中,保留在locos结构230的主要部分231和漏极区域 246之间(或在locos结构230的主要部分231和硅化物接触件248的边缘 e21之间)的锥形部分232可以用作筛选氧化物部分,以允许浅注入(例如, 相对低能量注入)的掺杂剂穿透其中以在第一漂移区域241和漏极区域246 之间形成缓冲区域245,而由于在locos结构130的主要部分131和漏极区 域146之间没有锥形部分或有可忽略的或短的锥形部分,因此在基线器件100 中的第一漂移区域141和漏极区域146之间没有形成缓冲区域。示例器件200 还包括“衬底表面延伸部”249(或层表面延伸部)。如本文所用,“衬底表面 延伸部”(例如,249)被定义为在locos结构(例如,230)和漏极区域(例 如,246)之间的衬底表面(或层表面)的未被locos结构(例如,230)的 任何部分覆盖的部分,其中“衬底”包括被处理以包括器件200的部件的半 导体的部分,例如硅晶圆上的外延层。衬底表面延伸部249(连同相应保留的 锥形部分232)可以允许浅注入(例如,相对低能量的注入)的掺杂剂穿透其 中以形成在第一漂移区域241和漏极区域246之间的缓冲区域。

28.可以选择浅注入(例如,相对低能量的注入)的注入能量,使得locos 结构230的主要部分231可以阻挡浅注入(例如,相对低能量的注入)的掺 杂剂,但锥形部分232可以允许浅注入(例如,相对低能量的注入)的掺杂 剂穿透其中,其中浅注入相对于用于形成第一漂移区域241的深(或较深) 注入来说是浅的。

29.在一些示例中,locos结构230的主要部分231具有的厚度为30nm至200nm,并且浅注入(例如,相对低能量的注入)的注入能量对于磷掺杂剂小 于50kev,并且对于砷掺杂剂小于100kev,并且对于锑掺杂剂小于200kev。 浅注入(例如,相对低能量的注入)的注入能量可以根据locos结构230的 主要部分231的厚度来选择。例如,在locos结构230的主要部分231的厚 度较大的情况下,可以增加浅注入的注入能量。

30.在本发明的半导体器件200(例如,ldmos器件或漏极扩展晶体管)中, 经由增加在locos结构230和硅化物接触件248的边缘e21之间的距离,并 保留在locos结构230的主要部分231和漏极区域246之间的锥形部分232, 可以在没有附加光致抗蚀剂掩模或注入的情

况下形成在第一漂移区域241和 漏极区域246之间的具有改进安全操作区(soa)和耐用性的掺杂分布的缓 冲区域245,并且因此可以降低制造成本。

31.图3a图示了基线半导体器件300的部分俯视图;并且图3b图示了图3a 的包括ldmos晶体管的基线半导体器件300的截面图。基线半导体器件300 包括源极区域356、具有沟道区域351的管体区域350、漏极区域346、在漏 极区域346上或上方的硅化物接触件348、在硅化物接触件348上或上方的一 个或多个钨接触件347、在漏极区域346和沟道区域351之间的第一漂移区域 341以及管体接触区域355。半导体器件300还包括在第一漂移区域341上或 上方的locos结构330。locos结构330包括主要部分331。locos结构 330可以包括在主要部分331和漏极区域346之间的截头锥形部分332,截头 锥形部分332是由在器件的漏极侧上充分去除了locos结构330的鸟喙部例 如以降低器件的rds-on而导致的。器件300还包括在沟道侧的locos结构 330的鸟喙部下方的掺杂区域343。此特征在下面更全面地描述。基线半导体 器件300还包括至少部分在沟道区域351上方或上的栅极结构360,以及保护 层370(诸如硅化物阻挡保护层)。

32.现在参考图4a和图4b,图4a图示了本公开的包括ldmos晶体管的示 例半导体器件400的部分俯视图;并且图4b图示了图4a的半导体器件400 的截面图。半导体器件400包括源极区域456、具有沟道区域451的管体区域 450、管体接触区域455、漏极区域446以及在漏极区域446和沟道区域451 之间的第一漂移区域441。半导体器件400还包括在第一漂移区域441上或上 方的locos结构430、掺杂区域443和缓冲区域445。locos结构430包括 主要部分431和在主要部分431和漏极区域446之间的锥形部分432。与基线 器件300不同,锥形部分432没有被截断,基本上留下了locos鸟喙部的全 长并且增加了沟道到漏极间距。半导体器件400还包括至少部分地在沟道区 域451上方或上的栅极结构460,以及保护层470(诸如硅化物阻挡保护层), 该保护层470在使脱釉(deglazing)和其它操作期间减轻或防止locos结构 430和缓冲区域445的硅化,并防止栅极到漏极的短路。

33.图4b的一个或多个相应locos结构430的主要部分431对应于在 locos工艺期间使用的图案化掩模的相应开口(也参见图13和图14)。例如, 主要部分431沿标记的x轴的宽度对应于图案化掩模的相应开口的宽度。此 外,在locos工艺期间,可以在下面的半导体层和上面的掩模之间发生氧的 扩散,并且因此形成锥形部分432(即,鸟喙部)并延伸超出图案化掩模的相 应开口的宽度。与基线器件300的locos到locos距离d-3ll相比,器件 400的locos到locos(ltl)距离d-4ll增加。locos到locos距离 (例如,d-4ll或d-3ll)是一个或多个相应locos结构(例如430、330) 的主要部分(例如431、331)之间的距离。例如,与基线器件300中的一个 或多个相应locos结构330的主要部分331相比,器件400中的一个或多个 相应locos结构430的主要部分431布置得分开更远。此外,与漏极区域 346的宽度d346相比,器件400的漏极区域446的宽度d446可以被减小; 并且与硅化物接触件348的宽度d348相比,器件400的硅化物接触件448的 宽度d448可以被减小。在器件400的ltl距离d-4ll增加并且硅化物接触 件448的宽度d448减小的情况下,与基线器件300的在locos结构330的 主要部分331和硅化物接触件348的边缘e31之间的距离d31相比,在locos 结构430的主要部分431和硅化物接触件448的边缘e41之间的距离d41被 增加。

34.此外,在locos结构430的主要部分431和硅化物接触件448的边缘 e41之间的距离d41增加的情况下,在locos结构430的主要部分431和漏 极区域446之间保留了锥形部分

432。保留的锥形部分432可以用作筛选氧化 物部分以允许浅注入(例如,低能量注入)的掺杂剂穿透其中以形成从第一 漂移区域441(例如,在栅极结构460下方和在主要部分431下方)到重掺杂 的漏极区域446的平滑掺杂浓度过渡(例如,参见图6)。相比之下,基线器 件(例如,100、300)在高电场下具有陡峭掺杂浓度过渡(例如,参见图5)。

35.保留的锥形部分432可以用作筛选氧化物部分以允许浅注入(例如,低 能量注入)的掺杂剂穿透其中以在第一漂移区域441和漏极区域446之间形 成缓冲区域445。示例器件400还包括“衬底表面延伸部”449(或层表面延 伸部)。衬底表面延伸部449被定义为在locos结构430和漏极区域446之 间的衬底表面(或层表面)的未被locos结构430的任何部分覆盖的部分。 衬底表面延伸部449(和相应且相邻的保留的锥形部分432)可以允许浅注入 (例如,低能量注入)的掺杂剂穿透其中以在第一漂移区域441和漏极区域 446之间形成缓冲区域445。由于在从locos结构430朝向漏极区域446的 方向上锥形部分432的厚度逐渐减小,因此相应缓冲区域445的掺杂剂浓度 逐渐且平滑地增加(例如,参见图6的椭圆区域)。相比之下,在基线器件300 中,由于在locos结构330的主要部分331和漏极区域346之间具有可忽略 或短的锥形部分或者没有锥形部分,因此在第一漂移区域341和漏极区域346 之间没有形成缓冲区域。相应地,基线器件(例如,100、300)在高电场下 具有陡峭掺杂浓度过渡(参见例如图5)。

36.在沟道端处在locos结构430下方的掺杂区域443(类似于基线器件300 的掺杂区域343)起到与缓冲区域445非常不同的作用,并且因此缓冲区域 445是重要且非显而易见的改进。掺杂区域443降低了rds-on和成本品质因 数rsp(其是rds-on乘以ldmos晶体管的半间距)。受益于掺杂区域443 的存在的器件400的部分有时被称为jfet区域。jfet区域是漂移区域中的 将栅极结构430下方的沟道区域451的反型层连接到locos结构430下方的 n掺杂漂移区域441的部分。由掺杂区域443提供的额外n型掺杂提供静电筛 选以减轻否则可能由从沟道区域451到漂移区域441的热载流子注入引起的 损坏。这是因为在器件400在高电压下操作的实施方式中,在热载流子应力 下的器件老化的早期迹象是漂移区域电阻下的增加。掺杂区域443的增加的 掺杂“推出(pushes out)”了该电阻增加的开始(onset),从而能够改进器件 可靠性。

37.相比之下,由缓冲区域445提供的额外掺杂在改进器件400的可靠性或 器件的“耐用性”方面提供了不相关的作用。更具体地,在漏极反向偏置下, n型漂移区域掺杂在locos结构430下方的整个区域耗尽,有时称为resurf 效应。然而,当耗尽边缘遇到衬底表面延伸部449的额外n型掺杂时,掺杂 太强而无法耗尽,并且发生雪崩。这设置器件的击穿电压bvdss。请注意, bvdss与耗尽的距离成比例,因此它反映了locos 431的长度,但不反映 衬底表面延伸部449。在高注入条件下,漂移区域的高场部分可以一直延伸到 漏极区域446。这有效地增加了高注入期间的漂移长度。在强注入条件下的击 穿称为回弹,并且在此类器件中通常是破坏性的。如果栅极电压大于零并且 一些沟道电流流动,并且漏极被击穿,则这将雪崩和来自沟道的电流注入的 影响结合。耐用的ldmos器件是其回弹故障电压充分高于bvdss的ldmos 器件,因为这种关系保证了ldmos在经历bvdss之后,它可以在经历破坏 性回弹故障之前幸免于一范围电压的雪崩。这种雪崩行为允许ldmos在某 一程度上保护自己免受不利的高功率事件,诸如电容性静电放电、电感性负 载突降或反激等。缓冲区域445的这种存在以与由掺杂区域443提供的任何 效应不相关的方式提供了此类改进的耐用性,

并且因此增加器件的soa。

38.图5图示了基线半导体器件(例如图1的基线器件100)的沿着从第一漂 移区域到漏极区域的方向的掺杂剂浓度;并且图6图示了示例半导体器件(例 如图2的示例器件200)的沿着从第一漂移区域到漏极区域的方向的掺杂剂浓 度。参考图1和图5,沿着从图1的基线半导体器件100的第一漂移区域到漏 极区域(例如,沿着图1中的虚线l11)的+x方向,磷掺杂剂浓度在以第一 掺杂剂浓度处轻掺杂的第一漂移区域141中是均匀的,并且陡峭地改变为在 重掺杂的漏极区域146中的第二掺杂剂浓度。在一个示例中,陡峭改变是在 100nm的横向距离上超过一个数量级的增加。相比之下,参考图2和图6,沿 着从图2的半导体器件200的第一漂移区域到漏极区域(例如沿着图2中的 虚线l21)的+x方向,磷掺杂剂浓度从轻掺杂的第一漂移区域241中的第一 掺杂剂浓度增加到中间掺杂的添加的缓冲区域245中的逐渐增加的第三掺杂 剂浓度(参见椭圆区域),然后陡峭地增加到重掺杂的漏极区域246中的第二 掺杂剂浓度。由添加的缓冲区域245引入的第三掺杂剂浓度高于第一漂移区 域241中的第一掺杂剂浓度并且低于重掺杂的漏极区域246中的第二掺杂剂 浓度,并且平滑且逐渐地增加。在各种示例中,逐渐改变提供了在300nm的 横向距离上缓冲区域245中的掺杂剂浓度增加至少0.5倍且不超过9倍。在一 些示例中,掺杂剂浓度的增加在从大约1倍到大约4倍的范围内。在另一示 例中,掺杂剂浓度在缓冲区域245内的300nm的距离上增加至少50%并且不 超过400%。在图6的示例中,例如,在大约200nm的距离内,磷浓度从椭圆 左侧的第一浓度到椭圆内的第二浓度增加大约1倍,并且保持在第二浓度达 大约100nm的距离,然后陡峭增加。因此,在示例器件(诸如图2的示例半 导体器件200)中的从第一漂移区域到漏极区域的掺杂浓度过渡比基线器件 (例如图1的基线器件100)更平滑。预计由锥形部分232提供的掺杂剂浓度 的更平滑过渡降低漂移区域241和漏极246之间的电场梯度,并且这种降低 的梯度将减少漏极附近电荷载流子的碰撞电离,从而增加soa。

39.图7图示了根据所描述的示例的另一示例半导体器件700的截面图。图8 图示了半导体器件700在图7中指示的水平下的另一示例截面图。半导体器 件700(诸如ldmos器件或漏极扩展晶体管)包括半导体层720,其包括半 导管体区域725、埋在半导体层720中的第一漂移区域741、漂移过渡区域742、 locos结构730、缓冲区域745、漏极区域746、漏极区域746上或上方的硅 化物接触件748、硅化物接触件748上或上方的钨接触件747、包括沟道区域 751的管体区域750、与管体区域接触的管体接触区域755,以及源极区域。 半导体器件700还包括一个或多个栅极结构760,每个栅极结构760包括栅极 介电层761和栅电极762、侧壁间隔件765和siblk 770。缓冲区域(诸如745) 和漂移过渡区域(诸如742)可以操作为或用作第二漂移区域。第二漂移区域 (诸如缓冲区域745和漂移过渡区域742)和第一漂移区域(诸如741)可以 形成或操作为将沟道区域(诸如751)耦合到漏极区域(诸如746)的漂移区 域。

40.半导体层720具有第一表面721和相反的第二表面722。图7还图示了具 有x、y和z轴的坐标系。x轴和y轴彼此正交并且平行于半导体层720的 平面,例如半导体层720的第一表面721。因此,x轴和y轴被称为“面内 方向”。z轴垂直于x轴和y轴并且因此垂直于半导体层720的平面。因此, z轴被称为“面外方向”。

41.在一些示例中,半导体层720的材料包括掺杂硅(诸如p型硅),并且以 p-掺杂剂浓度(例如轻掺杂)掺杂。在其它示例中,半导体层720的材料可以 包括硅、锗、砷化镓和/或任

何其它合适的半导体。p型半导体是多数载流子 为空穴的半导体,并且n型半导体是多数载流子为电子的半导体。

42.p型半导体的掺杂剂浓度可以是在3

×

10

16

cm-3

至3

×

10

18

cm-3

范围内的p 掺杂剂浓度、在1

×

10

19

cm-3

至1

×

10

22

cm-3

范围内的p+掺杂剂浓度,或任何 其它合适的p型掺杂剂浓度。n型半导体的掺杂剂浓度可以是在3

×

10

15

cm-3

至1

×

10

18

cm-3

范围内的n掺杂剂浓度、是n掺杂剂浓度的近似2至10倍高 的n+掺杂剂浓度、在1

×

10

19

cm-3

至1

×

10

22

cm-3

范围内的n++掺杂剂浓度, 或任何其它合适的n型掺杂剂浓度。半导体的类型可以是n型、与n型相反 的p型或未掺杂的半导体。

43.locos结构730包括主要部分731和逐渐变细的锥形部分732。主要部 分731和漏极区域746之间的锥形部分732的厚度在从主要部分731下方的 第一漂移区域741指向漏极区域746的方向上逐渐减小。与基线器件300的 locos到locos距离d-3ll相比,器件700的locos到locos距离d-7ll 被增加。locos到locos距离d-7ll是在locos结构730的主要部分731 之间的距离。与基线器件300中的locos结构330的主要部分331相比,器 件700中的locos结构730的主要部分731布置得分开更远。此外,与基线 器件中的漏极区域的宽度(例如,基线器件300的漏极区域346的宽度d346) 相比,器件700的漏极区域746的宽度d746可以被减小;并且与基线器件中 的硅化物接触件的宽度(例如,基线器件300的硅化物接触件348的宽度d348) 相比,器件700的硅化物接触件748的宽度d748可以被减小。在示例器件 700中的locos到locos距离d-7ll增加和/或硅化物接触件748的宽度 d748减小的情况下,与例如locos结构330的主要部分331和基线器件300 的硅化物接触件348的边缘e31之间的距离d31相比,locos结构730的主 要部分731和硅化物接触件748的边缘e71之间的距离d71被增加。

44.在本公开中,在locos结构730的主要部分731和硅化物接触件748的 边缘e71之间的距离d71增加的情况下,在locos结构730的主要部分731 和漏极区域746之间保留了锥形部分432。保留的锥形部分732可以用作筛选 氧化物部分,以允许浅注入(例如,低能量注入)的掺杂剂穿透其中以形成 从第一漂移区域741(例如,在栅极结构760下方和主要部分731下方)到重 掺杂的漏极区域746平滑掺杂浓度过渡。相比之下,基线器件(例如,100、 300)在高电场下具有陡峭掺杂浓度过渡。

45.保留的锥形部分732可以用作筛选氧化物部分以允许浅注入(例如,低 能量注入)的掺杂剂沿-z方向穿透,以在第一漂移区域741和漏极区域746 之间形成缓冲区域745,而locos结构730的主要部分731阻挡浅注入(例 如,低能量注入)的掺杂剂穿透。示例器件700还可以包括“衬底表面延伸 部”749(或层表面延伸部)。衬底表面延伸部749被定义为locos结构730 和漏极区域746之间的衬底表面(或层表面)的未被locos结构730的任何 部分覆盖的部分。衬底表面延伸部749(和相应保留的锥形部分732)可以允 许浅注入(例如,低能量注入)的掺杂剂穿透其中以在第一漂移区域741和 漏极区域748之间形成缓冲区域745。锥形部分732在从locos结构730(或 从locos结构730的主要部分731下方的第一漂移区域741)朝向漏极区域 746的方向上具有逐渐减小的厚度,并且因此相应缓冲区域745的掺杂剂浓度 在从locos结构730(或从locos结构730的主要部分731下方的第一漂 移区域741)朝向漏极区域746的方向上逐渐且平滑地增加(参见例如图6的 椭圆区域)。

46.locos结构730在半导体层720上、在半导体层720上方或部分在半导 体层720中。

locos结构730(例如,场释放(field-relief)locos结构) 沿半导体层720的第二表面722和沿面内方向(x轴)延伸,以为扩展漏极 区域746提供场间隙。漏极区域746通过相对轻掺杂的第一漂移区域741和 漂移过渡区域742以及缓冲区域745远离沟道区域751延伸或布置。locos 结构730的材料可以包括氧化硅。在一些示例中,locos结构730的主要部 分731沿面外方向的厚度在30nm至400nm的范围内。例如,对于较低电压 的ldmos或漏极扩展晶体管器件(例如,5v至40v),locos结构730的 主要部分731沿面外方向的厚度在30nm至200nm的范围内;并且例如,对 于较高电压的ldmos或漏极扩展晶体管器件(例如,40至120v),locos 结构730的主要部分731的厚度在200nm至400nm的范围内。locos结构 730在第一漂移区域741上或上方并且在漏极区域746和沟道区域751之间。

47.在一些示例中,locos结构730的locos到locos距离d-7ll(即, locos结构730的主要部分731之间的距离)具有在300nm至1400nm范围 内的值;并且漏极区域746的宽度d746具有在100至400nm范围内的值。 在某些示例中,locos结构730的主要部分731与硅化物接触件748的边缘 e71之间的距离d71具有100至500nm范围内的值。

48.第一漂移区域741具有比缓冲区域745低的掺杂剂浓度。第一漂移区域 741或第一漂移区域741的一部分在漂移过渡区域742和缓冲区域745之间延 伸。在图7的示例中,第一漂移区域741为n掺杂剂浓度;并且漂移过渡区 域742和缓冲区域745具有n+掺杂剂浓度。

49.沿着面内方向(x轴),缓冲区域745在漏极区域746和位于locos结 构730下方的第一漂移区域741的至少一部分之间横向延伸。缓冲区域745 与locos结构730的锥形部分732接触并且在locos结构730的锥形部分732下方并且与漏极区域746接触。例如,缓冲区域745沿面外方向(z轴) 与locos结构730的锥形部分732相邻或在locos结构730的锥形部分732 下方。在一些示例中,缓冲区域745沿面内方向(例如,x轴)的横向宽度 在近似100nm至500nm的范围内。在某些示例中,主要部分731和漏极区域 746之间的锥形部分732沿面内方向(例如,x轴)的横向宽度在近似20nm 至500nm的范围内。

50.缓冲区域745与漏极区域746、第一漂移区域741、locos结构730的 锥形部分732和衬底表面延伸部749接触。缓冲区域745沿面内方向(x轴) 位于第一漂移区域741(或第一漂移区域741的一部分)和漏极区域746之间。, 缓冲区域745或缓冲区域745的一部分在locos结构730的锥形部分732下 方的位置处,例如在具有(与locos结构730的锥形部分732相比)相同x 值和y值但不同z值的位置处。

51.在图7的示例中,缓冲区域745和漂移过渡区域742具有n+掺杂剂浓度; 并且第一漂移区域741具有n掺杂剂浓度;并且漏极区域746具有n++掺杂 剂浓度;并且半导体区域725具有p-掺杂剂浓度。缓冲区域745的掺杂剂浓 度大于第一漂移区域741的掺杂剂浓度并且小于漏极区域745的掺杂剂浓度。 在一些示例中,缓冲区域745的掺杂剂浓度是第一漂移区域741的掺杂剂浓 度近似2至10倍高。

52.经由漂移区域(诸如第一漂移区域741)和半导体区域725的组合,可以 实现漂移区域的减小表面场(resurf)效应。在一些示例中,响应于向n型 漂移区域(诸如第一漂移区域741)和p型半导体区域725的p-n结提供反向 偏置,n型第一漂移区域741(诸如作为locos结构730下方的n型第一漂 移区域741的一部分)被耗尽,从而实现半导体器件700的第一漂移区域741 的resurf效应。

53.可以选择第一漂移区域741中的掺杂区域的剂量(例如,每面积的掺杂 剂)以满足

减小表面场(resurf)条件,这可以提供第一漂移区域741的耗 尽,例如,在截止状态(栅极电压=0伏)下。靠近漏极区域746并作为第二 漂移区域操作的缓冲区域745增加剂量超过resurf条件,使得在截止状态 (栅极电压=0伏)下,当第一漂移区域741的耗尽边缘与缓冲区域745相遇 时发生碰撞电离,引发器件击穿。

54.随着漏极电压增加超过击穿,由于碰撞电离,在第一漂移区域741中建 立了过量的电子和空穴浓度,从而推动第一漂移区域741的耗尽边缘更靠近 漏极区域746。漏极区域746的掺杂足够高,并且当第一漂移区域741的耗尽 边缘到达漏极区域746时,第一漂移区域741中的电场急剧增加,并且发生 雪崩,这可能导致器件破坏。通过包括缓冲区域745,在半导体器件700的击 穿的引发和灾难性故障之间提供了可以发生碰撞电离而不会立即发生器件故 障的有限电压区域。这种能力称为耐用性,并且它导致半导体器件700(诸如 功率晶体管)能够幸免于在例如电力电子系统中可能发生的诸如热开关或电 感器负载突降的故障条件。

55.管体区域750在半导体层720中,并且包括沟道区域(或沟道区域的一 部分)751,例如,该沟道区域沿面内方向(x轴)横向地与漂移过渡区域742 相邻。沟道区域751进一步延伸到并包括半导体区域725的在管体区域750 和漂移过渡区域742之间并且与栅极结构760相邻的部分726。源极区域756、 漏极区域746和管体接触区域755在半导体层720中。源极区域756沿面内 方向(x轴)与沟道区域751横向相邻。管体接触区域755沿面内方向(x 轴)与源极区域756横向相邻,并提供到管体区域750的电连接。

56.在图7的示例中,具有p掺杂剂浓度的管体区域750用作管体区域。在 其它示例中,半导体区域725可以延伸到管体区域750的区域以用作或操作 为管体区域,而不需要具有区域750。沟道区域751在源极区域756和漂移区 域(包括第一漂移区域741、漂移过渡区域742和缓冲区域745)之间。沟道 区域751沿面内方向(x轴)延伸。源极区域756、管体区域750、缓冲区域 745和漏极区域746从半导体层720的第二表面722朝向第一表面721延伸。

57.栅极结构760在管体区域750的沟道区域751上或上方,并且包括栅极 介电层761和在栅极介电层761上的栅电极762。栅极介电层761在沟道区域 751上方延伸,并且在漂移过渡区域742和locos结构730的一部分上方延 伸。栅电极762具有超出沟道区域751并朝向第一漂移区域741延伸的部分, 并且栅电极762的该部分可以是或用作场板,以控制场线的分布,使第一漂 移区域741中的静电场成型,并增加半导体器件700的击穿电压。在图7的 示例中,场板是栅电极762的组成部分。在其它示例中,场板是相对于栅电 极分离的部分,并且电耦合到端子,诸如栅电极。

58.在一些示例中,栅电极762的材料包括多晶硅和/或任何其它合适的材料。 在一些示例中,栅极介电层761的材料包括氧化硅和/或任何其它合适的介电 材料。

59.侧壁间隔件765沿着或位于栅电极762的侧面。侧壁间隔件765可以包 括二氧化硅、氮化硅、二氧化硅和氮化硅的多层和/或任何其它合适的绝缘层。 siblk层770在locos结构730和衬底表面延伸部749上或上方。siblk 层770在locos结构730的暴露部分上方延伸并覆盖locos结构730的暴 露部分,其中locos结构730的暴露部分从栅极结构760和侧壁间隔件765 暴露。siblk层770部分地在栅电极762上方延伸。

60.siblk层770包括保护locos结构730和缓冲区域745(例如防止其上 形成硅化物)的材料。在一些示例中,siblk层770包括阻挡硅化物形成的 氧化物材料和/或氮化物材料。

在某些示例中,siblk层770包括硅化物阻挡 材料,其在制造半导体器件时在硅化物接触件形成期间和之后在使脱釉和其 它操作期间减轻或防止locos结构730和缓冲区域745的硅化。

61.在图7的示例中,第一漂移区域741具有n掺杂剂浓度;缓冲区域745 具有n+掺杂剂浓度;漏极区域746具有n++掺杂剂浓度;管体区域750具有 p掺杂剂浓度;管体接触区域755具有p++掺杂剂浓度;源极区域756具有 n++掺杂剂浓度;区域741、745、746、756为n型掺杂或具有n型导电性, 并且区域750、725为p型掺杂或具有p型导电性。在其它示例中,可以根据 应用场景为半导体器件700的部件(诸如725、741、742、745、746)选择各 种掺杂剂浓度和不同的掺杂类型。

62.参考图8,漏极区域746沿面内方向(y轴)延伸。衬底表面延伸部749 沿面内方向(y轴)延伸并进一步以弯曲形状延伸以形成在xy平面中横向 环绕漏极区域746的整体构件;并且缓冲区域745(图8中未示出)可以以相 同或相似的方式沿面内方向(y轴)延伸并进一步以弯曲形状延伸以形成在 xy平面中横向环绕漏极区域746的整体区域。locos结构730沿面内方向 (y轴)延伸并且进一步以弯曲形状延伸以形成在xy平面中横向环绕漏极 区域746和衬底表面延伸部749的整体locos结构。

63.可根据应用场景为半导体器件700的部件选择各种布置,诸如横向关系。 作为另一示例,半导体器件700的缓冲区域745是在漏极区域746的两侧沿 面内方向(y轴)延伸的两个细长条形区域;并且半导体器件700的locos 结构730是在漏极区域746的两侧沿面内方向(y轴)延伸的两个细长条形 结构。

64.图9图示了基线半导体器件(诸如器件100)的电流-电压特性;并且图 10图示了示例半导体器件(诸如器件200、400、700)的电流-电压特性。图 9的基线半导体器件的soa曲线1是图9的基线半导体器件的故障边界。soa 曲线1(即图9的基线半导体器件的故障边界)叠加在图10中。图10中的示 例半导体器件的电流-电压曲线延伸超过soa曲线1。因此,与图9的基线半 导体器件的soa相比,soa在图10的示例半导体器件中更宽。添加或具有 围绕n++漏极区域(例如,图7中的746)的缓冲区域(例如,图7中的745) 可以改进功率晶体管soa。它通过柯克(kirk)效应起作用,其中耗尽边缘 在高注入条件下移动到更重掺杂的硅区域,这随着漏极电流的增加而发生。 这具有随着栅极电压和漏极电流增加而增加器件击穿电压的效果。此类器件 被称为耐用的,因为它比非耐用的功率晶体管更能幸免于击穿(至少暂时地, 直到来自其它机制的损坏累积)。功率晶体管soa是耐用性的定量测量,并 且与对应于图9的基线半导体器件相比,在图10的示例半导体器件中更宽的 soa指示改进的耐用性。

65.图11图示了示例半导体器件(诸如器件200、400、700)与基线半导体 器件相比的比导通电阻,其中rsp是比导通电阻,bvdss是漏极到源极击穿 电压。与基线半导体器件的rsp曲线c1相比,与本公开一致的示例半导体器 件(诸如器件200、400、700)的rsp曲线c2已经保留或甚至降低了比导通 电阻。

66.图12图示了示例半导体器件(诸如器件200、400、700)与基线半导体 器件(诸如器件100)相比的回弹电流-电压特性。与基线半导体器件(诸如 器件100)的回弹电流曲线1中的回弹电流密度相比,本公开的示例半导体器 件的回弹电流曲线2中的回弹电流密度得到增加和改进。因此,在与本公开 一致的半导体器件中增加和改进了回弹电流密度。由于功

率晶体管电流-电压 i(v)曲线开始类似于电阻器i(v)曲线(即在i(v)绘图中向上和向右倾 斜),因此更宽的soa回弹区域与更高的回弹电流齐头并进。因此,更高的 回弹电流是具有更好耐用性的功率晶体管的标志。

67.在本公开中,通过增加在locos结构和硅化物接触件的边缘之间的距 离,在locos结构的主要部分和漏极区域之间保留了锥形部分,并且保留的 锥形部分可以用作筛选氧化物部分以允许浅注入(例如低能量注入)的掺杂 剂穿透其中以形成从器件的第一漂移区域到重掺杂的漏极区域的平滑掺杂浓 度过渡。因此,由于柯克效应,可以改进耐用性,并且可以改进安全操作区, 同时由于缓冲区域的掺杂剂浓度大于第一漂移区域的掺杂剂浓度,因此可以 保留或降低比导通电阻(rsp)。

68.图13至图22和图7图示了形成示例半导体器件700的各个阶段的示例 结构的截面图,并且因此图示了形成半导体器件700的示例方法。

69.图13图示了在半导体层720(例如,半导体衬底)上或上方形成氮化硅 硬掩模。图案化氮化硅硬掩模m0在半导体层720上或上方,并且具有一个或 多个开口以暴露半导体层720的第二表面722的一个或多个部分以用于局部 氧化。图案化氮化硅硬掩模m0可以通过沉积氮化硅膜并利用图案化光致抗蚀 剂掩模对氮化硅膜的一个或多个部分执行氮化物蚀刻来形成。

70.图14图示了通过执行硅局部氧化(locos)工艺来形成locos结构730。 locos结构331形成在半导体层720的由图案化掩模m0暴露的部分硅表面 上或上方,以及在预期第一漂移区域(图7中的741)上或上方。图7的一个 或多个相应locos结构730的主要部分731各自对应于在locos工艺期间 使用的图案化掩模m0的相应开口。例如,主要部分731沿x轴的宽度d731 对应或等于图案化掩模m0的相应开口的宽度e0。此外,在locos工艺期 间,氧可以(或被导致)在下面的半导体层与上面的掩膜m0之间扩散,并超 出图案化掩膜m0的相应开口的宽度e0,并相应地使锥形部分732(即,鸟 喙部)形成并延伸超过图案化掩模m0的相应开口的宽度e0。在形成locos 结构331之后,可以去除图案化掩模m1。

71.图15图示了沉积介电材料以在半导体层720和locos结构730上或上 方形成栅极介电层761。可以进一步蚀刻栅极介电层761以具有合适的尺寸和 形状。在一些示例中,栅极介电层761的材料包括氧化硅和/或任何其它合适 的介电材料。

72.图16图示了利用掩模和通过离子注入形成第一漂移区域。第一漂移区域 741可以通过以第一注入能量的第一离子注入1100(例如,深注入)利用限 定第一离子注入1100的暴露注入区域的图案化光致抗蚀剂掩模m1而形成。 在图16的示例,第一漂移区域741具有n的掺杂剂浓度。在一些示例中,第 一离子注入具有的剂量(例如总剂量)近似等于2至4

×

10

12

cm-2

的resurf 条件,使得漂移区域(诸如第一漂移区域741)可以被耗尽,例如在截止状态 (栅极电压=0伏)中,并且可以实现半导体器件700的增加的击穿电压。

73.图17图示了利用掩模和通过离子注入而形成漂移过渡区域和缓冲区域。 漂移过渡区域742和缓冲区域745可以通过以第二注入能量的第二离子注入 1200(例如,浅注入)利用与第一离子注入1100(例如,深注入)相同的图 案化光致抗蚀剂掩模m1而形成,而不必使用附加掩模,以便简化制造程序并 降低制造成本。因为锥形部分732可以用作筛选氧化物部分以允许浅注入(例 如,低能量注入)的掺杂剂穿透其中,所以可以通过使用与漂移过渡区域相 同的第二离子注入1200并且通过使用与第一离子注入1100(用于形成第一漂 移

区域741)相同的图案化光致抗蚀剂掩模m1来形成缓冲区域745,无需附 加的光致抗蚀剂掩模或注入,并且因此可以降低制造成本。第二离子注入1200 的第二注入能量低于第一离子注入1100的第一注入能量,并且第二离子注入 1200具有比第一离子注入1100浅的注入深度。因此,漂移过渡区域742和缓 冲区域745的深度小于第一漂移区域741的深度。在一些示例中,在第一离 子注入1100之后执行第二离子注入1200。在其它示例中,在第一离子注入 1100之前执行第二离子注入1200。

74.第一离子注入1100的参数(诸如注入能量、剂量,和掺杂剂)可以根据 不同的应用场景进行选择,并且第一离子注入1100可以包括具有各种或不同 的参数的各种深注入。例如,第一离子注入1100可以包括具有磷掺杂剂的深 注入和具有砷掺杂剂的另一深注入。第二离子注入1200的参数(诸如注入能 量、剂量,和掺杂剂)可以根据不同的应用场景进行选择,并且第二离子注 入1200可以包括具有各种或不同的参数的各种浅注入。例如,第二离子注入 1200可以包括具有磷掺杂剂的浅注入和具有砷掺杂剂的另一浅注入。

75.可以选择第二离子注入1200的第二注入能量,使得locos结构730的 主要部分731可以阻挡第二注入1200的掺杂剂,但锥形部分732可以允许第 二注入1200的掺杂剂穿透其中。在一些示例中,locos结构730的主要部 分731具有30nm至200nm的厚度,并且第二离子注入1200(浅注入)的第 二注入能量对于磷掺杂剂小于50kev,并且对于砷掺杂剂小于100kev,并且 对于锑掺杂剂小于200kev。第二注入能量可以根据locos结构730的主要 部分731的选择的厚度来选择。例如,在locos结构730的主要部分731的 较大厚度的情况下,可以增加第二注入能量。

76.在图17的该步骤处,形成n+掺杂剂浓度的掺杂区域743,掺杂区域743 包括缓冲区域745和对应于预期漏极区域的区域(图7)。对应于预期漏极区 域的区域的掺杂剂浓度可以在另一个步骤处进一步增加到n++掺杂剂浓度。 掩模m1覆盖预期源极区域和管体区域,暴露对应于漂移过渡区域742、 locos结构730和掺杂区域743的部分。在离子注入1100期间,由于注入 能量相对较高,掺杂剂可以穿透locos结构730,并且可以在由掩模m1限 定的暴露部分中形成第一漂移区域741。在第二离子注入1200期间,由于注 入能量相对较低,掺杂剂被locos结构730的主要部分731阻挡并且不能穿 透locos结构730的主要部分731。然而,保留的锥形部分732(用作筛选 氧化物部分)和衬底表面延伸部749(参见图7)可以允许低能量注入1200 的掺杂剂穿透其中以形成具有平滑掺杂浓度过渡的缓冲区域745。在图17的 示例中,漂移过渡区域742和缓冲区域745具有n+的掺杂剂浓度。在使用后 可以去除图案化光致抗蚀剂掩模m1。

77.图18图示了在半导体层中形成管体区域。管体区域750被掩埋在半导体 层720中。在图18的示例中,通过注入1300利用图案化光致抗蚀剂掩模m2 将p型掺杂剂注入到半导体层720中而形成管体区域750;并且管体区域750 具有p的掺杂剂浓度。在使用后可以去除光致抗蚀剂掩膜m2。

78.图19图示了沉积材料以在栅极介电层761上或上方形成栅电极762。可 以进一步蚀刻栅电极762以具有合适的尺寸和形状。可以在栅电极762上或 上方形成图案化掩模m3,用于限定栅电极762和栅极介电层761的尺寸和形 状。

79.图20图示了利用图案化光致抗蚀剂掩模m3蚀刻掉栅电极762和栅极介 电层761的一个或多个部分,使得栅电极762和栅极介电层761具有合适的 尺寸和形状。蚀刻掉被图案

化掩模m3暴露的栅电极762和栅极介电层761 的部分,并且相应地获得栅电极762和栅极介电层761的合适尺寸和形状。 在使用后可以去除图案化光致抗蚀剂掩模m3。在一些示例中,栅电极762的 材料包括多晶硅和/或任何其它合适的材料。在一些示例中,栅极介电层761 的材料包括氧化硅和/或任何其它合适的介电材料。

80.图21图示了沿着栅电极762和栅极介电层761的侧面或在栅电极762和 栅极介电层761的侧面形成侧壁间隔件765。侧壁间隔件765可以通过在栅电 极762上方沉积薄膜并去除一定厚度的薄膜来形成。侧壁间隔件765可以包 括二氧化硅、氮化硅、二氧化硅和氮化硅的多层,和/或任何其它合适的绝缘 层,以便保护例如电敏沟道区域751和栅电极762。

81.图22图示了形成siblk层770并且形成源极区域756和漏极区域746。 siblk层770在locos结构730的暴露部分和缓冲区域745上方延伸,其中 locos结构730的暴露部分从栅极结构760和侧壁间隔件765暴露。siblk 层770部分地在栅电极762上方延伸。源极区域756和漏极区域746通过注 入利用图案化光致抗蚀剂掩模m5而形成。因此,形成具有n++掺杂剂浓度 的源极区域756;并且与缓冲区域745横向地(例如,沿x轴)相邻并接触 缓冲区域745形成具有n++掺杂剂浓度的漏极区域746。

82.返回参考图7,管体接触区域755形成为与管体区域750接触,并且硅化 物接触件748形成在漏极区域746上或上方,并且钨接触件747形成在硅化 物接触件748上或上方。管体接触区域755可以通过掺杂剂注入利用图案化 光致抗蚀剂掩模而形成,并且可以具有p++掺杂剂浓度。光致抗蚀剂掩膜被 用于制造工艺,并且可以在其使用后去除。在一些示例中,硅化物接触件748 可以通过漏极区域746的硅的硅化形成在漏极区域746上或上方。

83.在图15的示例中,沉积介电材料以在半导体层720和locos结构730 上或上方形成栅极介电层761,这可以在形成第一漂移区域741、漂移过渡区 域742、缓冲区域745和管体区域750之前执行。在其它示例中,介电材料可 以通过在半导体层720的第二表面722(或第二表面722的一部分)处的硅的 氧化来热生长以形成相应栅极介电层,这可以在形成第一漂移区域741、漂移 过渡区域742、缓冲区域745和管体区域750之后执行。

84.在不脱离本公开的范围的情况下,可以对本文描述的系统、器件和方法 进行修改、添加或省略。此外,本文公开的系统和器件的操作可以通过包括 更多、更少或其它部件来执行;并且所描述的方法可以包括更多、更少或其 它步骤。此外,可以以任何合适的顺序执行步骤。

85.在整个说明书中使用术语“耦合”。该术语可以涵盖实现与本公开的描述 一致的功能关系的连接、通信或信号路径。例如,如果器件a生成信号以控 制器件b执行动作,则在第一示例中,器件a耦合到器件b,或者在第二示 例中,如果介入部件c基本上不改变器件a和器件b之间的功能关系b,则 器件a通过介入部件c耦合到器件,使得器件b经由器件a生成的控制信号 由器件a控制。

86.在权利要求的范围内,对所描述的实施例进行修改是可能的,并且其它 实施例也是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1