埋入式栅极结构及其形成方法及动态随机存取存储器结构与流程

本发明是有关于一种半导体元件及其形成方法,且特别是有关于一种具有负电容介电材料的埋入式栅极结构及其形成方法,及具有埋入式栅极结构的动态随机存取存储器结构。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)属于一种挥发性存储器,且由多个存储单元组成。具体来说,各存储单元主要由晶体管与由晶体管控制的电容器所组成,且通过字线及位线来进行选择。

2、随着半导体装置的积集度的提升,近年来发展出具有埋入式字线的dram,然而,随着dram的尺寸的微缩,栅极引发漏极漏电流(gate induced drain leakage,gidl)变得更严重,进而影响写入恢复时间(write recovery time,twr)及亚阈值摆幅(subthresholdswing,ss),导致动态随机存取存储器的效能降低,例如降低dram的运行速度以及增加电源耗损。

技术实现思路

1、本发明实施例提供一种埋入式栅极结构及其形成方法,能够缩短存储器装置写入恢复时间及降低晶体管的亚阈值摆幅,同时避免gidl效应。

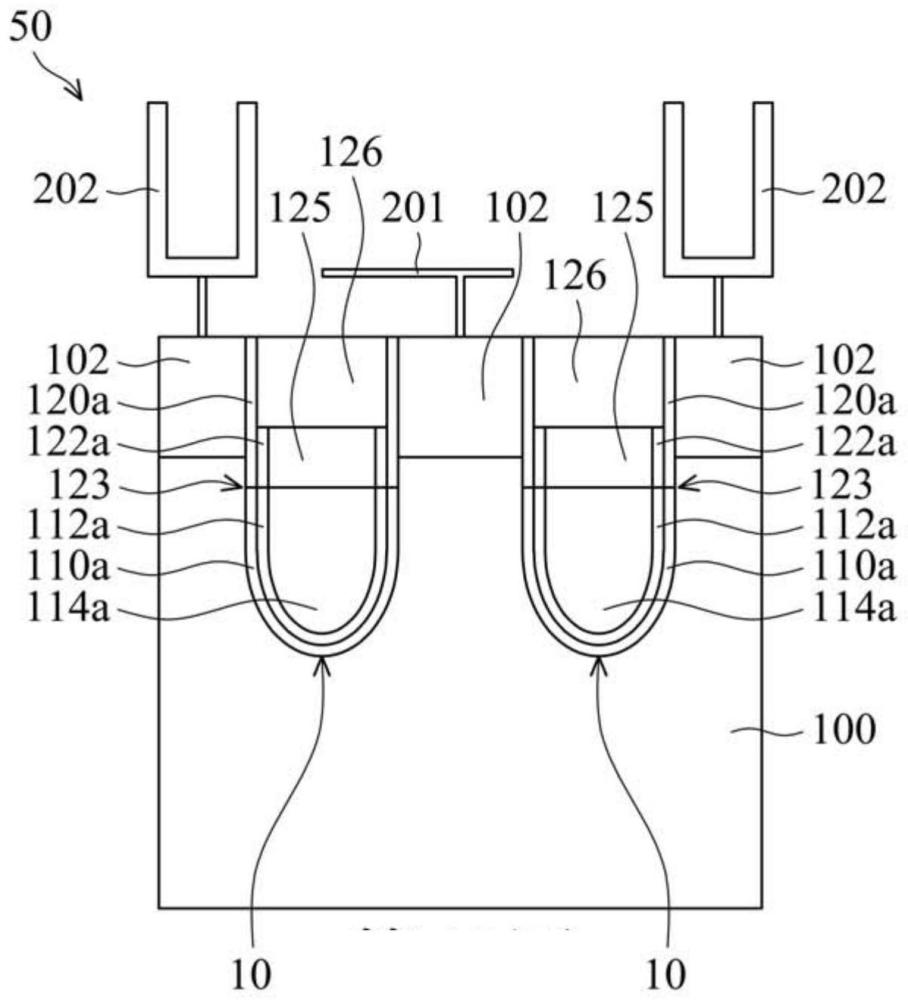

2、在本发明的一些实施例中,揭示一种埋入式栅极结构,设置于半导体衬底的栅极沟槽中,栅极沟槽位于源极区与漏极区之间,埋入式栅极结构包括:第一栅极介电层,形成于栅极沟槽的下部的表面,其中第一栅极介电层包括负电容介电材料;第一栅极电极,形成于第一栅极介电层上;第二栅极介电层,形成于栅极沟槽的上部的表面,其中第二栅极介电层包括不同于负电容介电材料的介电材料,且第一栅极介电层与第二栅极介电层之间的界面低于源极区与漏极区的底表面;及绝缘盖层,形成于第一栅极电极上,以填满栅极沟槽的剩余空间。

3、在本发明的一些实施例中,揭示一种动态随机存取存储器结构,包括:半导体衬底,具有源极区、漏极区及位于源极区与漏极区之间的栅极沟槽;如前述的埋入式栅极结构;位线,电连接至源极区与漏极区的其中一者;以及电容器,电连接至源极区与漏极区的另一者。

4、在本发明的一些实施例中,揭示一种埋入式栅极结构的形成方法,包括:形成栅极沟槽于半导体衬底中;顺应性地形成第一栅极介电层于栅极沟槽的下部的表面,其中第一栅极介电层包括负电容介电材料;形成第一栅极电极于第一栅极介电层上;顺应性地形成第二栅极介电层于栅极沟槽的上部的表面,其中第二栅极介电层包括不同于负电容介电材料的介电材料,且第一栅极介电层与第二栅极介电层之间的界面低于源极区与漏极区的底表面;以及形成绝缘盖层于第一栅极电极上,以填满栅极沟槽的剩余空间。

5、根据本发明的一些实施例,由于使用了负电容介电材料作为埋入式栅极结构的栅极介电层,因此可增加导通电流(ion),进而缩短存储器装置的写入恢复时间。再者,藉由负电容介电材料所带来的负电容效应,能够降低晶体管的亚阈值摆幅。如此一来,可提高存储器装置的操作速度并降低存储器装置的操作电压,进而提升存储器装置的效能。另外,根据本发明的一些实施例,藉由使用不同于负电容材料的另一种介电材料与负电容材料作为埋入式栅极结构的栅极介电层,可补强栅极介电层抑制gidl效应的能力。如此一来,可有效提升存储器装置的成品率及可靠度。

技术特征:

1.一种埋入式栅极结构,其特征在于,设置于一半导体衬底的一栅极沟槽中,该栅极沟槽位于一源极区与一漏极区之间,该埋入式栅极结构包括:

2.如权利要求1所述的埋入式栅极结构,其特征在于,该界面不高于该第一栅极电极的顶表面。

3.如权利要求1所述的埋入式栅极结构,其特征在于,更包括:

4.如权利要求1所述的埋入式栅极结构,其特征在于,该负电容介电材料包括:氧化铪锆、掺杂的氧化铪、掺杂的氧化锆、磷酸二氢钾、钛酸钡、锆钛酸铅、铁酸铋、钽酸锶铋、氮化铝钪或上述的组合。

5.如权利要求1所述的埋入式栅极结构,其特征在于,该介电材料包括氧化硅、氮氧化硅、低k值介电材料或上述材料的组合。

6.如权利要求1所述的埋入式栅极结构,其特征在于,更包括一第二栅极电极,形成于该第一栅极电极与该绝缘盖层之间,且该界面低于该第二栅极电极的底表面。

7.如权利要求6所述的埋入式栅极结构,其特征在于,更包括:

8.如权利要求6所述的埋入式栅极结构,其特征在于,更包括:

9.如权利要求6所述的埋入式栅极结构,其特征在于,该第二栅极电极的最大宽度大于该第一栅极电极的最大宽度,且该第二栅极电极的最大厚度小于该第一栅极电极的最大厚度。

10.一种动态随机存取存储器结构,其特征在于,包括:

11.一种埋入式栅极结构的形成方法,其特征在于,包括:

12.如权利要求11所述的埋入式栅极结构的形成方法,其特征在于,该界面不高于该第一栅极电极的顶表面。

13.如权利要求12所述的埋入式栅极结构的形成方法,其特征在于,更包括:

14.如权利要求13所述的埋入式栅极结构的形成方法,其特征在于,更包括:

15.如权利要求11所述的埋入式栅极结构的形成方法,其特征在于,该负电容介电材料包括:氧化铪锆、掺杂的氧化铪、掺杂的氧化锆、磷酸二氢钾、钛酸钡、锆钛酸铅、铁酸铋、钽酸锶铋、氮化铝钪或上述的组合。

16.如权利要求11所述的埋入式栅极结构的形成方法,其特征在于,该介电材料包括氧化硅、氮氧化硅、低k值介电材料或上述材料的组合。

17.如权利要求11所述的埋入式栅极结构的形成方法,其特征在于,更包括:

18.如权利要求17所述的埋入式栅极结构的形成方法,其特征在于,更包括:

19.如权利要求17所述的埋入式栅极结构的形成方法,其特征在于,更包括:

20.如权利要求17所述的埋入式栅极结构的形成方法,其特征在于,该第二栅极电极的最大宽度大于该第一栅极电极的最大宽度,且该第二栅极电极的最大厚度小于该第一栅极电极的最大厚度。

技术总结

在此提供一种埋入式栅极结构及其形成方法及动态随机存取存储器结构。埋入式栅极结构包括第一栅极介电层、第一栅极电极、第二栅极介电层及绝缘盖层。第一栅极介电层形成于半导体衬底的栅极沟槽的下部的表面。第二栅极介电层形成于栅极沟槽的上部的表面。第一栅极介电层包括负电容介电材料,而第二栅极介电层包括不同于负电容介电材料的介电材料。第一栅极电极形成于第一栅极介电层上。第一栅极介电层与第二栅极介电层之间的界面低于半导体衬底的源极区与漏极区的底表面。绝缘盖层形成于第一栅极电极上,以填满栅极沟槽的剩余空间。本发明可补强栅极介电层抑制GIDL效应的能力,有效提升存储器装置的效能、成品率及可靠度。

技术研发人员:陈侑廷,张维哲

受保护的技术使用者:华邦电子股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!