硅基MEMS滤波器的制作方法

硅基mems滤波器

技术领域

1.本发明涉及滤波器技术领域,尤其涉及一种硅基mems滤波器。

背景技术:

2.随着无线通信系统的快速发展,频谱和系统的空间资源也变的十分紧张,滤波器作为微波系统中不可或缺的重要选频器件,对滤波器的矩形系数和尺寸有了更高的要求。

3.滤波器可使某段频率的电信号通过,而对其他频率的电信号进行阻拦,提高滤波器的矩形系数和减小滤波器的尺寸成为滤波器的关键设计难点。mems工艺是一种在高阻硅上制作金属图形、通孔等立体结构的微机械加工工艺,加工精度可达到微纳米量级。利用mems工艺加工的硅基滤波器具有体积小、重量轻、高一致性、易集成等诸多优点,基于mems滤波器的产品应用将在未来通信系统中扮演重要角色。

4.目前,通常是通过增加滤波器阶数来提高产品抑制度,但会增加滤波器的体积和增大矩形系数,如何在小型化产品的基础上提高矩形系数,成为目前亟需解决的技术问题。

技术实现要素:

5.本发明实施例提供了一种硅基mems滤波器,以解决目前小型化的滤波器矩形系数较低的问题。

6.第一方面,本发明实施例提供了一种硅基mems滤波器,包括:

7.第一硅基板,在第一硅基板上表面的第一区域内设有一n阶滤波器、第一u型耦合线、第二u型耦合线、输入馈线和输出馈线;n阶滤波器的一端与第一u型耦合线的一侧连接,第一u型耦合线的另一侧与输入馈线连接;n阶滤波器的另一端与第二u型耦合线的一侧连接,第二u型耦合线的另一侧与输出馈线连接;在第一硅基板上表面设有第一金属层,且第一金属层避开第一区域;n阶滤波器中的每个谐振杆的一端均与第一金属层连接;

8.第二硅基板,位于第一硅基板的上表面,在第二硅基板的上表面的第二区域内设有第一抑制谐振杆和第二抑制谐振杆,且第一抑制谐振杆垂直位于第一u型耦合线的正上方,第二抑制谐振杆垂直位于第二u型耦合线的正上方,第一u型耦合线和第二u型耦合线的开口方向分别为第一抑制谐振杆和第二抑制谐振杆的长度方向;在第二硅基板上表面上设有第二金属层,且第二金属层避开第二区域;第一抑制谐振杆和第二抑制谐振杆的一端均与第二金属层连接。

9.在一种可能的实现方式中,第一抑制谐振杆的宽度等于第一u型耦合线的宽度与第一u型耦合线的间隔之和;第二抑制谐振杆的宽度等于第二u型耦合线的宽度与第二u型耦合线的间隔之和。

10.在一种可能的实现方式中,n阶滤波器包括n个谐振杆,且n个谐振杆之间均通过耦合线连接;

11.n阶滤波器还包括一第一耦合线,n阶滤波器中的第一个谐振杆或最后一个谐振杆与第一耦合线的一端连接,第一耦合线的另一端与第一u型耦合线或第二u型耦合线连接,

第一耦合线和与其连接的谐振杆形成感性耦合。

12.在一种可能的实现方式中,n阶滤波器包括n个谐振杆,且n个谐振杆之间均通过耦合线连接;

13.n阶滤波器还包括一第二耦合线,n阶滤波器中的第一个谐振杆或最后一个谐振杆与第二耦合线的一端间隔设置,第二耦合线的另一端与第一u型耦合线或第二u型耦合线连接,第二耦合线和与其间隔设置的谐振杆形成容性耦合。

14.在一种可能的实现方式中,n阶滤波器包括n个谐振杆,且n个谐振杆之间均通过耦合线连接;

15.n阶滤波器还包括一第一耦合线和一第二耦合线,n阶滤波器中的第一个谐振杆与第一耦合线连接,第一耦合线与第一u型耦合线连接,第一耦合线和与其连接的第一个谐振杆形成感性耦合;n阶滤波器中的最后一个谐振杆与第二耦合线的一端间隔设置,第二耦合线的另一端与第二u型耦合线连接,第二耦合线和与其间隔设置的最后一个谐振杆形成容性耦合。

16.在一种可能的实现方式中,第一耦合线为z形耦合线;

17.第二耦合线由多段耦合线组成,其中,第二耦合线至少包括一段与谐振杆平行的耦合线。

18.在一种可能的实现方式中,n阶滤波器中的每个谐振杆均为单端短路的1/4波长谐振器。

19.在一种可能的实现方式中,第一抑制谐振杆和第二抑制谐振杆均为单端短路的1/4波长谐振器。

20.在一种可能的实现方式中,第一硅基板的金属层上以及第二硅基板的金属层上均布设有金属化通孔,第一硅基板的下表面的所有区域均布设有金属。

21.在一种可能的实现方式中,第一硅基板的厚度小于第二硅基板的厚度,第一硅基板和第二硅基板均为高阻硅基板。

22.本发明实施例提供一种硅基mems滤波器,采用mems工艺在双层硅基板上制备了含有非谐振节点结构的滤波器,即通过在第一硅基板上设置第一u型耦合线和第二u型耦合线,在第二硅基板的相应位置上制备与第一u型耦合线和第二u型耦合线相对应的第一抑制谐振杆和第二抑制谐振杆,从而第一u型耦合线和第一抑制谐振杆、第二u型耦合线和第二抑制谐振杆在n阶滤波器的通带外,形成两个传输零点,提高了滤波器的矩形系数。

附图说明

23.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

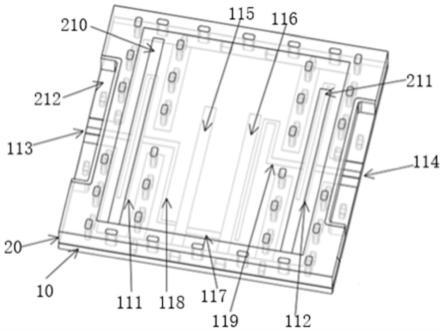

24.图1是本发明实施例提供的硅基mems滤波器的整体结构示意图;

25.图2是本发明实施例提供的图1中的第一硅基板的上表面的结构示意图;

26.图3是本发明实施例提供的图1中的第一硅基板的下表面的结构示意图;

27.图4是本发明实施例提供的图1中的第二硅基板的上表面的结构示意图。

具体实施方式

28.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

29.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图通过具体实施例来进行说明。

30.目前,主要通过增加滤波器阶数来提高产品抑制度,但会增加滤波器的体积和增大损耗。引入传输零点可在保持较小体积的基础上,实现较高的抑制度。然而目前通过引入交叉耦合结构虽然也可以实现在滤波器中引入传输零点,但是交叉耦合结构的设计灵活度较低,结构设计时较复杂。

31.为了解决现有技术问题,本发明实施例提供了一种硅基mems滤波器。下面对本发明实施例所提供的硅基mems滤波器进行介绍。

32.一种硅基mems滤波器,包括叠设在一起的第一硅基板和第二硅基板。在第一硅基板的上表面的第一区域内设有一n阶滤波器、第一u型耦合线、第二u型耦合线、输入馈线和输出馈线。n阶滤波器的一端与第一u型耦合线的一侧连接,第一u型耦合线的另一侧与输入馈线连接。n阶滤波器的另一端与第二u型耦合线的一侧连接,第二u型耦合线的另一侧与输出馈线连接。且在第一硅基板上表面设有第一金属层,且第一金属层避开第一区域;n阶滤波器中的每个谐振杆的一端均与第一金属层连接。

33.第二硅基板,位于第一硅基板的上表面。在第二硅基板的上表面的第二区域内设有第一抑制谐振杆和第二抑制谐振杆,且第一抑制谐振杆垂直位于第一u型耦合线的正上方,第二抑制谐振杆垂直位于第二u型耦合线的正上方。其中,第一u型耦合线和第二u型耦合线的开口方向分别为第一抑制谐振杆和第二抑制谐振杆的长度方向。且在第二硅基板上表面上设有第二金属层,且第二金属层避开第二区域。第一抑制谐振杆和第二抑制谐振杆的一端均与第二金属层连接。

34.其中,n阶滤波器为采用mems工艺在双层高阻硅上制备的。

35.通过在n阶滤波器中增加由第一u型耦合线和第一抑制谐振杆、第二u型耦合线和第二抑制谐振杆构成的非谐振节点,从而利用非谐振节点级联产生传输零点,提高滤波器的抑制性能及滤波器的矩形系数。含有非谐振节点的硅基mems滤波器,能够灵活实现零点所在位置及多零点特性,可以有效地提高滤波器的抑制度。在小型化滤波器的基础上进一步提升滤波器的性能,满足未来通信中对滤波器的更高要求。

36.一些实施例中,可以通过调节第一u型耦合线和第一抑制谐振杆、第二u型耦合线和第二抑制谐振杆的宽度,达到较好的抑制效果。

37.在此实施例中,可以将第一抑制谐振杆的宽度等于第一u型耦合线的宽度与第一u型耦合线的间隔之和。第二抑制谐振杆的宽度等于第二u型耦合线的宽度与第二u型耦合线的间隔之和。

38.示例性的,可将第一u型耦合线任一边的线宽设置为第一抑制谐振杆的宽度的1/3,第一u型耦合线的间隔也为第一抑制谐振杆的宽度的1/3,从而使得第一抑制谐振杆的宽度等于第一u型耦合线的宽度与第一u型耦合线的间隔之和。相应的,可将第二u型耦合线任

一边的线宽设置为第二抑制谐振杆的宽度的1/3,第二u型耦合线的间隔也为第二抑制谐振杆的宽度的1/3,从而使得第二抑制谐振杆的宽度等于第二u型耦合线的宽度与第二u型耦合线的间隔之和。

39.在此实施例中,为了便于调节零点抑制度,第一u型耦合线和第二u型耦合线的长度、位置均独立调谐,通过控制与第一抑制谐振杆和第二抑制谐振杆的耦合强度,调节零点抑制度。

40.一些实施例中,为了实现不同的馈电强度和相位,使滤波器有良好的带内驻波,得到良好的损耗和抑制,且进一步的减小滤波器的体积,可以在n阶滤波器中增加感性耦合的结构。

41.在此实施例中,n阶滤波器可以包括n个谐振杆,且n个谐振杆之间均通过耦合线连接。为了提高抑制,且减小滤波器的体积,在n阶滤波器的第一个谐振杆或最后一个谐振杆与一第一耦合线的一端连接,形成感性耦合。第一耦合线的另一端与第一u型耦合线或第二u型耦合线连接。

42.示例性的,可以将第一耦合线设置为z形耦合线。

43.一些实施例中,为了实现不同的馈电强度和相位,使滤波器有良好的带内驻波,得到良好的损耗和抑制,且进一步的减小滤波器的体积,可以在n阶滤波器中增加容性耦合的结构。

44.在此实施例中,n阶滤波器可以包括n个谐振杆,且n个谐振杆之间均通过耦合线连接。为了提高抑制,且减小滤波器的体积,在n阶滤波器的第一个谐振杆或最后一个谐振杆与一第二耦合线的一端间隔设置,第二耦合线的另一端与第一u型耦合线或第二u型耦合线连接,第二耦合线和与其间隔设置的谐振杆形成容性耦合。

45.示例性的,第二耦合线由多段耦合线组成,其中,第二耦合线至少包括一段与谐振杆平行的耦合线。

46.一些实施例中,为了实现不同的馈电强度和相位,使滤波器有良好的带内驻波,得到良好的损耗和抑制,且进一步的减小滤波器的体积,可以在n阶滤波器中同时增加感性耦合和容性耦合。

47.在此实施例中,n阶滤波器可以包括n个谐振杆,且n个谐振杆之间均通过耦合线连接。为了提高抑制,且减小滤波器的体积,在n阶滤波器的一端设置感性耦合,在n阶滤波器的另一端设置容性耦合。

48.示例性的,n阶滤波器中的第一个谐振杆与第一耦合线连接,第一耦合线与第一u型耦合线连接,第一耦合线和与其连接的第一个谐振杆形成感性耦合。n阶滤波器中的最后一个谐振杆与第二耦合线的一端间隔设置,第二耦合线的另一端与第二u型耦合线连接,第二耦合线和与其间隔设置的最后一个谐振杆形成容性耦合。

49.一些实施例中,为了得到良好的损耗和抑制,可以通过调节连接n个谐振杆之间的耦合线的位置,调节谐振器间耦合。

50.在此实施例中,n阶滤波器中的每个谐振杆均为单端短路的1/4波长谐振器。

51.为了便于调节n阶滤波器的通带频率,n阶滤波器中的每个谐振杆的长度是相互独立的,可以通过调节每个谐振杆的长度,从而调节n阶滤波器的通带频率。

52.一些实施例中,第一抑制谐振杆和第二抑制谐振杆均为单端短路的1/4波长谐振

器。可以通过调节其长度,灵活调节传输零点的位置。

53.示例性的,第一抑制谐振杆的长度可以大于第二抑制谐振杆的长度。

54.一些实施例中,为了保证良好的屏蔽特性,在第一硅基板的下表面全部设置接地金属。在第一硅基板的金属层上以及第二硅基板的金属层上均布设有金属化通孔。且位于第一硅基板的金属层上的金属化通孔为贯穿第一硅基板的上下表面,位于第二硅基板的金属层上的金属化通孔为贯穿第二硅基板的上下表面。位于两个硅基板的上下表面的金属化通孔的位置不做限制。

55.一些实施例中,为了增加滤波器的电容,且进一步缩小滤波器的体积,第一硅基板的厚度可以小于第二硅基板的厚度,第一硅基板和第二硅基板均为高阻硅基板。

56.一些实施例中,为了便于输入和输出,可在第二硅基板上对应输入馈线和输出馈线的位置处,设置凹槽,将输入馈线和输出馈线露出。

57.本发明提供的硅基mems滤波器,采用mems工艺在双层高阻硅基板上制备了含有非谐振节点结构的滤波器,即通过在第一硅基板上设置第一u型耦合线和第二u型耦合线,在第二硅基板的相应位置上制备与第一u型耦合线和第二u型耦合线相对应的第一抑制谐振杆和第二抑制谐振杆,从而第一u型耦合线和第一抑制谐振杆、第二u型耦合线和第二抑制谐振杆在n阶滤波器的通带外,组成两个传输零点,提高了滤波器的矩形系数。

58.请一并参照图1-图4,提供了一种硅基mems滤波器的结构示意图。该硅基mems滤波器包括第一硅基板10和第二硅基板20。第一硅基板10的厚度为0.12mm,第二硅基板20的厚度为0.25mm。

59.如图2所示,在第一硅基板10的第一区域110内设有二阶滤波器、第一u型耦合线111、第二u型耦合线112、输入馈线113和输出馈线114。

60.其中,二阶滤波器包括2个单端短路的1/4波长谐振器,图2中的115和116为2个单端短路的1/4波长谐振器,且2个谐振器的另一端与第一硅基板10的第一金属层连接。第一金属层布设在第一硅基板10的上表面,除第一区域110外的其他区域内,均布设有第一金属层,便于实现良好的屏蔽。两个单端短路的1/4波长谐振器之间连接有耦合线117,通过调节耦合线117的位置,调节谐振器间的耦合。

61.为了提高滤波器的性能,以及减小滤波器的体积,可在谐振器115上连接z型耦合线118。谐振器115和z型耦合线118形成感性耦合,通过调节谐振器115和z型耦合线118的接触点的位置,可以调节耦合强度。

62.此外,谐振器116和第二耦合线119形成容性阻抗,第二耦合线119的长度以及谐振器116和第二耦合线119的缝隙可调节耦合强度。第二耦合线119由4段折线组成,与谐振器116组成容性阻抗的折线与谐振器116平行。

63.输入馈线113和输出馈线114均为50欧姆传输线。

64.第一硅基板10的上表面的第一金属层上还设有贯穿上下表面的金属化通孔,图2中未示出,可参照图1。图2中的第一区域10内的空白区域为高阻硅基,第一区域10内的二阶滤波器、第一u型耦合线111、第二u型耦合线112、输入馈线113和输出馈线114为在第一区域10内的高阻硅上制备的。第一区域10外的为第一金属层。

65.如图3所示,第一硅基板10的下表面均布设有接地金属,保证了良好的屏蔽特性。

66.如图4所示,在第二硅基板20的上表面的第二区域213内设有第一抑制谐振杆210

和第二抑制谐振杆211。在第二硅基板20对应输入馈线113和输出馈线114的位置上,设有两个凹槽212,可使第一硅基板10上的输入馈线113和输出馈线114裸露在外表面,便于连接。

67.第一抑制谐振杆210和第二抑制谐振杆211分别位于第一u型耦合线111和第二u型耦合线112的垂直正上方。第一u型耦合线111和第二u型耦合线112的开口方向分别为第一抑制谐振杆和第二抑制谐振杆的长度方向。第一抑制谐振杆210和第二抑制谐振杆211均为单端短路的1/4波长谐振器。可以通过调节其长度,灵活调节传输零点的位置。第一u型耦合线111任一边的线宽设置为第一抑制谐振杆210的宽度的1/3,第一u型耦合线111的间隔也为第一抑制谐振杆210的宽度的1/3,使得第一抑制谐振杆210的宽度等于第一u型耦合线111的宽度与第一u型耦合线111的间隔之和。相应的,第二u型耦合线112任一边的线宽设置为第二抑制谐振杆211的宽度的1/3,第二u型耦合线112的间隔也为第二抑制谐振杆211的宽度的1/3,使得第二抑制谐振杆211的宽度等于第二u型耦合线112的宽度与第二u型耦合线112的间隔之和。第一抑制谐振杆210的长度可以大于第二抑制谐振杆211的长度。

68.第一抑制谐振杆210和第一u型耦合线111、第二抑制谐振杆211和第二u型耦合线112形成两组非谐振节点。

69.微波输入信号经过输入馈线113馈入,经过第一u型耦合线111到达z型耦合线118、谐振器115、谐振器116和第二耦合线119处,谐振器115和谐振器116形成二阶滤波器,并对通带频率内信号提供传输特性,并在阻带内提供衰减特性。然后经过第二u型耦合线112,最后通过输出馈线114将通带频率内信号传输出去。第一抑制谐振杆210和第二抑制谐振杆211分别位于第一u型耦合线111和第二u型耦合线112的垂直方向,在带外产生传输零点,从而提高了矩形系数。

70.本发明提供的含有非谐振节点(nrn)结构的多零点硅基mems滤波器,采用mems工艺在双层高阻硅上实现了还有非谐振节点的滤波器。主要的传输电路在第一硅基板10和第二硅基板20之间,具有良好的屏蔽特性,且易于集成。底层的第一硅基板10采用薄硅,可以增加电容进一步缩小尺寸。第二硅基板20上的抑制谐振杆在通带外增加了两个传输零点,提高了滤波器的矩形系数。从而可以使滤波器具有尺寸小、高矩形系数、屏蔽性好,且易于集成。

71.以上所述实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1