半导体结构及其制备方法与流程

本发明属于集成电路设计及制造,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、在现有技术中,随着工艺的发展,3d nand(三维存储器)中的叠层结构的牺牲层及栅间介质层层数越来越多,对于包括层数较多的所述叠层结构的三维存储而言,由于在所述叠层结构的核心区域(core区域)及台阶区域形成的沟道通孔的密度不同(譬如,所述核心区域为9排沟道通孔的排列方式,所述沟道通孔的密度较大,而所述台阶区域为3排沟道通孔的排列方式,所述沟道通孔的密度较小),这会导致在核心区域及台阶区域的交界处(即所述沟槽通孔的密度不同的两个区域的交界处)存在局部应力差;又所述叠层结构中的所述牺牲层一般为氮化硅层,所述栅间介质层一般为氧化硅层,所述氮化硅层中的si-n键的键能低于si-o键的键能,在所述核心区域与所述台阶区域交界处的所述氮化硅层中的si-n键长被拉更长,键长被拉长的si-n键更容易在采用干法刻蚀工艺形成栅极间隙时被刻蚀机台上电极产生并加速的正离子打断并反应,从而在所述核心区域与所述台阶区域交界处造成损伤而形成栅极间隙向所述沟道通孔方向的凸起(即所述核心区域与所述台阶区域交界处的所述栅极间隙向所述沟道通孔方向延伸);随着栅极间隙深度的增加,所述核心区域与所述台阶区域交界处的所述损伤越明显,甚至会使得栅极间隙延伸至沟道通孔内;又沟道通孔内形成有功能侧壁及沟道层,若栅极间隙延伸至沟道通孔内,在栅极间隙内填充形成共源线后很容易造成漏电的问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种半导体结构及其制备方法,用于解决现有技术中的上述问题。

2、为实现上述目的及其他相关目的,本发明提供一种半导体结构的制备方法,所述半导体结构的制备方法包括如下步骤:

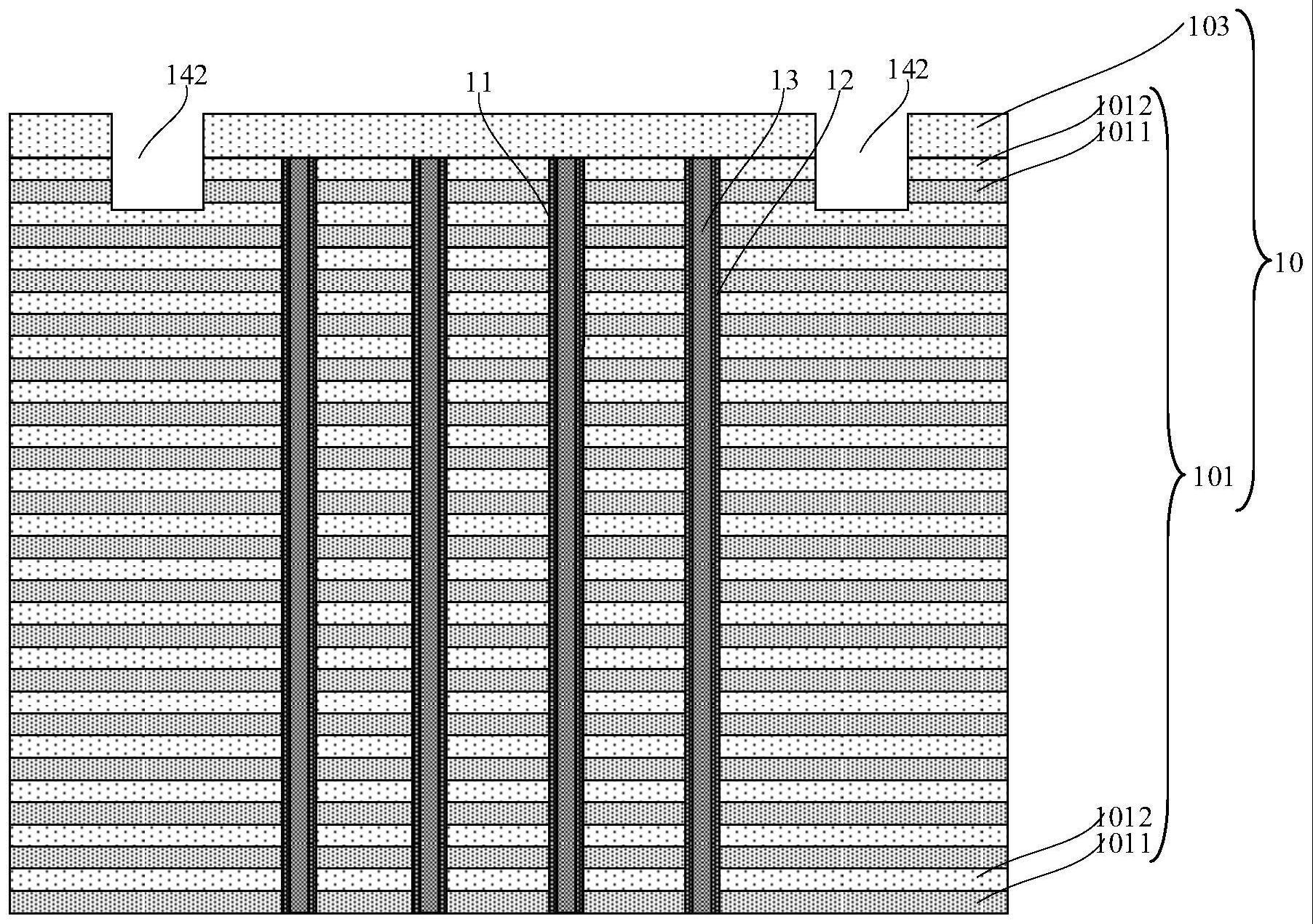

3、形成结构层,所述结构层包括第一区域及第二区域;所述结构层内形成有沟道通孔,所述沟道通孔位于所述第一区域及所述第二区域内,且所述第一区域内所述沟道通孔的密度大于所述第二区域内所述沟道通孔的密度;及

4、于所述结构层内形成栅极间隙,所述栅极间隙包括第一沟槽、第二沟槽及第三沟槽;其中,所述第一沟槽位于所述第一区域内,所述第三沟槽位于所述第二区域内,所述第二沟槽位于所述第一区域与所述第二区域的交界处,一端与所述第一沟槽相连接,另一端与所述第三沟槽相连接,所述第二沟槽的深度小于所述第一沟槽的深度及所述第三沟槽的深度。

5、上述实施例中形成的半导体结构中,所述栅极间隙位于所述沟道通孔密度不同的所述第一区域及所述第二区域的交界处的所述第二沟槽深度小于位于所述第一区域及所述第二区域的所述第一沟槽及所述第三沟槽的深度,所述第一区域及所述第二区域的交界处没有深度较大的沟槽,可以避免由于所述第一区域与所述第二区域的交界处存在应力差而导致的所述栅极间隙向所述沟道通孔延伸,从而避免在对栅极间隙填充后造成漏电。

6、可选地,形成所述结构层包括如下步骤:

7、形成包括依次交替叠置的牺牲层及栅间介质层的叠层结构,所述叠层结构包括核心区域及位于所述叠层结构边缘的台阶区域,其中,所述核心区域为所述第一区域,所述台阶区域为所述第二区域;

8、于所述叠层结构内形成所述沟道通孔,所述沟道通孔沿厚度方向贯穿所述叠层结构;及

9、于所述叠层结构的上表面形成覆盖介质层。

10、可选地,于所述叠层结构的上表面形成所述覆盖介质层之前还包括如下步骤:

11、于所述沟道通孔内形成功能侧壁;及

12、于所述功能侧壁的表面形成沟道层。

13、可选地,所述牺牲层包括氮化硅层,所述栅间介质层包括氧化硅层。

14、可选地,于所述叠层结构内形成所述栅极间隙包括如下步骤:

15、于所述第一区域内形成所述第一沟槽,并于所述第二区域内形成所述第三沟槽;所述第一沟槽及所述第三沟槽均沿厚度方向贯穿所述覆盖介质层及所述叠层结构;及

16、于所述结构层内形成第二沟槽,所述第二沟槽沿厚度方向贯穿所述覆盖介质层以暴露出所述叠层结构。

17、可选地,形成所述栅极间隙之后还包括于所述栅极间隙内形成共源线的步骤。

18、可选地,于所述栅极间隙内形成所述共源线之前还包括于所述栅极间隙的侧壁形成绝缘隔离层的步骤。

19、可选地,于所述栅极间隙的侧壁形成所述绝缘隔离层之前还包括如下步骤:

20、基于所述栅极间隙去除所述牺牲层,以形成牺牲间隙;及

21、于所述牺牲间隙内形成栅极层。

22、可选地,于所述结构层内形成所述第二沟槽之前还包括如下步骤:

23、基于所述第一沟槽及所述第三沟槽去除所述牺牲层,以形成牺牲间隙;

24、于所述牺牲间隙内形成栅极层;及

25、于所述第一沟槽及所述第三沟槽内形成第一导电层。

26、可选地,形成所述第二沟槽之后还包括于所述第二沟槽内形成第二导电层的步骤,所述第二导电层与位于所述第一沟槽及所述第三沟槽内的所述第一导电层均相连接,以形成共源线。

27、可选地,于所述第一沟槽及所述第三沟槽内形成所述第一导电层之前包括于所述第一沟槽的侧壁及所述第三沟槽的侧壁形成第一绝缘隔离层的步骤;于所述第二沟槽内形成所述第二导电层之前还包括于所述第二沟槽的侧壁形成第二绝缘隔离层的步骤。

28、本发明还提供一种半导体结构,所述半导体结构包括:

29、结构层,所述结构层包括第一区域及第二区域;

30、沟道通孔,位于所述第一区域及所述第二区域内,且所述第一区域内所述沟道通孔的密度大于所述第二区域内所述沟道通孔的密度;及

31、栅极间隙,位于所述结构层内;所述栅极间隙包括第一沟槽、第二沟槽及第三沟槽,所述第一沟槽位于所述第一区域内,所述第三沟槽位于所述第二区域内,所述第二沟槽位于所述第一区域与所述第二区域的交界处,一端与所述第一沟槽相连接,另一端与所述第三沟槽相连接,所述第二沟槽的深度小于所述第一沟槽的深度及所述第三沟槽的深度。

32、上述实施例中的半导体结构中,所述栅极间隙位于所述沟道通孔密度不同的所述第一区域及所述第二区域的交界处的所述第二沟槽深度小于位于所述第一区域及所述第二区域的所述第一沟槽及所述第三沟槽的深度,所述第一区域及所述第二区域的交界处没有深度较大的沟槽,可以避免由于所述第一区域与所述第二区域的交界处存在应力差而导致的所述栅极间隙向所述沟道通孔延伸,从而避免在对栅极间隙填充后造成漏电。

33、可选地,所述半导体结构还包括:

34、功能侧壁,位于所述沟道通孔内;及

35、沟道层,位于所述功能侧壁的表面。

36、可选地,所述半导体结构还包括共源线,所述共源线位于所述栅极间隙内。

37、可选地,所述半导体结构还包括绝缘隔离层,所述绝缘隔离层位于所述栅极间隙的侧壁,且位于所述共源线与所述结构层之间。

38、可选地,所述结构层包括:

39、叠层结构,所述叠层结构包括依次交替叠置的牺牲层及栅间介质层,所述叠层结构包括核心区域及位于所述叠层结构边缘的台阶区域,其中,所述核心区域为所述第一区域,所述台阶区域为所述第二区域;所述沟道通孔位于所述叠层结构内,且沿厚度方向贯穿所述叠层结构;及

40、覆盖介质层,位于所述叠层结构的上表面;

41、所述第一沟槽及所述第三沟槽均沿厚度方向贯穿所述覆盖介质层及所述叠层结构;所述第二沟槽沿厚度方向贯穿所述覆盖介质层以暴露出所述叠层结构。

42、可选地,所述牺牲层包括氮化硅层,所述栅间介质层包括氧化硅层。

43、可选地,所述结构层包括:

44、叠层结构,所述叠层结构包括依次交替叠置的栅极层及栅间介质层,所述叠层结构包括核心区域及位于所述叠层结构边缘的台阶区域,其中,所述核心区域为所述第一区域,所述台阶区域为所述第二区域;所述沟道通孔位于所述叠层结构内,且沿厚度方向贯穿所述叠层结构;及

45、覆盖介质层,位于所述叠层结构的上表面;

46、所述第一沟槽及所述第三沟槽均沿厚度方向贯穿所述覆盖介质层及所述叠层结构;所述第二沟槽沿厚度方向贯穿所述覆盖介质层以暴露出所述叠层结构。

- 还没有人留言评论。精彩留言会获得点赞!