半导体产品封装结构和方法与流程

本发明涉及半导体集成电路领域,特别是涉及一种半导体产品封装结构。本发明还涉及一种半导体产品封装方法。

背景技术:

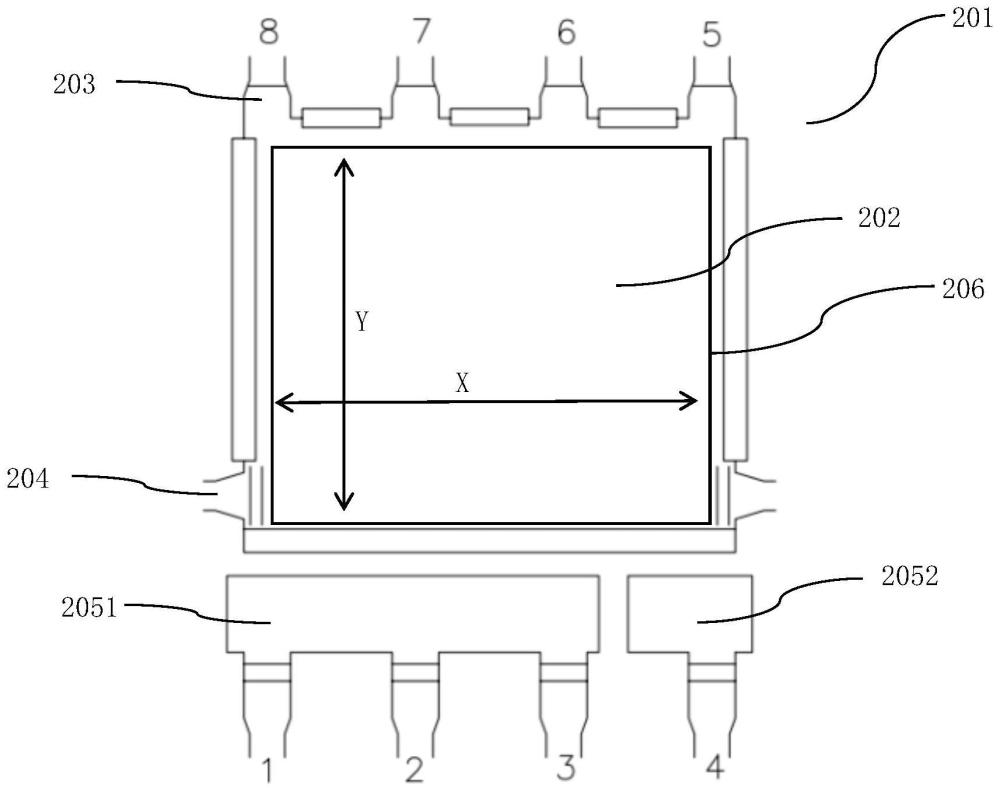

1、如图1所示,是现有半导体产品封装结构的芯片安装单元101的结构示意图。现有半导体产品封装结构包括:

2、引线框架,包括多个芯片安装单元101,各所述芯片安装单元101包括载片岛102,所述载片岛102用于承载半导体产品芯片。

3、通常,所述半导体产品芯片为mosfet芯片产品。

4、所述引线框架采用双侧无引脚扁平封装(dual flat non-lead package,dfn)5*6结构。dfn5*6又通常采用塑料双侧无引脚扁平封装(plastic dual flat non-leadpackage,pdfn)5*6。pdfn5*6结构中,所述引线框架中通常包括12*40个所述芯片安装单元101,所述芯片安装单元101排列形成的阵列结构为12行和40列,每相邻的两列所述芯片安装单元101组成一个列组合结构,各所述列组合结构重复排列形成所述芯片安装单元101。

5、所述芯片安装单元101还包括8个引脚103和2个引脚焊接区。

6、8个所述引脚103还分别用编号1-8标出。2个所述引脚焊接区分别用标记1051和1052标出。

7、编号5至8对应的4个所述引脚103位于所述芯片安装单元101的顶部。

8、2个所述引脚焊接区都位于所述芯片安装单元101的底部。

9、一个所述引脚焊接区1051的底部连接有编号1至3对应的3个所述引脚103,另一个所述引脚焊接区1052的底部连接有编号4对应的所述引脚103。

10、在所述芯片安装单元101的左右两侧个设置有一个支撑连筋104。

11、图1所示的现有半导体产品封装结构的芯片安装单元101的所述载片岛102的尺寸相对偏小,能够封装的mosfet产品芯片尺寸也就相对偏小,限制了pdfn5*6能够封装mosfet产品的能力,不利于产品扩展和成本效应。

技术实现思路

1、本发明所要解决的技术问题是提供一种半导体产品封装结构,能提高对较大尺寸的半导体芯片产品进行封装的能力,同时能确保产品质量,使产品应力以及防水汽能力满足要求以及使产品具有低导通电阻特性和表面贴装器件特性。为此,本发明还提供一种半导体产品封装方法。

2、为解决上述技术问题,本发明提供的半导体产品封装结构包括:

3、引线框架,包括多个芯片安装单元,各所述芯片安装单元包括载片岛,所述载片岛用于承载半导体产品芯片。

4、所述载片岛具有最大面积结构并在所述载片岛的周侧边缘设置有一圈由凹槽组成的防水结构。

5、所述载片岛的面积是以所述引线框架形成的塑封体的有效尺寸为基准进行计算和仿真得到的所述载片岛所能得到的最大面积,通过采用所述最大面积结构,使所述载片岛能封装的所述半导体产品芯片的面积增加。

6、进一步的改进是,所述半导体产品芯片为mosfet芯片产品。

7、进一步的改进是,所述防水结构的所述凹槽为v型槽。

8、进一步的改进是,所述引线框架采用dfn5*6结构。

9、进一步的改进是,所述引线框架采用pdfn5*6结构。

10、进一步的改进是,所述芯片安装单元还包括8个引脚和2个引脚焊接区;

11、4个所述引脚位于所述芯片安装单元的顶部;

12、2个所述引脚焊接区都位于所述芯片安装单元的底部;

13、一个所述引脚焊接区的底部连接有3个所述引脚,另一个所述引脚焊接区的底部连接有一个所述引脚;

14、在所述芯片安装单元的左右两侧个设置有一个支撑连筋。

15、进一步的改进是,所述载片岛俯视面呈方形,通过对xy方向的尺寸进行扩展形成所述最大面积结构。

16、为解决上述技术问题,本发明提供的半导体产品封装方法包括如下步骤:

17、步骤一、以引线框架形成的塑封体的有效尺寸为基准进行计算和仿真得到的所述载片岛所能得到的最大面积。

18、步骤二、形成所述引线框架,所述引线框架包括多个芯片安装单元,各所述芯片安装单元包括所述载片岛,所述载片岛用于承载半导体产品芯片。

19、将所述载片岛设置为最大面积结构并在所述载片岛的周侧边缘设置有一圈由凹槽组成的防水结构;通过采用所述最大面积结构,使所述载片岛能封装的所述半导体产品芯片的面积增加。

20、进一步的改进是,所述半导体产品芯片为mosfet芯片产品。

21、进一步的改进是,所述防水结构的所述凹槽为v型槽。

22、进一步的改进是,所述引线框架采用dfn5*6结构。

23、进一步的改进是,所述引线框架采用pdfn5*6结构。

24、进一步的改进是,所述芯片安装单元还包括8个引脚和2个引脚焊接区;

25、4个所述引脚位于所述芯片安装单元的顶部;

26、2个所述引脚焊接区都位于所述芯片安装单元的底部;

27、一个所述引脚焊接区的底部连接有3个所述引脚,另一个所述引脚焊接区的底部连接有一个所述引脚;

28、在所述芯片安装单元的左右两侧个设置有一个支撑连筋。

29、进一步的改进是,所述载片岛俯视面呈方形,通过对xy方向的尺寸进行扩展形成所述最大面积结构。

30、进一步的改进是,还包括:

31、步骤三、进行装片(die bond,db)工艺将所述半导体产品芯片承载在所述载片岛上;

32、步骤四、进行塑封(molding)工艺将所述引线框架塑封形成所述塑封体。

33、本发明通过将载片岛设置为最大面积结构以及同时设置凹槽组成的防水结构,能提高对较大尺寸的半导体芯片产品进行封装的能力并从而能实现对大尺寸的半导体芯片产品的封装,同时能确保产品质量,其中凹槽的防水结构能改善产品应力以及能提升塑封材料如环氧塑封材料(emc)和引线框架的结合力从而能提高防水汽能力,较大的载片岛面积能确保产品具有低导通电阻(rdson)特性和表面贴装器件特性。

34、本发明的引线框架的整体外形尺寸不需要改变即可实现,所以本发明能利用现有的封装生产线设备实现了芯片尺寸较大的半导体产品如mosfet产品封装制造,在确保产品质量的前提下扩展了引线框架如pdfn5*6的封装(pkg)的适用范围。

技术特征:

1.一种半导体产品封装结构,其特征在于,包括:

2.如权利要求1所述的半导体产品封装结构,其特征在于:所述半导体产品芯片为mosfet芯片产品。

3.如权利要求1所述的半导体产品封装结构,其特征在于:所述防水结构的所述凹槽为v型槽。

4.如权利要求1所述的半导体产品封装结构,其特征在于:所述引线框架采用dfn5*6结构。

5.如权利要求4所述的半导体产品封装结构,其特征在于:所述引线框架采用pdfn5*6结构。

6.如权利要求5所述的半导体产品封装结构,其特征在于:所述芯片安装单元还包括8个引脚和2个引脚焊接区;

7.如权利要求1所述的半导体产品封装结构,其特征在于:所述载片岛俯视面呈方形,通过对xy方向的尺寸进行扩展形成所述最大面积结构。

8.一种半导体产品封装方法,其特征在于,包括如下步骤:

9.如权利要求8所述的半导体产品封装方法,其特征在于:所述半导体产品芯片为mosfet芯片产品。

10.如权利要求8所述的半导体产品封装方法,其特征在于:所述防水结构的所述凹槽为v型槽。

11.如权利要求8所述的半导体产品封装方法,其特征在于:所述引线框架采用dfn5*6结构。

12.如权利要求11所述的半导体产品封装方法,其特征在于:所述引线框架采用pdfn5*6结构。

13.如权利要求12所述的半导体产品封装方法,其特征在于:所述芯片安装单元还包括8个引脚和2个引脚焊接区;

14.如权利要求8所述的半导体产品封装方法,其特征在于:所述载片岛俯视面呈方形,通过对xy方向的尺寸进行扩展形成所述最大面积结构。

15.如权利要求8所述的半导体产品封装方法,其特征在于,还包括:

技术总结

本发明公开了一种半导体产品封装结构,包括:引线框架,包括多个芯片安装单元,各芯片安装单元包括载片岛,载片岛用于承载半导体产品芯片。载片岛具有最大面积结构并在周侧边缘设置有一圈由凹槽组成的防水结构。载片岛的面积是以引线框架形成的塑封体的有效尺寸为基准进行计算和仿真得到的载片岛所能得到的最大面积,通过采用最大面积结构,使载片岛能封装的半导体产品芯片的面积增加。本发明还公开了一种半导体产品封装方法。本发明能提高对较大尺寸的半导体芯片产品进行封装的能力,同时能确保产品质量,使产品应力以及防水汽能力满足要求以及使产品具有低导通电阻特性和表面贴装器件特性。

技术研发人员:田茂康

受保护的技术使用者:南通尚阳通集成电路有限公司

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!