一种可提升OLED存储电容的阵列基板及其制造方法与流程

一种可提升oled存储电容的阵列基板及其制造方法

技术领域

1.本发明属于显示技术领域,具体是指一种可提升oled存储电容的阵列基板及其制造方法。

背景技术:

2.目前非晶态金属氧化物半导体发展迅速。其中,非晶ingazno(igzo)凭借其简单的制备工艺以及优异的光电学性能而成为tft制备的理想材料,以其制备的tft有着高迁移率、高开关比等特点,具有替代a-si的潜力。较a-sitft相比,igzo-tft的载流子迁移率可以达到10~30cm2/v

·

s,大大提高tft对像素电极的充放电效率和响应速度。更为重要的是,igzo制程和现有的a-si生产线具有很好的兼容性,较生产工艺更为复杂、设备投资更高的低温多晶硅(ltps)具有更低的投资成本。

3.有源矩阵有机发光二极管amoled因其具有高响应、高对比度及低功耗等优点被认为是下一代主流的显示技术。amoled作为电流驱动器件,以常见的2t1c为例,由开关tft、驱动tft和电容共同构成像素电路,其中,开关tft主要是控制数据输入信号,驱动tft主要是为oled提供电流。因为电流不可稳定储存,而电压可以用电容暂时储存,故驱动tft的栅极电压是被电容cs保持,若无此cs电容,驱动tft的栅极电压会很容易漂移。现有的amoled显示屏为了保证画质的均一性,开发了驱动补偿电路技术,故pixel显示由多颗tft和电容共同控制。随着对屏幕分辨率的要求越来越高,像素的尺寸越来越小,故如何优化补偿电路器件设计尺寸、电路排布将尤为重要。并且补偿电路的设计越复杂,为了在有限空间内设计更多的tft,pixel内部电容的空间就相对越狭小。

4.因此,提供一种可以优化电容尺寸及容量的设计,可以有效的避免为设计高分辨率结构而无法保证阈值电压漂移的问题。

技术实现要素:

5.本发明所要解决的技术问题在于提供一种可提升oled存储电容的阵列基板及其制造方法。

6.本发明是这样实现的:

7.一种可提升oled存储电容的阵列基板,包括:玻璃基板和设在所述玻璃基板上的缓冲层,

8.所述缓冲层在电容区域的部分横向和纵向上均开设有多个凹槽;所述凹槽内依次填充有第一金属层、栅级绝缘层、刻蚀阻挡层、第二金属层;

9.所述缓冲层在tft区域上依次层叠有所述第一金属层、所述栅级绝缘层、有源层、所述刻蚀阻挡层、所述第二金属层;tft区域的所述刻蚀阻挡层上具有多个开孔,使得所述有源层和所述第二金属层相连接;tft区域的的所述第二金属层pattern形成源漏极。

10.进一步地,所述凹槽中的第一金属层与所述玻璃基板接触。

11.进一步地,所述凹槽在横向和纵向上的竖直截面形状均为倒梯形。

12.进一步地,所述第一金属层和所述第二金属层,均为mo/al/mo。

13.进一步地,所述有源层,为igzo。

14.一种可提升oled存储电容的阵列基板的制造方法,包括如下步骤:

15.步骤s1:提供一玻璃基板,在所述玻璃基板表面覆盖有缓冲层,所述缓冲层在电容区域的部分横向和纵向上均开设多个凹槽;

16.步骤s2:形成第一金属层;所述第一金属层填充于电容区域的所述凹槽内,所述第一金属层覆盖于tft区域的缓冲层表面;

17.步骤s3:形成栅极绝缘层,所述栅极绝缘层覆盖于所述第一金属层表面;

18.步骤s4:在tft区域的栅极绝缘层表面形成有源层;

19.步骤s5:形成刻蚀阻挡层,电容区域的刻蚀阻挡层覆盖于栅级绝缘层上表面,tft区域的刻蚀阻挡层覆盖于栅级绝缘层和有源层的上表面;tft区域的刻蚀阻挡层形成多个开孔;

20.步骤s6:形成第二金属层,电容区域的第二金属层覆盖于刻蚀阻挡层es上表面,tft区域的第二金属层上pattern形成源漏极。

21.进一步地,所述凹槽中的第一金属层与所述玻璃基板接触。

22.进一步地,所述凹槽在横向和纵向上的竖直截面形状均为倒梯形。

23.进一步地,所述第一金属层和所述第二金属层,均为mo/al/mo。

24.进一步地,所述有源层se,为igzo。

25.本发明的优点在于:通过在玻璃基板上电容区域设计一层带有凹槽设计的缓冲层,根据电容的面积大小设置开凹槽数量,在保持间距d不变的情况下,增加了电容的面积,以此来提高电容的容量,若在等效的电容下,此设计方案的像素尺寸可以做的更小,补偿电路设计可以更加复杂,驱动tft的阈值电压会更为稳定,可以有效的避免为设计高分辨率结构而无法保证阈值电压漂移的问题。

附图说明

26.下面参照附图结合实施例对本发明作进一步的描述。

27.图1是现有技术的阵列基板俯视平面图。

28.图2是本发明的阵列基板俯视平面图。

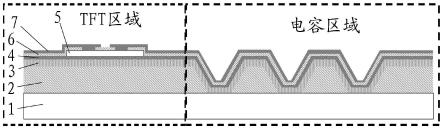

29.图3是图2中的a-a'剖视图。

30.图4是图2中的b-b'剖视图。

31.图5是本发明中的其中一凹槽的俯视平面图。

具体实施方式

32.如图2至图5所示,一种可提升oled存储电容的阵列基板,包括:玻璃基板1和设在玻璃基板1上的缓冲层2,缓冲层2在电容区域的部分横向和纵向上均开设有多个凹槽(和图1对比可以看出,现有技术的图1中并未设计凹槽);凹槽内依次填充有第一金属层3、栅级绝缘层gi4、刻蚀阻挡层es6、第二金属层7;

33.缓冲层2在tft区域上依次层叠有第一金属层3、栅级绝缘层gi4、有源层se5、刻蚀阻挡层es6、第二金属层7;tft区域的刻蚀阻挡层es6上具有多个开孔,使得有源层se5和第

二金属层7相连接;tft区域的第二金属层7pattern形成源漏极。

34.凹槽中的第一金属层3和玻璃基板1接触。凹槽在横向和纵向上的竖直截面形状均为倒梯形。

35.其中:

36.缓冲层2:通常选用siox,不仅可应用于平坦化玻璃表面,且在特定区域形成对应的凹槽形状;

37.第一金属层3:在tft区域作为非透明栅极ge,在电容区域作为电容的第一是电极层,其可选用铝/钼/钛/镍/铜/等导电性优良金属以及合金,此处以mo/al/mo为例;

38.栅极绝缘层gi4:具有较大介电常数的绝缘层,此设计方案可选siox;

39.有源层se5:tft器件半导体层,如a-si、mox和ltps等,此设计方案可选igzo;

40.刻蚀阻挡层es6:具有较大介电常数的绝缘层,保护sechanel不被蚀刻液或气体蚀刻,此设计方案可选siox;

41.第二金属层7:在tft区域作为源漏极sd,在电容区域作为第二电极层,此处以mo/al/mo为例。

42.pattern:图案化,array主要的制程工艺为成膜/曝光/显影/蚀刻/剥膜。光阻显影后会形成相应的图案,蚀刻制程就会对没有光阻保护的膜层进行蚀刻,最终剥膜制程后就会保留最终设计的图案。

43.本发明还提供上述的一种可提升oled存储电容的阵列基板的制造方法,包括如下步骤:

44.步骤s1:提供一玻璃基板1,在所述玻璃基板1表面覆盖有缓冲层2,所述缓冲层2在电容区域的部分横向和纵向上均开设多个凹槽;

45.步骤s2:形成第一金属层3;所述第一金属层3填充于电容区域的所述凹槽内,所述第一金属层3覆盖于tft区域的缓冲层2表面;凹槽中的第一金属层3和玻璃基板1接触;凹槽在横向和纵向上的竖直截面形状均为倒梯形;

46.步骤s3:形成栅极绝缘层gi4,所述栅极绝缘层gi4覆盖于所述第一金属层3表面;

47.步骤s4:在tft区域的栅极绝缘层gi4表面形成有源层se5;

48.步骤s5:形成刻蚀阻挡层es6,电容区域的刻蚀阻挡层es6覆盖于栅级绝缘层gi4上表面,tft区域的刻蚀阻挡层es6覆盖于栅级绝缘层gi4和有源层se5的上表面;

49.步骤s6:形成第二金属层7,电容区域的第二金属层7覆盖于刻蚀阻挡层es6上表面,tft区域的的第二金属层7上pattern形成源漏极。

50.本发明通过在玻璃基板上电容区域设计一层带有凹槽设计的缓冲层,根据电容的面积大小设置开凹槽数量,在保持间距d不变的情况下,增加了电容的面积,以此来提高电容的容量,若在等效的电容下,此设计方案的像素尺寸可以做的更小,补偿电路设计可以更加复杂,驱动tft的阈值电压会更为稳定,可以有效的避免为设计高分辨率结构而无法保证阈值电压漂移的问题。

51.以上所述仅为本发明的较佳实施用例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换以及改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1