半导体器件及其形成方法与流程

本申请的实施例涉及半导体器件及其形成方法。

背景技术:

1、对包括智能手机、平板电脑、台式电脑、膝上型电脑和许多其它类型的电子器件在内的电子器件的计算能力的需求持续增大。半导体器件为这些电子器件提供计算能力。在半导体器件中增大计算能力的一种方法是增加半导体衬底的给定区域可以包括的晶体管和其它半导体器件部件的数量。

2、纳米结构晶体管可以帮助增大计算能力,因为纳米结构晶体管可以非常小并且可以具有优于传统晶体管的改善功能。纳米结构晶体管可以包括用作用于晶体管的沟道区域的多个半导体纳米结构(例如,纳米线、纳米片等)。源极区域和漏极区域可以耦合至纳米结构。可能难以形成具有期望特性的源极区域和漏极区域。

技术实现思路

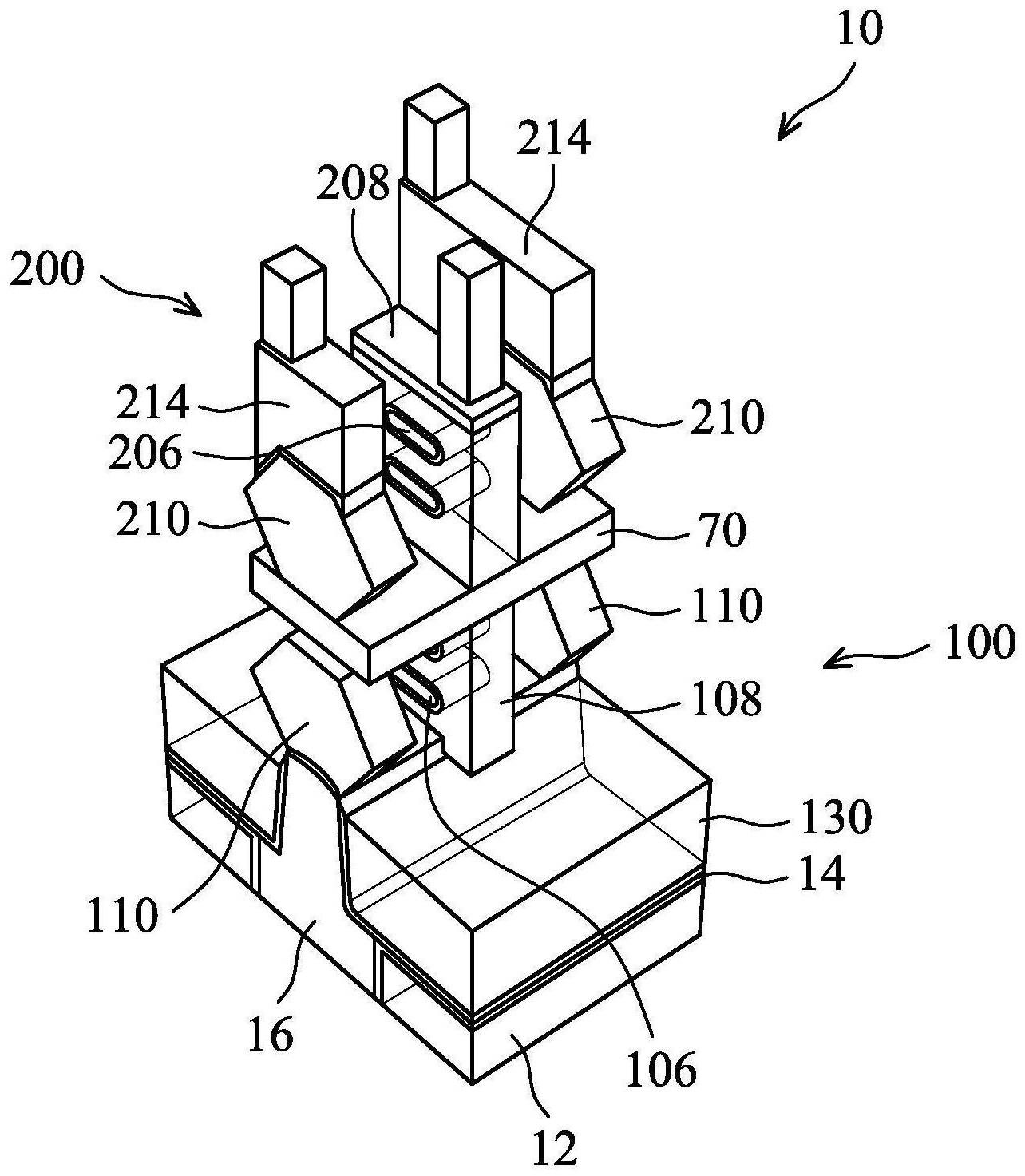

1、本申请的一些实施例提供了一种形成半导体器件的方法,包括:形成第一半导体器件的第一晶体管,形成所述第一晶体管包括:形成第一沟道区域;以及在所述第一沟道区域上形成第一栅电极;通过在所述第一半导体器件和所述第二半导体器件之间形成第一接合层将第二半导体器件接合至所述第一半导体器件;以及形成所述第二半导体器件的第二晶体管,形成所述第二晶体管包括:形成第二沟道区域;以及在所述第二沟道区域上形成第二栅电极,其中,所述第一接合层设置在所述第一晶体管的所述第一栅电极和所述第二晶体管的所述第二栅电极之间。

2、本申请的另一些实施例提供了一种形成半导体器件的方法,包括:在第一衬底上或中形成第一半导体器件,形成所述第一半导体器件包括:形成第一沟道区域;形成位于所述第一沟道区域上面的第一栅电极;以及形成与所述第一沟道区域接触的第一源极/漏极区域,所述第一源极/漏极区域沿第一方向与所述第一沟道区域相邻;在所述第一半导体器件上形成第一接合层;在第二衬底上形成第二接合层;将所述第一接合层和所述第二接合层彼此接合;以及在所述第二衬底上或中形成第二半导体器件,形成所述第二半导体器件包括:形成第二沟道区域;形成位于所述第二沟道区域上面的第二栅电极;以及形成与所述第二沟道区域接触的第二源极/漏极区域,所述第二源极/漏极区域沿所述第一方向与所述第二沟道区域相邻。

3、本申请的又一些实施例提供了一种半导体器件,包括:衬底;第一晶体管,位于所述衬底上,所述第一晶体管包括:第一沟道区域;第一栅电极,位于所述第一沟道区域上面;以及第一源极/漏极区域,与所述第一沟道区域接触,所述第一源极/漏极区域沿第一方向与所述第一沟道区域相邻;绝缘层,位于所述第一晶体管上;以及第二晶体管,位于所述绝缘层上,所述第二晶体管包括:第二沟道区域;第二栅电极,位于所述第二沟道区域上面;以及第二源极/漏极区域,与所述第二沟道区域接触,所述第二源极/漏极区域沿所述第一方向与所述第二沟道区域相邻。

技术特征:

1.一种形成半导体器件的方法,包括:

2.根据权利要求1所述的方法,其中,形成所述第一沟道区域包括形成具有第一导电类型的所述第一沟道区域,并且其中,形成所述第二沟道区域包括形成具有与所述第一导电类型不同的第二导电类型的所述第二沟道区域。

3.根据权利要求1所述的方法,其中,形成所述第一沟道区域包括形成具有沿第一方向彼此横向间隔开的多个鳍结构的所述第一沟道区域,并且其中,形成所述第二沟道区域包括形成具有沿横向于所述第一方向的第二方向彼此间隔开的多个纳米结构的所述第二沟道区域。

4.根据权利要求1所述的方法,其中,形成所述第一晶体管或所述第二晶体管中的一个包括通过从所述第一沟道区域或所述第二沟道区域中的一个外延生长来形成外延源极/漏极区域,至少一空隙设置在所述第一接合层和所述外延源极/漏极区域之间。

5.根据权利要求1所述的方法,其中,形成所述第二沟道区域包括形成与所述第一沟道区域不同材料的所述第二沟道区域,并且其中,形成所述第一沟道区域包括形成硅锗区域,并且形成所述第二沟道区域包括形成硅区域。

6.根据权利要求1所述的方法,包括:

7.根据权利要求6所述的方法,其中,形成所述第一接合层和形成所述第二接合层包括形成包括sio、sioc、siocn、sin、sion、aln、bn、sic、金刚石或beo中的至少一种的所述第一接合层和所述第二接合层。

8.根据权利要求6所述的方法,其中,形成所述第一接合层和形成所述第二接合层包括形成具有小于50nm的厚度的所述第一接合层或所述第二接合层中的至少一个。

9.一种形成半导体器件的方法,包括:

10.一种半导体器件,包括:

技术总结

方法包括形成第一半导体器件的第一晶体管。第一半导体器件包括第一沟道区域以及位于第一沟道区域上的栅电极。第二半导体器件通过设置在第一半导体器件和第二半导体器件之间的接合层而接合至第一半导体器件。形成第二半导体器件的第二晶体管,第二半导体器件包括第二沟道区域以及位于第二沟道区域上的第二栅电极。接合层设置在第一晶体管的第一栅电极和第二晶体管的第二栅电极之间。本申请的实施例还涉及半导体器件及其形成方法。

技术研发人员:黄瑞乾,廖思雅,王振印,王世豪

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!