一种提高发光效率的LED外延结构及制备方法与流程

一种提高发光效率的led外延结构及制备方法

技术领域

1.本发明涉及一种提高发光效率的led外延结构及制备方法,属于led外延结构技术领域。

背景技术:

2.发光二极管(led,light emitting diode)是一种能发光的半导体电子元件。近年来led因其具有耗电低、寿命长、体积小、节能环保等优点得到了广泛的应用,可以应用于室内外照明、交通灯、背光源等领域。其中iii-v族as,p化物在电学、光学领域受到广泛的关注与应用,但现实应用中由于材料、结构以及工艺的限制,各类新兴led产品大规模应用依旧存在电子束缚不足导致的溢流严重,空穴注入效率低限制了发光效率的进一步提升等一系列问题;这些都阻碍了载流子在有源区的高效复合,为了led大规模商业化,减小电子泄露、增加空穴注入效率、促进载流子在有源区的高效复合,成为提升led发光效率的关键所在。

3.目前,为了减少电子泄露,通常在在p型半导体层的一侧利用algainp组分构成电子阻挡层。然而,上述algainp组分的电子阻挡层,增加电子阻挡的同时,也阻挡了空穴注入;同时,还会面临一些其它问题,如与邻近层的晶格失配带来晶体质量下降,无法形成一个良好的界面。为此,提出本发明。

技术实现要素:

4.针对现有技术的不足,本发明提供一种提高发光效率的led外延结构,增加空穴在靠近量子阱区域的储存,避免电子与空穴在非复合量子阱区域发生复合发光,从而提升led的发光效率。

5.本发明的技术方案如下:

6.一种提高发光效率的led外延结构,包括从下到上依次设置的衬底、缓冲层、n型半导体层、复合量子阱层、边缘量子垒层、电子阻挡层和p型半导体层,其中,

7.复合量子阱层包括交替设置的量子垒和量子阱,生长方向为沿着衬底垂直指向于n型半导体层,电子阻挡层的势垒高度高于边缘量子垒层的势垒高度,使边缘量子垒层在复合量子阱层和电子阻挡层之间形成空穴存储区和电子阻挡区域。

8.优选的,量子垒包括algainp层,量子阱包括gainp层,边缘量子垒层包括若干个al

x

gayinzp层。

9.进一步优选的,al

x

gayinzp层中,0≤x≤1,0≤y≤1,0≤z≤1,x+y+z=1。

10.优选的,边缘量子垒层若干个al

x

gayinzp层中,x由复合量子阱层指向电子阻挡层的方向递减,y、z由复合量子阱层指向电子阻挡层的方向递增。

11.优选的,边缘量子垒层包括p型掺杂的al

x

gayinzp层和非掺杂的al

x

gayinzp层,其中,靠近电子阻挡层的al

x

gayinzp层为p型掺杂的al

x

gayinzp层,使其在避免电子与空穴在非复合量子阱区域进行复合发光的同时,通过p型掺杂提供更多的空穴,进一步增加空穴在靠近复合量子阱区域的储存及迁移能力,从而提高led发光效率,其余为非掺杂的al

x

gayinzp

层。

12.优选的,电子阻挡层为alagabincp层和al

x

gayinzp层交替堆叠的超晶格结构,其中,0≤a≤1,0≤b≤1,0≤c≤1,a+b+c=1,且x≤a。

13.优选的,衬底为蓝宝石、sic、si、algainp、gaas中的任意一种。

14.优选的,缓冲层为n型掺杂的gaas缓冲层,n型半导体层为alinp层。

15.上述提高发光效率的led外延结构的制备方法,步骤如下:

16.(1)将衬底放入mocvd反应室中,温度环境为850℃左右,通入ash3源,进行5分钟左右的预处理,然后降温至720℃左右,通入ga源,生长n型掺杂的gaas缓冲层;

17.(2)关闭ash3源和ga源,通入al、in源和ph3,环境温度为750℃,生长alinp层,得到n型半导体层;

18.(3)关闭掺杂源,持续通入al,ga源和in源,生长algainp量子垒,接着关闭al源,生长gainp量子阱,重复生长10~15周期,构成复合量子阱层;

19.(4)通入al源,并调节铝组分,生长al

x

gayinzp层,靠近复合量子阱层一侧的al

x

gayinzp层中铝组分最大,最顶层的al

x

gayinzp层中铝组分最小,同时,在最顶层的al

x

gayinzp层中通入p型掺杂源,构成边缘量子垒层;

20.(5)关闭p型掺杂源,并调整铝组分,生长交替堆叠的alagabincp层和al

x

gayinzp层,构成电子阻挡层;

21.(6)将温度调整至750℃,关闭ga源,通入cp2mg,生长p型alinp层,掺杂浓度为0.5*10

18

cm-3-1*10

18

cm-3

,得到p型半导体层。

22.优选的,步骤(1)中,gaas缓冲层生长厚度为10nm,步骤(2)中alinp层生长厚度为30nm左右,步骤(3)中algainp量子垒生长厚度为10nm,gainp量子阱生长厚度为10nm,步骤(6)中p型alinp层生长厚度为30nm。

23.本发明的有益效果在于:

24.1、本发明提供的外延结构,在复合量子阱层和电子阻挡层中间生长一个边缘量子垒层,且电子阻挡层的势垒高度需高于边缘量子垒层的势垒高度,使边缘量子垒层在复合量子阱层和电子阻挡层之间形成空穴存储区及电子阻挡区域,以避免电子与空穴在非复合量子阱区域发生复合发光。

25.2、本发明在边缘量子垒层的若干个al

x

gayinzp层中,铝组分随复合量子阱层指向电子阻挡层的方向降低,使靠近复合量子阱层一侧具有较高的势垒高度,对n型半导体层的电子注入起到阻挡作用,避免其进入非复合量子阱区域;而所述电子阻挡层(即p型半导体层侧)具有较低的势垒高度,如此也不会导致空穴难以注入复合量子阱区域。

26.3、本发明在边缘量子垒层的若干个al

x

gayinzp层中,靠近电子阻挡层的al

x

gayinzp层存在p型掺杂,使其在避免电子与空穴在非复合量子阱区域进行复合发光的同时,通过p型掺杂可提供更多的空穴,进一步增加空穴在靠近复合量子阱区域的储存及迁移能力,从而提高led发光效率。

附图说明

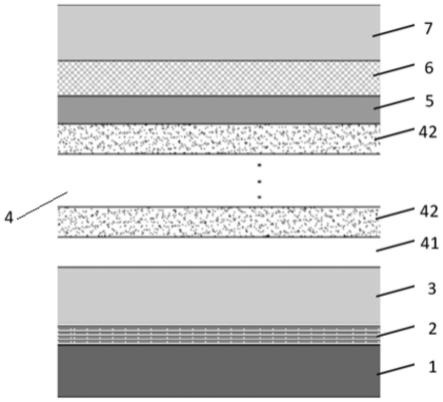

27.图1为本发明的结构示意图;

28.图2为本发明边缘量子垒层的铝组分x及电子阻挡层的铝组分a沿生长方向的变化

示意图;

29.图3为本发明边缘量子垒层的铝组分x及电子阻挡层的铝组分a沿生长方向的变化示意图;

30.图4为本发明边缘量子垒层的铝组分x及电子阻挡层的铝组分a沿生长方向的变化示意图;

31.其中:1、衬底,2、缓冲层,3、n型半导体层,4、复合量子阱层,5、边缘量子垒层,6、电子阻挡层,7、p型半导体层;

32.41、量子垒,42、量子阱。

具体实施方式

33.下面通过实施例并结合附图对本发明做进一步说明,但不限于此。

34.实施例1:

35.如图1-2所示,本实施例提供一种提高发光效率的led外延结构,包括从下到上依次设置的衬底1、缓冲层2、n型半导体层3、复合量子阱层4、边缘量子垒层5、电子阻挡层6和p型半导体层7,其中,复合量子阱层4包括交替设置的量子垒41和量子阱42,生长方向为沿着衬底垂直指向于n型半导体层,电子阻挡层6的势垒高度高于边缘量子垒层5的势垒高度,使边缘量子垒层在复合量子阱层和电子阻挡层之间形成空穴存储区和电子阻挡区域。

36.量子垒41包括algainp层,量子阱42包括gainp层,边缘量子垒层5包括p型掺杂的al

x

gayinzp层和非掺杂的al

x

gayinzp层,其中,靠近电子阻挡层6的al

x

gayinzp层为p型掺杂的al

x

gayinzp层,使其在避免电子与空穴在非复合量子阱区域进行复合发光的同时,通过p型掺杂提供更多的空穴,进一步增加空穴在靠近复合量子阱区域的储存及迁移能力,从而提高led发光效率,其余为非掺杂的al

x

gayinzp层。al

x

gayinzp层中,0≤x≤1,0≤y≤1,0≤z≤1,x+y+z=1。

37.边缘量子垒层5若干个al

x

gayinzp层中,x由复合量子阱层4指向电子阻挡层6的方向线性降低,如图2所示,图中,横坐标为生长方向,纵坐标为铝组分,y、z由复合量子阱层指向电子阻挡层的方向递增。

38.电子阻挡层6为alagabincp层和al

x

gayinzp层交替堆叠的超晶格结构,其中,0≤a≤1,0≤b≤1,0≤c≤1,a+b+c=1,且x≤a。

39.衬底1为蓝宝石、sic、si、algainp、gaas中的任意一种。

40.缓冲层2为n型掺杂的gaas缓冲层,n型半导体层3为alinp层。

41.上述提高发光效率的led外延结构的制备方法,步骤如下:

42.(1)将衬底放入mocvd反应室中,温度环境为850℃左右,通入ash3源,进行5分钟左右的预处理,然后降温至720℃左右,通入ga源,生长n型掺杂的gaas缓冲层;

43.(2)关闭ash3源和ga源,通入al、in源和ph3,环境温度为750℃,生长alinp层,得到n型半导体层;

44.(3)关闭掺杂源,持续通入al,ga源和in源,生长algainp量子垒,接着关闭al源,生长gainp量子阱,重复生长10~15周期,构成复合量子阱层;

45.(4)通入al源,并调节铝组分,生长al

x

gayinzp层,靠近复合量子阱层一侧的al

x

gayinzp层中铝组分最大,最顶层的al

x

gayinzp层中铝组分最小,同时,在最顶层的

al

x

gayinzp层中通入p型掺杂源,构成边缘量子垒层;

46.(5)关闭p型掺杂源,并调整铝组分,生长交替堆叠的alagabincp层和al

x

gayinzp层,构成电子阻挡层;

47.(6)将温度调整至750℃,关闭ga源,通入cp2mg,生长p型alinp层,掺杂浓度为0.5*10

18

cm-3-1*10

18

cm-3

,得p型半导体层。

48.实施例2:

49.一种提高发光效率的led外延结构,结构如实施例1所示,不同之处在于,边缘量子垒层5若干个al

x

gayinzp层中,铝组分x由下到上包括三个阶段,第一阶段内,铝组分恒定;第二阶段,铝组分线性减小;第三阶段,铝组分恒定,如图3所示,图中,横坐标为生长方向,纵坐标为铝组分,衬底为sic。

50.实施例3:

51.一种提高发光效率的led外延结构,结构如实施例1所示,不同之处在于,边缘量子垒层5若干个al

x

gayinzp层中,铝组分x呈梯度减小,如图4所示,图中,横坐标为生长方向,纵坐标为铝组分,衬底为si。

52.实施例4:

53.一种提高发光效率的led外延结构的制备方法,步骤如实施例(1)所述,不同之处在于,步骤(1)中,衬底1为algainp,gaas缓冲层2生长厚度为10nm,步骤(2)中alinp层生长厚度为30nm左右,步骤(3)中algainp量子垒生长厚度为10nm,gainp量子阱生长厚度为10nm,步骤(6)中p型alinp层生长厚度为30nm。

54.实施例5:

55.一种提高发光效率的led外延结构的制备方法,步骤如实施例(1)所述,不同之处在于,步骤(1)中,衬底1为gaas,步骤(6)中,掺杂浓度为1*10

18

cm-3

。

56.上述说明示出并描述了本技术的若干优选实施例,但如前所述,应当理解本技术并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述申请构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本技术的精神和范围,则都应在本技术所附权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1