框架单元标记伪栅版图及其设计方法与流程

本发明涉及半导体,特别是涉及一种框架单元标记伪栅版图及其设计方法。

背景技术:

1、通过自对准双重图形工艺(sadp)方式,可以获得光刻无法曝开的较小pitch(周期),使pitch缩小一倍。限于图形是大量重复单元的层次。

2、在frame(框架版图)中frame cell mark(框架单元标记)是摆放在切割道上,用于对准和测量的图形。目前的工艺中框架单元并没有添加伪栅,而是通过框架版图整体添加伪栅,同时这种方法只有极少数框架单元内部,部分层次会添加伪栅,目前fab(半导体工厂)里的使用的框架单元在较为先进的技术节点会产生脱落的问题。

3、为解决上述问题,需要提出一种新型的框架单元标记伪栅版图及其设计方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种框架单元标记伪栅版图及其设计方法,用于解决现有技术中框架单元并没有添加伪栅,而是通过框架版图整体添加伪栅,同时这种方法只有极少数框架单元内部,部分层次会添加伪栅,目前半导体工厂里的使用的框架单元在较为先进的技术节点会产生脱落的问题。

2、为实现上述目的及其他相关目的,本发明提供一种框架单元标记伪栅版图,包括:

3、框架图形,所述框架图形为单个shot中除芯片以外的剩余区域的图形;

4、所述框架图形上设有标记图形,所述标记图形用于定义出衬底切割道上用于对准和测量的图形;

5、所述标记图形间具有间隙,所述标记图形间插入有第一伪栅图形;

6、设于所述标记图形内的所述第二伪栅图形,所述第二伪栅图形根据不同层次的所述标记图形设置不同的尺寸;

7、设于所述标记图形上的假块标记层,所述假块标记层用于定义伪栅不形成的区域。

8、优选地,所述标记图形位于的区域包括m0a层和后段金属层。

9、优选地,所述第二伪栅图形在所述标记图形的区域中依次等距分布。

10、优选地,所述m0a层中的所述第二伪栅的长为1.2微米,宽为0.038微米,左右相邻的两所述第二伪栅的周期为0.18微米,上下相邻的两所述第二伪栅的周期为1.366微米。

11、优选地,所述后段金属层中的所述第二伪栅的长、宽均为0.8微米,左右相邻的两所述第二伪栅的周期以及上下相邻的两所述第二伪栅的周期均为0.8微米。

12、本发明还提供一种框架单元标记伪栅版图的设计方法,包括:

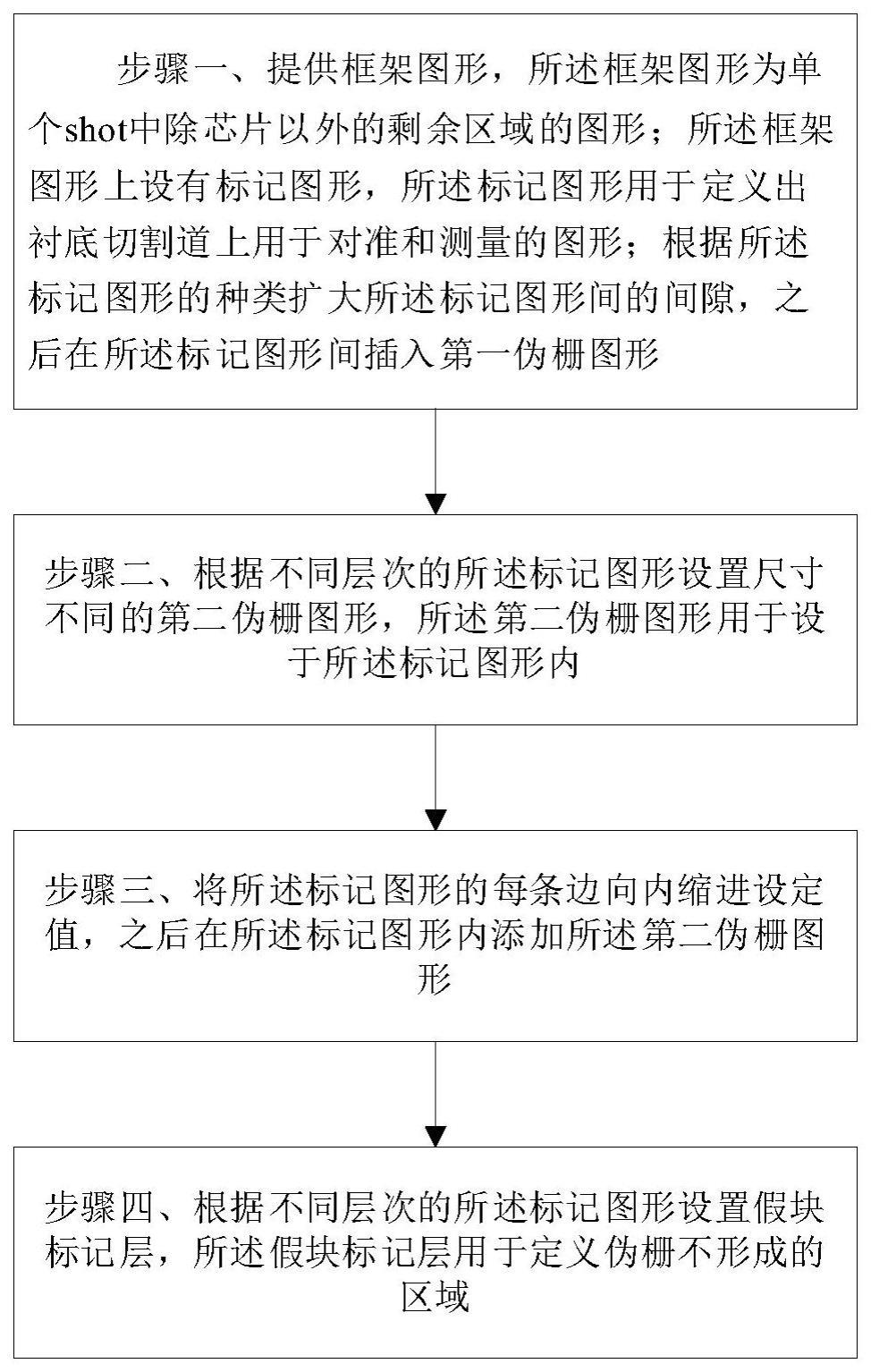

13、步骤一、提供框架图形,所述框架图形为单个shot中除芯片以外的剩余区域的图形;

14、所述框架图形上设有标记图形,所述标记图形用于定义出衬底切割道上用于对准和测量的图形;

15、根据所述标记图形的种类扩大所述标记图形间的间隙,之后在所述标记图形间插入第一伪栅图形;

16、步骤二、根据不同层次的所述标记图形设置尺寸不同的第二伪栅图形,所述第二伪栅图形用于设于所述标记图形内;

17、步骤三、将所述标记图形的每条边向内缩进设定值,之后在所述标记图形内添加所述第二伪栅图形;

18、步骤四、根据不同层次的所述标记图形设置假块标记层,所述假块标记层用于定义伪栅不形成的区域。

19、优选地,步骤一中所述标记图形位于的区域包括m0a层和后段金属层。

20、优选地,步骤一中的所述第二伪栅图形通过设计软件的设计规则与所述框架图形同时形成。

21、优选地,步骤二中所述第二伪栅图形在所述标记图形的区域中依次等距分布。

22、优选地,步骤二中所述m0a层中的所述第二伪栅的长为1.2微米,宽为0.038微米,左右相邻的两所述第二伪栅的周期为0.18微米,上下相邻的两所述第二伪栅的周期为1.366微米。

23、优选地,步骤二中所述后段金属层中的所述第二伪栅的长、宽均为0.8微米,左右相邻的两所述第二伪栅的周期以及上下相邻的两所述第二伪栅的周期均为0.8微米。

24、优选地,步骤三中所述缩进值为5至20微米。

25、如上所述,本发明的框架单元标记伪栅版图及其设计方法,具有以下有益效果:

26、本发明对原有框架单元标记伪栅版图进行伪栅图形添加处理,以达到测量或者对准的目的,解决了在先进技术节点工艺存在套准标记脱落的问题。

技术特征:

1.一种框架单元标记伪栅版图,其特征在于,包括:

2.根据权利要求1所述的框架单元标记伪栅版图,其特征在于:所述标记图形位于的区域包括m0a层和后段金属层。

3.根据权利要求1所述的框架单元标记伪栅版图,其特征在于:所述第二伪栅图形在所述标记图形的区域中依次等距分布。

4.根据权利要求2所述的框架单元标记伪栅版图,其特征在于:所述m0a层中的所述第二伪栅的长为1.2微米,宽为0.038微米,左右相邻的两所述第二伪栅的周期为0.18微米,上下相邻的两所述第二伪栅的周期为1.366微米。

5.根据权利要求2所述的框架单元标记伪栅版图,其特征在于:所述后段金属层中的所述第二伪栅的长、宽均为0.8微米,左右相邻的两所述第二伪栅的周期以及上下相邻的两所述第二伪栅的周期均为0.8微米。

6.一种框架单元标记伪栅版图的设计方法,其特征在于,至少包括:

7.根据权利要求6所述的框架单元标记伪栅版图的设计方法,其特征在于:步骤一中所述标记图形位于的区域包括m0a层和后段金属层。

8.根据权利要求6所述的框架单元标记伪栅版图的设计方法,其特征在于:步骤一中的所述第二伪栅图形通过设计软件的设计规则与所述框架图形同时形成。

9.根据权利要求6所述的框架单元标记伪栅版图的设计方法,其特征在于:步骤二中所述第二伪栅图形在所述标记图形的区域中依次等距分布。

10.根据权利要求7所述的框架单元标记伪栅版图的设计方法,其特征在于:步骤二中所述m0a层中的所述第二伪栅的长为1.2微米,宽为0.038微米,左右相邻的两所述第二伪栅的周期为0.18微米,上下相邻的两所述第二伪栅的周期为1.366微米。

11.根据权利要求7所述的框架单元标记伪栅版图的设计方法,其特征在于:步骤二中所述后段金属层中的所述第二伪栅的长、宽均为0.8微米,左右相邻的两所述第二伪栅的周期以及上下相邻的两所述第二伪栅的周期均为0.8微米。

12.根据权利要求6所述的框架单元标记伪栅版图的设计方法,其特征在于:步骤三中所述缩进值为5至20微米。

技术总结

本发明提供一种框架单元标记伪栅版图,包括框架图形,框架图形为单个shot中除芯片以外的剩余区域的图形;框架图形上设有标记图形,标记图形用于定义出衬底切割道上用于对准和测量的图形;标记图形间具有间隙,标记图形间插入有第一伪栅图形;设于标记图形内的第二伪栅图形,第二伪栅图形根据不同层次的标记图形设置不同的尺寸;设于标记图形上的假块标记层,假块标记层用于定义伪栅不形成的区域。本发明对原有框架单元标记伪栅版图进行伪栅图形添加处理,以达到测量或者对准的目的,解决了在先进技术节点工艺存在套准标记脱落的问题。

技术研发人员:刘思哲

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!