封装结构及其制作方法与流程

本发明涉及半导体封装领域,特别涉及一种封装结构及其制作方法。

背景技术:

1、随着半导体技术的日益发展,具有高的集成密度的封装结构越来越重要。例如,采用3d封装结构可以实现芯片与芯片之间的相互堆叠。

2、目前现有的硅光芯片中的电子集成电路芯片(electronic integrated circuitchip,eic芯片)和光子集成电路芯片(photonic integrated circuit chip,pic芯片)由于采用不同的晶圆生成工艺制程,采用芯片级别的互连(例如打线或倒装的互连方式)来实现电子集成电路芯片(eic芯片)与光子集成电路芯片(pic芯片)之间的连接,形成三维互连结构。

3、为了缩短信号传输路径获取足够好的电性能,光子集成电路芯片(pic芯片)和电子集成电路芯片(eic芯片)采用3d堆叠互联替换传统的打线互联越来越成为趋势。同时,如果光纤结构与光子集成电路芯片(pic芯片)采用面耦合的方式与光栅耦合器(gratingcouple,gc)进行耦合时,那么需要预留出用于耦合空间,同时要求耦合面上不能够有有机物残留从而阻挡光线的传输,这使得在光耦合区以及该光耦合区在宽度方向的延伸区域上方均不能够设置电子集成电路芯片(eic芯片),从而浪费了一定区域的面积,降低了电子集成电路芯片(eic芯片)和对应的光子集成电路芯片(pic芯片)的所占面积比例,故使得电子集成电路芯片(eic芯片)和光子集成电路芯片(pic芯片)的面积使用率不高。

技术实现思路

1、为了克服现有技术的不足,本发明的目的在于提供一种封装结构及其制作方法,其可以实现3d芯片堆叠封装,并能提高电子集成电路芯片(eic芯片)和光子集成电路芯片(pic芯片)的面积使用率。

2、本发明的目的采用以下技术方案实现:

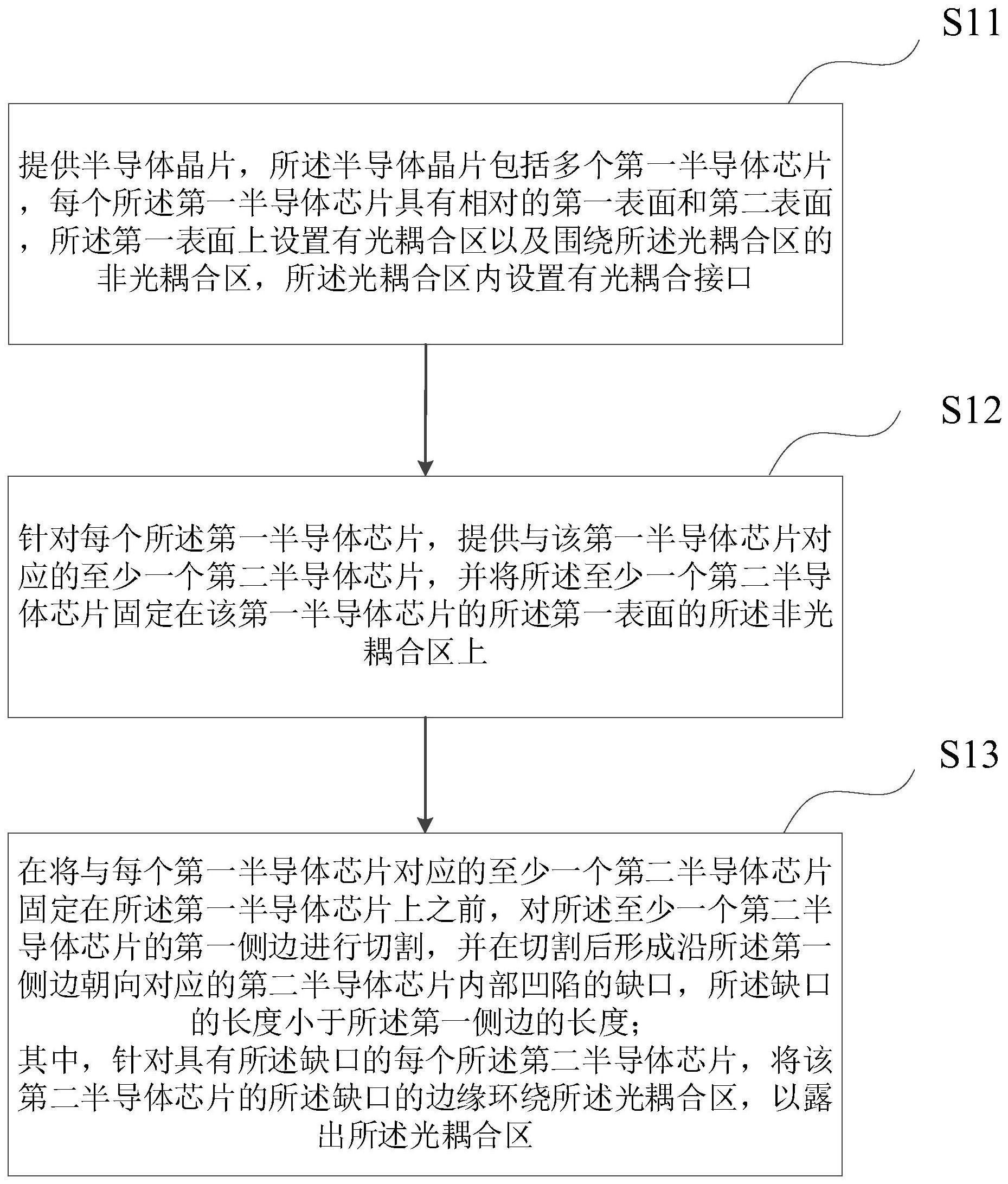

3、根据本发明的一方面,提供一种封装结构的制作方法,所述方法包括:

4、提供半导体晶片,所述半导体晶片包括多个第一半导体芯片,每个所述第一半导体芯片具有相对的第一表面和第二表面,所述第一表面上设置有光耦合区以及围绕所述光耦合区的非光耦合区,所述光耦合区内设置有光耦合接口;

5、针对每个所述第一半导体芯片,提供与该第一半导体芯片对应的至少一个第二半导体芯片,并将所述至少一个第二半导体芯片固定在该第一半导体芯片的所述第一表面的所述非光耦合区上;

6、在将与每个第一半导体芯片对应的至少一个第二半导体芯片固定在所述第一半导体芯片上之前,对所述至少一个第二半导体芯片的第一侧边进行切割,并在切割后形成沿所述第一侧边朝向对应的第二半导体芯片内部凹陷的缺口,所述缺口的长度小于所述第一侧边的长度;

7、其中,针对具有所述缺口的每个所述第二半导体芯片,将该第二半导体芯片的所述缺口的边缘环绕所述光耦合区,以露出所述光耦合区。

8、可选地,针对每个所述第一半导体芯片,对与该第一半导体芯片对应的一个第二半导体芯片的所述第一侧边进行切割,并在切割后形成沿所述第一侧边朝向该第二半导体芯片内部凹陷的所述缺口,所述缺口所在的区域位于该第二半导体芯片的所述第一侧边的中部或者端部,所述缺口的形状与所述光耦合区的形状相适应。

9、可选地,针对每个所述第一半导体芯片,对与该第一半导体芯片对应的两个第二半导体芯片的各自的所述第一侧边分别进行切割,并在切割后分别形成沿所述第一侧边朝向对应的两个半导体芯片内部凹陷的第一缺口和第二缺口,所述第一缺口所在的区域和所述第二缺口所在的区域各自位于对应的两个第二半导体芯片的所述第一侧边的端部,将其中一个具有所述第一缺口的第二半导体芯片和另一个具有所述第二缺口的第二半导体芯片以拼接的方式固定在所述光耦合区的四周,并且所述第一缺口和所述第二缺口在拼接后所形成的总的缺口的形状与所述光耦合区的形状相适应。

10、进一步地,针对具有所述缺口的每个所述第二半导体芯片,该第二半导体芯片的所述第一侧边在其长度方向上或者宽度方向上延伸至靠近所述第一半导体芯片的一侧边缘。

11、进一步地,针对每个所述第一半导体芯片,定义该第一半导体芯片的所述第一表面所占面积为s1,与该第一半导体芯片对应的所有的第二半导体芯片所占的面积之和为s2,其中,s2与s1之间的比例大于80%。

12、进一步地,所述半导体晶片包括:第一承载基板,所述第一承载基板与所述多个第一半导体芯片的所述第二表面临时键合,以用于临时承载所述半导体晶片。

13、进一步地,在将与每个第一半导体芯片对应的至少一个第二半导体芯片固定在所述第一半导体芯片上之后,所述方法还包括:将每个所述第二半导体芯片背离对应的第一半导体芯片的一侧表面与临时键合膜键合,随后将所述第一承载基板解键合。

14、进一步地,所述方法还包括:在将所述第一承载基板解键合之后,针对每个所述第一半导体芯片在所述半导体晶片上对应的区域边界,从所述第二表面指向所述第一表面的方向上,对所述半导体晶片进行切割;以及,去除所述临时键合膜,以得到多个分离的芯片封装组件,其中,每个所述芯片封装组件包括一个第一半导体芯片以及对应的至少一个第二半导体芯片。

15、可选地,所述临时键合膜包括光敏材料,以光照的方式去除所述临时键合膜。

16、进一步地,所述方法还包括:在得到多个分离的所述芯片封装组件之后,将每个所述芯片封装组件安装至对应的封装基板上,随后将导光结构或者激光器芯片安装至所述第一半导体芯片的所述光耦合接口上。

17、根据本发明的又一方面,提供一种封装结构的制作方法,所述方法包括:

18、提供半导体晶片,所述半导体晶片包括多个第一半导体芯片,每个所述第一半导体芯片具有相对的第一表面和第二表面,所述第一表面上设置有光耦合区以及围绕所述光耦合区的非光耦合区,所述光耦合区内设置有光耦合接口;

19、针对每个所述第一半导体芯片,提供与该第一半导体芯片对应的至少一个第二半导体芯片,并将所述至少一个第二半导体芯片固定在该第一半导体芯片的所述第一表面上;其中,所述至少一个第二半导体芯片上设置有虚拟区,所述虚拟区为不设置有电路的区域;针对具有所述虚拟区的每个所述第二半导体芯片,所述虚拟区的一侧边缘与该第二半导体芯片的第一侧边相重合;以及将所述至少一个第二半导体芯片的所述虚拟区对应覆盖在所述光耦合区上方;

20、制作塑封层,并使所述塑封层露出每个所述第二半导体芯片背离所述第一半导体芯片的一侧表面;

21、针对每个所述第一半导体芯片,去除覆盖于所述光耦合区上的所述至少一个第二半导体芯片上的所述虚拟区,以形成露出所述光耦合区的开口。

22、可选地,针对每个所述第一半导体芯片,在与该第一半导体芯片对应的一个第二半导体芯片上设置有所述虚拟区,所述虚拟区的一侧边缘位于该第二半导体芯片的所述第一侧边的中部或者端部,所述虚拟区的形状与所述光耦合区的形状相适应。

23、可选地,针对每个所述第一半导体芯片,在与该第一半导体芯片对应的两个第二半导体芯片上分别设置有第一虚拟区和第二虚拟区,所述第一虚拟区的一侧边缘和所述第二虚拟区的一侧边缘分别位于所述两个第二半导体芯片的所述第一侧边的端部,将其中一个具有所述第一虚拟区的第二半导体芯片和另一个具有所述第二虚拟区的另一个第二半导体芯片以拼接的方式覆盖在所述光耦合区的上方,并且所述第一虚拟区和所述第二虚拟区在拼接后所形成的总的虚拟区的形状与所述光耦合区的形状相适应。

24、进一步地,针对具有所述虚拟区的每个所述第二半导体芯片,该第二半导体芯片的所述第一侧边在其长度方向上或者宽度方向上延伸至靠近所述第一半导体芯片的一侧边缘。

25、进一步地,针对每个所述第一半导体芯片,定义该第一半导体芯片的所述第一表面所占面积为s1,与该第一半导体芯片对应的所有的第二半导体芯片所占的面积之和为s2,其中,s2与s1之间的比例大于80%。

26、进一步地,所述针对每个所述第一半导体芯片,去除覆盖于所述光耦合区上的所述至少一个第二半导体芯片上的所述虚拟区的方法包括:采用激光切割或者等离子切割的方式对所述至少一个第二半导体芯片的所述虚拟区所在的位置进行切割,以去除所述虚拟区。

27、进一步地,所述半导体晶片包括:第一承载基板,所述第一承载基板与所述多个第一半导体芯片的所述第二表面临时键合,以用于临时承载所述半导体晶片。

28、进一步地,在所述针对每个所述第一半导体芯片,去除覆盖于所述光耦合区上的所述至少一个第二半导体芯片上的所述虚拟区之后,所述方法还包括:将每个所述第二半导体芯片背离对应的第一半导体芯片的一侧表面与临时键合膜键合,随后将所述第一承载基板解键合。

29、进一步地,所述方法还包括:在将所述第一承载基板解键合之后,针对每个所述第一半导体芯片在所述半导体晶片上对应的区域边界,从所述第二表面指向所述第一表面的方向上,对所述半导体晶片进行切割;以及,去除所述临时键合膜,以得到多个分离的芯片封装组件,其中,每个所述芯片封装组件包括一个第一半导体芯片以及对应的至少一个第二半导体芯片。

30、进一步地,所述方法还包括:在得到多个分离的所述芯片封装组件之后,将每个所述芯片封装组件安装至对应的封装基板上,随后将导光结构或者激光器芯片安装至所述第一半导体芯片的所述光耦合接口上。

31、根据本发明的另一方面,还提供一种封装结构,包括:

32、第一半导体芯片,所述第一半导体芯片具有相对的第一表面和第二表面,在所述第一表面设置有光耦合区以及围绕所述光耦合区的非光耦合区,所述光耦合区内设置有光耦合接口;

33、至少一个第二半导体芯片,所述至少一个第二半导体芯片固定在所述第一表面的所述非光耦合区上;

34、其中,所述至少一个第二半导体芯片的第一侧边设置有朝向对应的第二半导体芯片内部凹陷的缺口,并且针对具有缺口的每个所述第二半导体芯片,该第二半导体芯片的所述缺口的边缘环绕所述光耦合区,以露出所述光耦合区。

35、可选地,针对每个所述第一半导体芯片,在与该第一半导体芯片对应的一个第二半导体芯片的所述第一侧边上开设有所述缺口,所述缺口所在的区域位于该第二半导体芯片的所述第一侧边的中部或者端部,其中,所述缺口的形状与所述光耦合区的形状相适应。

36、可选地,针对每个所述第一半导体芯片,在与该第一半导体芯片对应的两个第二半导体芯片的所述第一侧边上分别开设有第一缺口和第二缺口,所述第一缺口所在的区域和所述第二缺口所在的区域分别位于所述两个第二半导体芯片的所述第一侧边的端部,其中,具有所述第一缺口的一个第二半导体芯片和具有所述第二缺口的另一个第二半导体芯片以拼接的方式固定在所述光耦合区的四周,并且所述第一缺口和所述第二缺口在拼接后所形成的总的缺口的形状与所述光耦合区的形状相适应。

37、进一步地,针对具有所述缺口的每个所述第二半导体芯片,该第二半导体芯片的所述第一侧边在其长度方向上或者宽度方向上延伸至靠近所述第一半导体芯片的一侧边缘。

38、进一步地,针对每个所述第一半导体芯片,定义该第一半导体芯片的所述第一表面所占面积为s1,与该第一半导体芯片对应的所有的第二半导体芯片所占的面积之和为s2,其中,s2与s1之间的比例大于80%。

39、根据本发明的另一方面,还提供一种封装结构,包括:

40、第一半导体芯片,所述第一半导体芯片具有相对的第一表面和第二表面,在所述第一表面设置有光耦合区以及围绕所述光耦合区的非光耦合区,所述光耦合区内设置有光耦合接口;

41、至少一个第二半导体芯片,所述至少一个第二半导体芯片固定在所述第一表面的所述非光耦合区上,并且在所述光耦合区设置有贯通所述至少一个第二半导体芯片的开口,针对具有所述开口的每个所述第二半导体芯片,所述开口的一侧边缘与该第二半导体芯片的第一侧边相重合;

42、塑封层,所述塑封层位于所述第一表面上以及包覆所述至少一个第二半导体芯片的侧边,所述开口不被所述塑封层填充和覆盖。

43、进一步地,针对具有所述开口的每个所述第二半导体芯片,该第二半导体芯片的所述第一侧边在其长度方向上或者宽度方向上延伸至靠近所述第一半导体芯片的一侧边缘。

44、进一步地,针对每个所述第一半导体芯片,定义该第一半导体芯片的所述第一表面所占面积为s1,与该第一半导体芯片对应的所有的第二半导体芯片所占的面积之和为s2,其中,s2与s1之间的比例大于80%。

45、本发明实施例提供的封装结构及其制作方法,由于针对每个第一半导体芯片,与该第一半导体芯片对应的至少一个第二半导体芯片上制作有缺口或者开口以露出光耦合区,故相比于常用技术,增加了与该第一半导体芯片对应的所有第二半导体芯片所占的面积之和与该第一半导体芯片的所述第一表面所占面积的比例,同时还有利于提高第一半导体芯片和第二半导体芯片各自的有效利用面积,而且还避免了塑封层中的有机材料对光耦合区界面的污染问题。

- 还没有人留言评论。精彩留言会获得点赞!