包括支撑结构的半导体封装件的制作方法

1.本公开的示例实施例涉及半导体封装领域,具体地讲,涉及一种包括支撑结构的半导体封装件。

背景技术:

2.嵌入式多芯片封装(emcp,embedded multi-chip package)是一种结合嵌入式多媒体卡(emmc)和多芯片封装件(mcp)封装而成的智能电子设备存储器标准。因为emcp有内建的nand flash控制芯片,所以可以减少主芯片运算的负担,并且可以管理更大容量的快闪存储器。换言之,它将emmc与低功率双数据速率(lpddr)封装为一体,在减小体积的同时还减少了电路设计。另外,它将主控制芯片与nand flash集成为一体,通过内在的控制芯片来管理flash。

3.图1示出了根据相关技术的emcp封装结构。如图1所示,该emcp封装结构包括nand flash芯片(以下称为闪存芯片)1,dram芯片(以下称为存储器芯片)2以及ctrl.芯片(以下称为控制器芯片)3。控制器芯片3由于具有相对较小的尺寸而被放置在emcp封装结构的底部位置。为了保证控制器芯片3上的大尺寸芯片在安装时具备良好的结构性、电气性及可靠性,通常在其周围放置虚设芯片作为间隔件,以支撑上部芯片。

4.具体地,在完成底层的控制器芯片3的安装之后,在其四周安装一定面积的虚拟芯片4。然后,将存储器芯片2安装在由控制器芯片3与虚拟芯片4构成的扩展面积上。特别地,为了防止控制器芯片3与虚拟芯片4之间存在高度差异,通常还会在由控制器芯片3与虚拟芯片4构成的扩展面积上增加不小于存储器芯片2的面积的虚拟芯片5,再在虚拟芯片5提供的扩展面积上安装存储器芯片2。此外,对于基板上未设置控制器芯片3的区域,可以利用大尺寸的虚拟芯片6来补偿设置在该区域内的存储器芯片2a与存储器芯片2之间的高度差异,并且在由存储器芯片2和2a构成的扩展面积上安装闪存芯片1。

5.图1的上述emcp封装结构需要使用大量的虚拟芯片作为间隔件,因而组装工程周转平均时间(tat)长,生产效率低下。由于并列芯片的上表面之间存在高度差异,因此直接安装上部存储器芯片时存在破裂的风险。

技术实现要素:

6.本公开的示例实施例公开了一种包括由模塑材料包封的支撑结构以扩大其对上部芯片的支撑面积的半导体封装件。

7.根据本公开的一方面,提供一种半导体封装件,其包括:基板;支撑结构,设置在基板上,所述支撑结构包括由第一模塑材料包封的第一芯片;多个第二芯片,所述多个第二芯片中的至少一个第二芯片设置在支撑结构上;以及第三芯片,设置在所述多个第二芯片上,其中,第一芯片具有第一尺寸,所述多个第二芯片中的每个具有第二尺寸,第三芯片具有第三尺寸,其中,第一尺寸小于第二尺寸和第三尺寸,并且其中,所述多个第二芯片中的所述至少一个第二芯片的顶表面与所述多个第二芯片中的其余的第二芯片的顶表面位于同一

高度水平处。

8.优选地,支撑结构还可以包括:多个凸点,设置在第一芯片的有效表面上;以及底部填充材料,设置在所述多个凸点与基板之间,其中,第一芯片通过所述多个凸点连接到基板的电路图案。

9.优选地,第一模塑材料可以覆盖第一芯片以形成第一扩展面积,所述多个第二芯片中的所述至少一个第二芯片设置在第一扩展面积上。

10.优选地,第三尺寸可以大于第二尺寸。

11.优选地,第一扩展面积可以等于或者大于第三芯片的占据面积。

12.优选地,所述半导体封装件还可以包括:虚设芯片,设置在基板上并与支撑结构分隔开,所述多个第二芯片中的所述其余的第二芯片设置在虚设芯片上。

13.优选地,虚设芯片的顶表面可以与支撑结构的顶表面位于同一高度水平处。

14.优选地,第一扩展面积可以等于或者大于所述多个第二芯片中的所述至少一个第二芯片的占据面积。

15.优选地,所述第一芯片可以包括控制器芯片,所述多个第二芯片可以包括存储器芯片,所述第三芯片可以包括闪存芯片。

16.优选地,所述半导体封装件还可以包括:第二模塑材料,包封支撑结构、所述多个第二芯片以及第三芯片。

17.优选地,所述支撑结构可以是预制支撑结构。

18.根据本公开的另一方面,提供一种半导体封装件,其包括:基板;支撑结构,设置在所述基板上,所述支撑结构包括由第一模塑材料包封的第一芯片;一个或更多个第二芯片,片设置在所述支撑结构上;以及第三芯片,设置在所述一个或更多个第二芯片上,其中,所述第一芯片具有第一尺寸,所述一个或更多个第二芯片中的每个具有第二尺寸,所述第三芯片具有第三尺寸,并且其中,所述第一尺寸小于所述第二尺寸。

19.优选地,所述一个或更多个第二芯片中的第一个第二芯片可以设置在所述支撑结构上,并且所述一个或更多个第二芯片中的第二个第二芯片可以设置在所述支撑结构上。

20.优选地,所述第一个第二芯片的顶表面可以与所述第二个第二芯片的顶表面位于同一高度水平处。

21.优选地,所述一个或更多个第二芯片中的第一个第二芯片可以设置在所述支撑结构上,并且虚设芯片可以设置在所述支撑结构上。

22.优选地,所述第一个第二芯片的顶表面可以与所述虚设芯片的顶表面位于同一高度水平处。

23.优选地,所述第一尺寸可以小于所述第三尺寸。

24.优选地,所述第一模塑材料可以覆盖所述第一芯片以形成第一扩展面积,并且所述一个或更多个第二芯片可以设置在所述第一扩展面积上。

25.优选地,所述第一扩展面积可以等于或者大于所述第三芯片的占据面积。

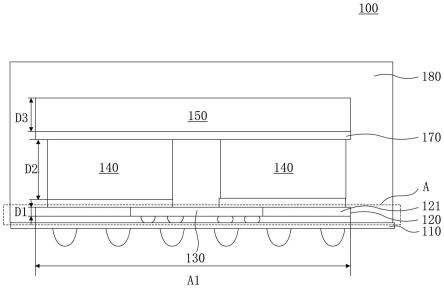

26.优选地,所述第一扩展面积可以等于或者大于所述一个或更多个第二芯片的占据面积。

附图说明

27.通过下面结合附图详细描述本公开的示例实施例,本公开的以上和其他方面的特征及优点将变得明确。在附图中,同样的附图标记将始终指示同样的元件。

28.图1示出了根据相关技术的emcp封装结构。

29.图2示出了根据本公开的示例实施例的半导体封装件。

30.图3示出了图2的虚线框a中所示的根据本公开的示例实施例的半导体封装件中包括的支撑结构的放大图。

31.图4示出了根据本公开的示例实施例的半导体封装件。

具体实施方式

32.在下文中,将参照其中示出一些实施例的附图来更充分地描述本公开的各种实施例。然而,本公开可以以许多不同的形式实施,并且不应该被解释为局限于在此阐述的实施例。相反,提供这些实施例使得该描述将是彻底的和完整的,并且这些实施例将把本公开的范围传达给本领域技术人员。在附图中,为了清楚起见,可能夸大层和区域的尺寸。

33.为了易于描述,可以在这里使用诸如“在

……

之下”、“在

……

下方”、“下面的”、“在

……

上方”、“上面的”等的空间相对术语来描述如附图中示出的一个元件与其他元件的关系。将理解的是,除了附图中绘出的方位之外,空间相对术语还意图包括装置在使用或操作中的不同方位。例如,如果附图中的装置被翻转,则被描述为“在”其他元件“下方”或“之下”的元件随后将被定向为“在”所述其他元件“上方”。因此,术语“在

……

下方”可以包括“在

……

上方”和“在

……

下方”两种方位。可以将装置另外定向(旋转90度或在其他方位),并相应地解释在这里使用的空间相对描述语。

34.图2示出了根据本公开的示例实施例的半导体封装件。

35.如图2所示,根据本公开的第一实施例的半导体封装件100包括:基板110;支撑结构120,设置在基板110上,支撑结构120包括由第一模塑材料121包封的第一芯片130;多个第二芯片140,多个第二芯片140中的至少一个第二芯片设置在支撑结构120上;以及第三芯片150,设置在多个第二芯片140上。支撑结构120可以是预制支撑结构。

36.在实施例中,基板110可以是刚性基板或柔性基板。基板110可以包括用于形成半导体封装件的基板的任何材料。例如,基板110可以是其上设置有电路图案的印刷电路板。

37.第一芯片130具有第一尺寸d1。所述多个第二芯片140中的每个第二芯片具有第二尺寸d2。第三芯片150具有第三尺寸d3。第一尺寸d1小于第二尺寸d2和第三尺寸d3。在示例实施例中,第一尺寸d1可以包括第一芯片130的高度,第二尺寸d2可以包括第二芯片140的高度,并且第三尺寸d3可以包括第三芯片150的高度。例如,第一尺寸d1可以是第一芯片130的高度,第二尺寸d2可以是第二芯片140的高度,并且第三尺寸d3可以是第三芯片150的高度。第一芯片130的高度小于第二芯片140的高度和第三芯片150的高度。然而,本公开不限于此,第一尺寸、第二尺寸和第三尺寸可以包括第一芯片、第二芯片和第三芯片的长度、宽度、高度、体积等各种维度中的至少一种维度,只要第一尺寸与第二尺寸和第三尺寸之间存在的差异能够导致本公开所要解决的技术问题即可。

38.在实施例中,第一芯片130可以是较小芯片,第二芯片140和第三芯片150可以是较大芯片。例如,第一芯片130可以是与第二芯片140和第三芯片150相比而相对较小的芯片。

可以指第三芯片在竖直方向上的足迹面积,或者可以指第三芯片沿着竖直方向的投影的面积。在一些示例实施例中,所述的“占据面积”可以基本等于第三芯片的底表面的面积。虽然图2示出了预制支撑结构120的第一扩展面积a1与第三芯片150的占据面积相同,但本公开不限于此,在其它的示例实施例中,第一扩展面积a1可以大于第三芯片150的占据面积。根据另一示例实施例,第一扩展面积a1可以小于第三芯片150的占据面积。

46.在示例实施例中,半导体封装件100还可以包括多个粘合层170。多个粘合层170可以设置在第二芯片140与预制支撑结构120之间以及第三芯片150与第二芯片140之间,以将这些元件彼此粘合在一起。

47.在示例实施例中,半导体封装件100还可以包括第二模塑材料180。第二模塑材料180可以对预制支撑结构120、多个第二芯片140以及第三芯片150进行包封。在实施例中,第二模塑材料180可以是环氧模塑化合物,例如环氧树脂,或者可以是本领域常用于包封芯片的任何材料。

48.在示例实施例中,第一芯片130可以包括控制器芯片,第二芯片140可以包括存储器芯片,第三芯片150可以包括闪存芯片。与存储器芯片和闪存芯片相比,控制器芯片具有较小的尺寸,因而被置于封装件的底部。通过将控制器芯片进行包封,形成预制支撑结构,使得对尺寸较小的控制器芯片的面积进行有效扩展,可以完全不使用虚设芯片,避免了因为使用虚设芯片而导致的工程性及可靠性问题。

49.图4示出了根据本公开的另一示例实施例的半导体封装件。除了虚设芯片和预制支撑结构之外,图4所示的半导体封装件与图2所示的半导体封装件基本相同。以下,将重点描述第二实施例与第一实施例之间的差异。

50.如图4所示,根据本公开的第二实施例的半导体封装件200包括:基板210;预制支撑结构220,设置在基板210上,预制支撑结构220包括由第一模塑材料221包封的第一芯片230;多个第二芯片240,所述多个第二芯片240中的至少一个第二芯片241设置在预制支撑结构220上;以及第三芯片250,设置在多个第二芯片240上。

51.半导体封装件200还可以包括虚设芯片260。虚设芯片260可以设置在基板210上并与预制支撑结构220分隔开。多个第二芯片240中的其余的第二芯片242设置在虚设芯片260上。

52.在示例实施例中,如图4所示,第一芯片230的第一尺寸d1小于至少一个第二芯片241的第二尺寸d2和第三芯片250的第三尺寸d3。至少一个第二芯片241的顶表面与多个第二芯片240中的其余的第二芯片242的顶表面位于同一高度水平处。

53.在示例实施例中,如图4所示,虚设芯片260的顶表面可以与预制支撑结构220的顶表面位于同一高度水平处。第一模塑材料221可以覆盖第一芯片230以形成第一扩展面积a2,并且至少一个第二芯片241可以设置在第一扩展面积a2上。在本示例实施例中,第一扩展面积a2可以与至少一个第二芯片241的占据面积相同。然而,在其它的示例实施例中,第一扩展面积a1可以大于至少一个第二芯片241的占据面积。

54.在根据本公开的示例实施例的半导体封装件中,由于设置在封装件底部的具有较小尺寸的第一芯片被模塑材料包封,扩大了其对上部芯片的支撑面积,减少了虚设芯片的使用量,降低了半导体封装结构的复杂程度,同时可以规避由引入多颗虚设芯片而导致的工程性及可靠性问题。

55.本公开的示例实施例在半导体封装件的底部设计预制支撑结构,可以全部或部分代替虚设芯片,实现工程效率的提高,彻底根治由多个芯片之间的高度差而导致的上部芯片破裂等的诸如emcp的产品的品质顽疾。

56.虽然已经在此示出和描述了本公开的实施例,但本领域技术人员将清楚的是,在不脱离由权利要求限定的本公开的精神和范围的情况下,可以做出各种修改和变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1