芯片及其制造、安装方法以及印刷电路板预制件与流程

本发明涉及半导体,具体地涉及一种芯片及其制造、安装方法以及印刷电路板预制件。

背景技术:

1、目前市面上存在一种包含高边开关的功率分配(power distribution)芯片。这种功率分配芯片在单片或多片芯片(die)上集成了控制电路和功率金属-氧化物半导体场效应晶体管(简称金氧半场效晶体管,metal-oxide-semiconductor field-effecttransistor,mosfet)。

2、目前主流的功率分配芯片产品中,功率mosfet通常采用垂直工艺制造,控制电路部分则采用横向工艺制造。产品的封装采用有引脚(lead)有散热焊盘(thermal pad)的封装形式,具体采用引线键合(bonding wire)工艺,散热焊盘接最高电位(vin)。对于使用按前述方式制造的功率分配芯片的用户,会在印刷电路板(printed circuit board,pcb)上设计相应的图案,如按功率分配芯片的引脚位置设置pcb板上引脚焊盘的焊盘位置和电网络,按功率分配芯片的散热焊盘位置设计pcb板上散热焊盘的焊盘位置和电网络。

3、如果直接用bcd(bipolar-cmos-dmos,其中,bipolar是用于高精度处理模拟信号的双极晶体管,cmos是用于设计数字控制电路的互补金属氧化物半导体,dmos是用于开发电源和高压开关器件的双扩散金属氧化物半导体)工艺制造,当采用有引脚的封装方案时,由于bcd的衬底必须接地,而现有pcb板上散热焊盘通常接最高电位,两者电位的不匹配导致用bcd工艺制造的功率分配芯片无法和现有市面上的pcb板做管脚到管脚(pin-to-pin,也称pin-2-pin)兼容。而且,bcd工艺的引线键合电阻较高,影响器件性能。

4、如果采用倒装芯片(flip-chip)工艺制造,虽然能够有效减小电阻以克服bcd工艺电阻高的缺陷。但倒装芯片没有引脚,也没有散热焊盘,因此同样无法和现有市面上的pcb板做pin-2-pin兼容。而且一般来说,倒装芯片的封装尺寸和芯片本身尺寸相近,通常并不会为了实现pin-2-pin兼容打线封装而把倒装芯片的封装专门设计的较大,或者为了兼容而特别设计倒装芯片的电连接图案。

5、这就导致现有诸如倒装芯片之类的无引脚芯片无法直接安装到针对有引脚芯片设计的pcb板上。

技术实现思路

1、本发明解决的技术问题是如何使无引脚芯片兼容针对有引脚芯片设计的pcb板。

2、为解决上述技术问题,本发明实施例提供一种芯片,包括:本体,具有相对的第一侧和第二侧;封装框架,位于所述本体的第一侧并和所述本体电连接,所述封装框架背离所述本体一侧的外露图案和目标图案相匹配,所述目标图案包括目标印刷电路板上焊盘的焊盘位置和电网络的布局;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

3、可选的,所述外露图案和所述目标图案相匹配包括:所述外露图案和所述目标图案相重叠的区域无电气网络冲突。

4、可选的,所述外露图案属于匹配图案的一部分,所述匹配图案包括所述封装框架上电网络的布局以及所述封装框架面向所述本体一侧和所述本体的焊点连接的结构,所述匹配图案根据所述目标图案确定,所述本体和所述目标印刷电路板通过所述匹配图案提供的电网络电连接。

5、可选的,所述封装框架为单层结构,所述匹配图案的一部分暴露在所述封装框架背离所述本体的一侧以形成所述外露图案。

6、可选的,所述封装框架为多层结构,所述匹配图案包括各层框架上电网络的布局,其中,最外层框架上电网络的布局形成所述外露图案。

7、可选的,所述外露图案与所述目标图案基本保持一致。

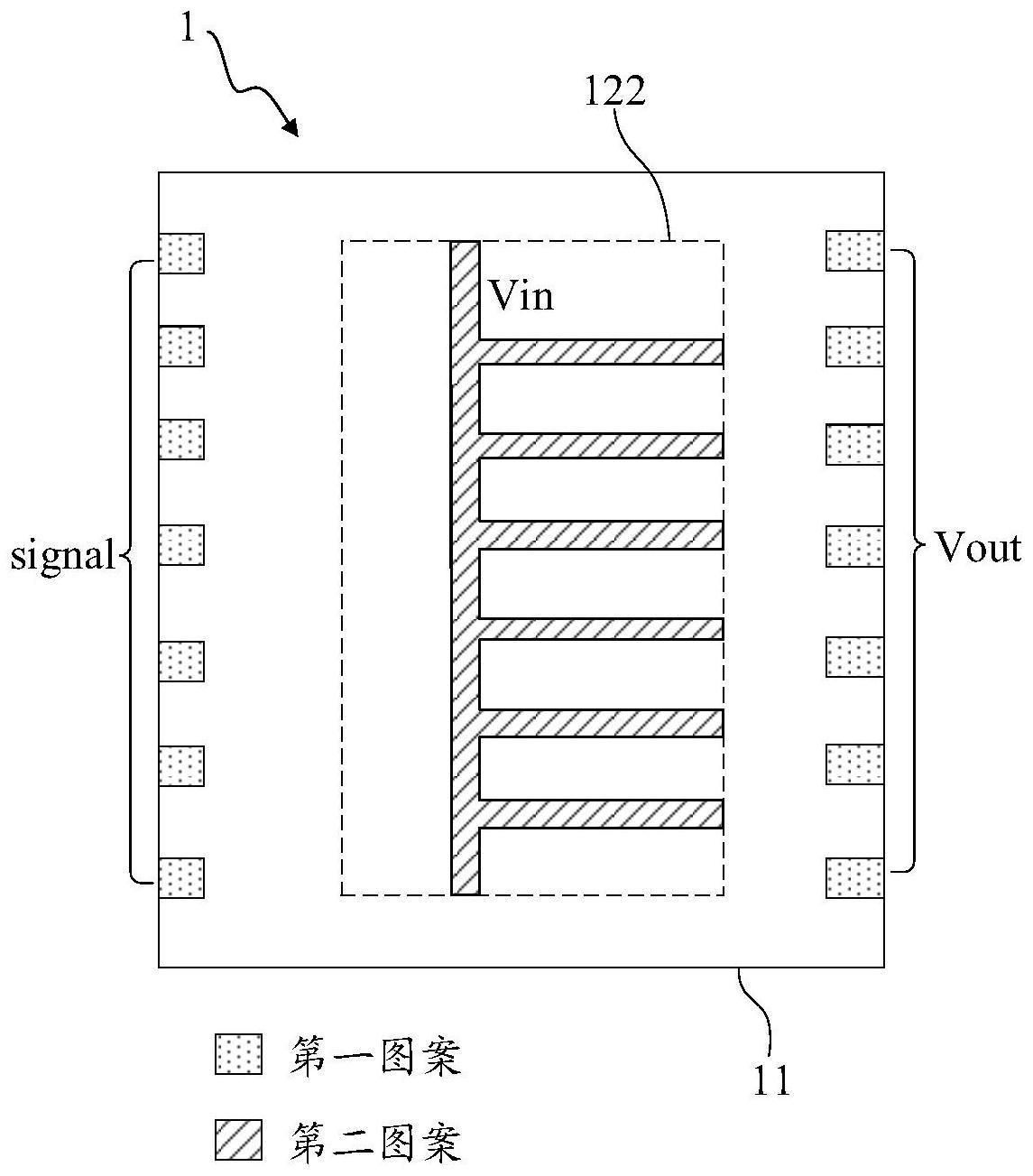

8、可选的,所述焊盘包括引脚焊盘,所述外露图案包括第一图案,所述第一图案在所述封装框架上的分布和所述引脚焊盘的焊盘位置相对应。

9、可选的,所述焊盘包括散热焊盘,所述外露图案包括第二图案,所述第二图案落入所述散热焊盘的焊盘图形内。

10、可选的,所述封装框架为多层结构,所述第二图案根据所述散热焊盘的焊盘图形确定,所述第二图案包括多层框架中最外层框架上电网络的布局。

11、可选的,所述封装框架为单层结构,所述第二图案属于匹配图案暴露在所述封装框架背离所述本体一侧形成的图形,其中,所述匹配图案包括所述封装框架上电网络的布局以及所述封装框架面向所述本体一侧和所述本体的焊点连接的结构,所述匹配图案根据所述目标图案确定,所述本体和所述目标pcb板通过所述匹配图案提供的电网络电连接。

12、可选的,所述本体的第一侧设置有焊点和电网络,所述本体通过所述焊点和电网络和所述封装框架电连接。

13、可选的,所述焊点包括交替阵列排布的多个输入电压焊点和多个输出电压焊点,并且,输入电压焊点和输出电压焊点交错设置。

14、可选的,所述封装框架包括多个条状的电网络,所述电网络适于电连接所述焊点和所述焊盘。

15、可选的,所述无引脚芯片包括倒装芯片,和/或,所述芯片包括功率分配芯片。

16、可选的,所述本体包括:半导体衬底,具有相对的正面和背面,所述正面朝向所述本体的第一侧,所述背面朝向所述本体的第二侧;工作器件,形成于所述半导体衬底的正面,所述封装框架位于所述工作器件远离所述半导体衬底的一侧。

17、为解决上述技术问题,本发明实施例还提供一种芯片制造方法,包括:获取目标图案,其中,所述目标图案包括目标印刷电路板上焊盘的焊盘位置和电网络的布局;根据所述目标图案确定封装框架的外露图案,以使所述外露图案和所述目标图案相匹配;将所述封装框架电连接至本体的第一侧,得到所述芯片,其中,所述本体具有相对的第一侧和第二侧,所述外露图案位于所述封装框架背离所述本体的一侧;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

18、可选的,所述外露图案和所述目标图案相匹配包括:所述外露图案和所述目标图案相重叠的区域无电气网络冲突。

19、可选的,所述根据所述目标图案确定封装框架的外露图案,以使所述外露图案和所述目标图案相匹配包括:根据所述目标图案确定匹配图案,其中,所述匹配图案包括所述封装框架上电网络的布局以及所述封装框架面向所述本体一侧和所述本体的焊点连接的结构,所述本体和所述目标印刷电路板通过所述匹配图案提供的电网络电连接;基于所述匹配图案得到所述外露图案。

20、可选的,所述封装框架为单层结构,所述基于所述匹配图案得到所述外露图案包括:半蚀刻所述封装框架,以在所述封装框架背离所述本体的一侧去除部分匹配图案,剩余部分匹配图案适于形成所述外露图案。

21、可选的,所述封装框架为多层结构,所述匹配图案包括各层框架上电网络的布局,所述基于所述匹配图案得到所述外露图案包括:将所述匹配图案中最外层框架上电网络的布局确定为所述外露图案。

22、可选的,所述外露图案与所述目标图案基本保持一致。

23、可选的,所述焊盘包括引脚焊盘,所述外露图案包括第一图案,所述根据所述目标图案确定封装框架的外露图案包括:根据所述引脚焊盘的焊盘位置相对应地确定得到所述第一图案在所述封装框架上的分布。

24、可选的,所述焊盘包括散热焊盘,所述外露图案包括第二图案,所述根据所述目标图案确定封装框架的外露图案包括:根据所述散热焊盘的焊盘图形和所述封装框架的层数确定得到所述第二图案,以使所述第二图案落入所述散热焊盘的焊盘图形内。

25、可选的,所述根据所述散热焊盘的焊盘图形和所述封装框架的层数确定得到所述第二图案包括:当所述封装框架为多层结构时,根据所述散热焊盘的焊盘图形确定所述第二图案,其中,所述第二图案包括多层框架中最外层框架上电网络的布局;当所述封装框架为单层结构时,将所述封装框架背离所述本体一侧半蚀刻后剩余的部分匹配图案确定为所述第二图案,其中,所述匹配图案包括所述封装框架上电网络的布局以及所述封装框架面向所述本体一侧和所述本体的焊点连接的结构,所述匹配图案根据所述目标图案确定,所述本体和所述目标pcb板通过所述匹配图案提供的电网络电连接。

26、可选的,所述将所述封装框架电连接至本体的第一侧,得到所述芯片包括:在所述本体的第一侧设置焊点和电网络;通过所述焊点将封装框架电连接至所述本体的第一侧。

27、为解决上述技术问题,本发明实施例还提供一种芯片安装方法,包括:获取上述芯片;获取目标印刷电路板,所述目标印刷电路板具有相对的第一侧和第二侧,所述目标印刷电路板的第一侧设置有所述目标图案;在所述目标印刷电路板的第一侧设置掩膜层,所述掩膜层具有开窗图案以暴露部分所述目标图案,所述开窗图案和所述外露图案相匹配;在所述开窗图案限定的开窗区域内填充电连接材料,将所述芯片安装至所述目标印刷电路板的第一侧,其中,所述芯片通过所述电连接材料和所述目标印刷电路板电连接;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

28、可选的,在将所述芯片安装至所述目标印刷电路板的第一侧之后,所述芯片安装方法还包括:去除所述掩膜层。

29、可选的,所述在所述目标印刷电路板的第一侧设置掩膜层包括:以所述开窗图案为掩膜在所述目标印刷电路板的第一侧按所述开窗图案形成阻焊层;或者,在所述目标印刷电路板的第一侧遮盖钢网,所述钢网上的开窗位置和开窗面积根据所述开窗图案确定。

30、为解决上述技术问题,本发明实施例还提供一种印刷电路板预制件,包括:印刷电路板,具有相对的第一侧和第二侧,所述印刷电路板的第一侧设置有目标图案,所述目标图案包括所述印刷电路板上焊盘的焊盘位置和电网络的布局;掩膜层,设置于所述印刷电路板的第一侧,所述掩膜层具有开窗图案以暴露部分所述目标图案,所述开窗图案和外露图案相匹配,所述外露图案为芯片的封装框架暴露在外的电网络的布局,所述外露图案和所述目标图案相匹配;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

31、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

32、本发明实施例提供一种芯片,包括:本体,具有相对的第一侧和第二侧;封装框架,位于所述本体的第一侧并和所述本体电连接,所述封装框架背离所述本体一侧的外露图案和目标图案相匹配,所述目标图案包括目标印刷电路板上焊盘的焊盘位置和电网络的布局;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

33、较之现有技术需要用户自行调整pcb板上的电连接图案以匹配无引脚芯片,本实施方案能够使无引脚芯片直接兼容针对有引脚芯片设计的pcb板,从而提高芯片通用性,减轻用户侧工作负担。具体而言,虽然芯片为无引脚(leadless)封装,但封装好的芯片底部封装框架外露部分的图形和电网络是经过专门设计的。进一步,通过使封装框架的外露图案和目标pcb板上的电连接图案相匹配,如目标pcb板上有焊盘的区域确保封装框架上的对应部分保持外露,目标pcb板上非焊盘的区域则使封装框架上的对应部分保持不外露。由此,本实施方案公开的芯片虽然是采用无引脚工艺封装得到的,仍然能焊接在原先为采用有引脚工艺封装的芯片设计的客户pcb板的焊盘上,不会发生电气网络/电气功能冲突(或不匹配)的现象,这种冲突或不匹配可以例如是电气短路或电网络没连上。

34、进一步,所述无引脚封装可以具体是指,芯片封装好后没有引脚伸出。所述封装框架的外露图案和pcb板上的电连接图案(即目标图案)相匹配可以包括,外露图案和目标图案相重叠的区域无电气网络冲突。例如,在原本有引脚封装的引脚的对应位置,本实施方案的芯片设计了封装框架外露部分,外露部分的形状与引脚近似,且电网络也与引脚相对应。又例如,在原本有引脚封装的散热焊盘对应位置,本实施方案的芯片同样设计将封装框架对应电网络外露,且尽量增大这个电网络外露的面积。而在非引脚和非散热焊盘区域,可以通过诸如半蚀刻工艺或多层封装框架中最外层框架上电网络布局的针对性设计让封装框架在这些区域不要外露在芯片正面。

35、本发明实施例还提供一种芯片制造方法,包括:获取目标图案,其中,所述目标图案包括目标印刷电路板上焊盘的焊盘位置和电网络的布局;根据所述目标图案确定封装框架的外露图案,以使所述外露图案和所述目标图案相匹配;将所述封装框架电连接至本体的第一侧,得到所述芯片,其中,所述本体具有相对的第一侧和第二侧,所述外露图案位于所述封装框架背离所述本体的一侧;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

36、较之现有技术在以倒装工艺等方式制造无引脚芯片时不考虑和原本pcb板的兼容性问题,本实施方案在芯片制造阶段即考虑兼容性问题,并出于兼容考量特别设计封装框架和芯片上的电连接图案。由此,采用本实施方案制备得到的无引脚芯片能够直接兼容针对有引脚芯片设计的pcb板,芯片的通用性得以显著提高,用户侧的工作负担也得以减轻。具体而言,对于采用无引脚封装的芯片,通过使封装框架的外露图案和pcb板上的电连接图案相匹配,如pcb板上有焊盘的区域确保封装框架上的对应部分保持外露,pcb板上非焊盘的区域则通过半蚀刻工艺或多层封装框架中最外层框架上电网络布局的针对性设计使封装框架上的对应部分不外露在芯片背面。由此,本实施方案公开的芯片虽然是采用无引脚工艺封装得到的,仍然能焊接在原先为采用有引脚工艺封装的芯片设计的客户pcb板的焊盘上,不会发生电气网络/电气功能的冲突/不匹配。

37、本发明实施例还提供一种芯片安装方法,包括:获取上述芯片;获取目标印刷电路板,所述目标印刷电路板具有相对的第一侧和第二侧,所述目标印刷电路板的第一侧设置有所述目标图案;在所述目标印刷电路板的第一侧设置掩膜层,所述掩膜层具有开窗图案以暴露部分所述目标图案,所述开窗图案和所述外露图案相匹配;在所述开窗图案限定的开窗区域内填充电连接材料,将所述芯片安装至所述目标印刷电路板的第一侧,其中,所述芯片通过所述电连接材料和所述目标印刷电路板电连接;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

38、本实施方案能够以较小的工艺改进和较高的用户操作便利性,实现无引脚芯片在针对有引脚芯片设计的目标pcb板上的兼容安装。具体而言,只需针对性地调整掩膜层上的开窗图案使之匹配芯片的外露图案,即可将无引脚芯片可靠安装到针对有引脚芯片设计的目标pcb板上。

39、本发明实施例还提供一种印刷电路板预制件,包括:印刷电路板,具有相对的第一侧和第二侧,所述印刷电路板的第一侧设置有目标图案,所述目标图案包括所述印刷电路板上焊盘的焊盘位置和电网络的布局;掩膜层,设置于所述印刷电路板的第一侧,所述掩膜层具有开窗图案以暴露部分所述目标图案,所述开窗图案和外露图案相匹配,所述外露图案为芯片的封装框架暴露在外的电网络的布局,所述外露图案和所述目标图案相匹配;其中,所述芯片包括无引脚芯片,所述目标图案是针对有引脚芯片设计的。

40、本实施方案在印刷电路板上预制备得到开窗图案和无引脚芯片的外露图案相匹配的掩膜层。由此,用户在将无引脚芯片安装至该印刷电路板预制件时基本无需调整安装工艺,即可实现无引脚芯片在针对有引脚芯片设计的pcb板上的兼容安装。

- 还没有人留言评论。精彩留言会获得点赞!