一种芯片、制备方法、三维堆叠芯片及电子设备与流程

本技术涉及半导体,尤其涉及一种芯片、制备方法、三维堆叠芯片及电子设备。

背景技术:

1、在制作芯片时,为确保芯片的良率,可以在芯片封装之前进行测试,在测试结果满足要求时再进行封装,这样可以保证封装后的每个芯片的良率。为了便于测试,在制作芯片时可以制作出用于与测试设备进行连接的测试垫(也可以称之为测试pad),测试设备中的测试针可以扎至测试pad内,实现测试设备与测试pad的电连接;在测试完成后,再将测试针从测试pad内取出即可。

2、然而,测试pad被测试针扎过之后,会在测试pad之上留下针痕和翘起,而针痕和翘起不利于封装,造成封装困难。这种情况下,可以对针痕和翘起进行腐蚀,以便于封装,但是在进行腐蚀处理时很容易出现过腐蚀现象,从而对芯片造成损坏,造成芯片的制作良率下降。

技术实现思路

1、本技术提供一种芯片、制备方法、三维堆叠芯片及电子设备,用以提高芯片的制作良率。

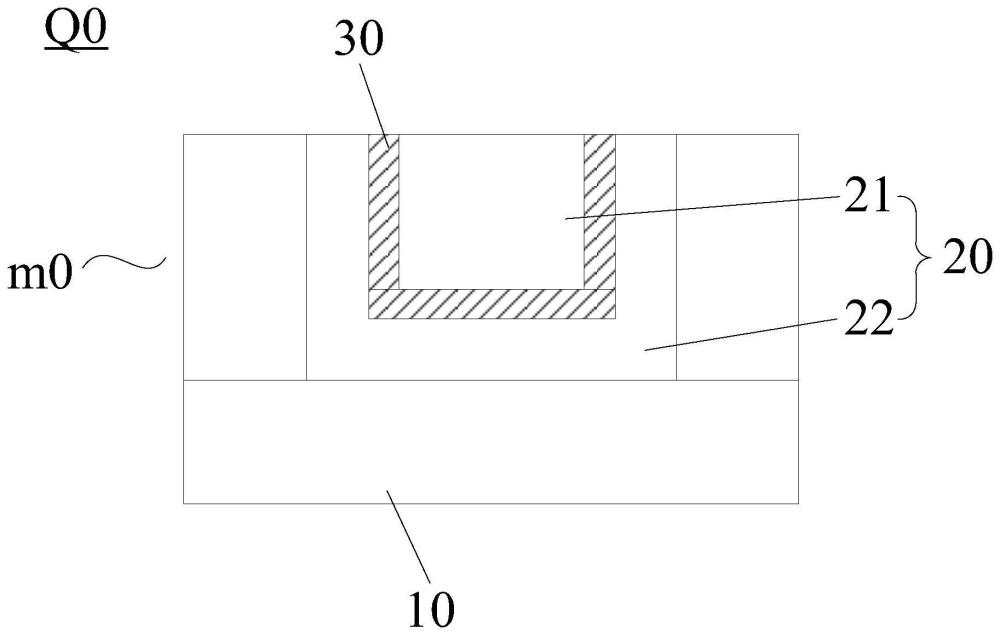

2、第一方面,本技术实施例提供了一种芯片,包括:衬底、以及位于衬底之上的至少一层布线层,至少部分所述布线层中设有用于进行扎针测试的导电端子;其中,导电端子中设置有导电阻挡层,导电阻挡层将导电端子分割为第一导电结构和第二导电结构,第一导电结构位于第二导电结构远离衬底一侧的至少部分表面之上,也即第一导电结构位于第二导电结构的至少部分表面的上部,衬底位于第二导电结构的下部,从而通过导电阻挡层将导电端子一分为二。

3、其中,导电阻挡层与导电端子的刻蚀选择比不同,使得在对第一导电结构进行刻蚀处理时,并不会或很难刻蚀掉导电阻挡层,并且,刻蚀选择比的差异越大,导电阻挡层就越难被刻蚀,导电阻挡层的保护阻隔作用就越强,从而可以通过设置导电阻挡层避免第二导电结构被刻蚀,为刻蚀处理提供了边界,对导电阻挡层之下的结构进行较好的保护,避免出现过腐蚀的现象,提高了芯片的制作良率。

4、应理解,刻蚀选择比指的是:在同一刻蚀条件下,一种材料与另一种材料相对刻蚀速率的快慢,且刻蚀选择比定义为:被刻蚀材料的刻蚀速率与另一种材料的刻蚀速率的比;如果材料a相对于材料b的刻蚀选择比较高,表示材料a与材料b相比刻蚀速率较快,材料a较容易地被刻蚀掉,材料b不太容易被刻蚀。刻蚀选择比的差异可以理解为刻蚀速率的差异,而制作材料的选择和刻蚀工艺等因素均对刻蚀速率产生影响,所以在本技术实施例中,只要能够保证导电阻挡层与导电端子的刻蚀选择比不同,实现导电阻挡层避免第二导电结构被刻蚀即可,对于具体的刻蚀选择比的设置,在此不作限定。

5、并且,通过设置导电阻挡层,在刻蚀处理时若将第一导电结构刻穿而到达导电阻挡层时,因导电阻挡层提供了刻蚀边界,所以可以较好地控制刻蚀区域的界面形态,这样不仅便于对刻蚀区域进行填埋,还可以在器件堆叠时降低堆叠界面的厚度,增加芯片的散热功能。

6、此外,为了提高了芯片的制作良率、以及较好地控制刻蚀区域的界面形态,仅需要在导电端子中设置导电阻挡层即可,如此可以降低芯片的制作难度,还可以降低芯片的制作成本,从而可以在低成本下实现上述目的。

7、在一些实施例中,在选择导电阻挡层的制作材料时,可以选择金属材料或金属复合材料,其中,金属材料可以但不限于包括钛和钽等其他金属,金属复合材料可以但不限于包括氮化钛和氮化钽等其他金属复合物。并且,可以从上述金属和上述金属复合物中选择其中一种材料制作导电阻挡层,形成单层材料构成的导电阻挡层;或者,可以从上述金属和上述金属复合物中选择至少两种来制作导电阻挡层,形成由堆叠的多层材料构成的导电阻挡层,以满足不同应用场景的需要,提高设计的灵活性。

8、在一些实施例中,在选择导电端子的制作材料时,同样可以选择金属材料或金属复合材料,其中,金属材料可以但不限于包括钨、铜和铝等其他金属,金属复合材料可以但不限于包括铜铝合金等其他金属复合物。并且,可以从上述金属和上述金属复合物中选择其中一种材料制作导电端子,形成单层材料构成的导电端子;或者,可以从上述金属和上述金属复合物中选择至少两种来制作导电端子,形成由堆叠的多层材料构成的导电端子,以满足不同应用场景的需要,提高设计的灵活性。

9、并且,在一些实施例中,第一导电结构和第二导电结构的制作材料可以设置为相同,当然也可以设置为不同,但需要保证第一导电结构和导电阻挡层的制作材料的刻蚀选择比不同,从而可以通过导电阻挡层对第二导电结构实现保护。

10、在一些实施例中,在对导电阻挡层的形状进行设置时,可以根据导电端子的尺寸、刻蚀工艺、导电阻挡层的制作难度等因素进行设置,例如:在垂直于衬底表面的平面上,导电阻挡层的截面形状可以设置为u字型、一字型或l型等其他形状,只要能够通过导电阻挡层阻挡第二导电结构被刻蚀即可,对于导电阻挡层的具体形状,在此并不限定。

11、在一些实施例中,导电阻挡层的厚度可以设置为10埃至1000埃。这样可以避免导电阻挡层过薄时无法起到较好的阻挡作用,还可以避免导电阻挡层较厚时增加制作难度和制作成本。

12、并且,第一导电结构的厚度与第二导电结构的厚度可以相同,此时导电阻挡层位于导电端子的中间位置;

13、当然,第一导电结构的厚度与第二导电结构的厚度还可以不同;其中,第一导电结构的厚度最小可以设置为500埃,第二导电结构的厚度最小可以设置为500埃。这样设置的原因在于:

14、如果第二导电结构中某些位置的厚度过小,且在该位置之上的导电阻挡层较薄时,在进行刻蚀处理的过程中,可能会将该位置处的导电阻挡层刻蚀掉,进而刻蚀掉该位置处的第二导电结构,继而对该位置处位于第二导电结构下部的其他结构造成不利影响;

15、如果第一导电结构中某些位置的厚度过大,必然会导致该位置处的第二导电结构的厚度过小;如果第一导电结构中某些位置的厚度过小,在测试针扎入第一导电结构时,可能会刺穿第一导电结构而对导电阻挡层造成损坏,进而在后续的刻蚀处理时导电阻挡层则无法提高较好地保护;

16、因此,通过第一导电结构和第二导电结构的厚度设置,使得第一导电结构和第二导电结构具有较合适的尺寸,不仅可以避免测试针的扎入而破坏导电阻挡层,还可以使得导电阻挡层对除第一导电结构之外的结构进行较好地保护,从而有利于提高芯片的制作良率。

17、在一些实施例中,在导电端子所在的布线层之上还设置有导电连接件时,导电端子与导电连接件通过第一绝缘层间隔开,第一绝缘层中设置有第一接触孔,导电端子与导电连接件通过第一接触孔连接。这样,可以实现导电端子和导电连接件的电连接关系。

18、在一些实施例中,在对第一接触孔的位置进行设置时,可以包括以下几种情况:

19、情况1:第一接触孔位于裸露部之上。

20、导电端子所在的布线层中,除导电端子之外的部分可以采用绝缘材料填充,若将填充的这部分绝缘材料称之为补充部时,导电端子和补充部构成了该布线层;并且,如果该布线层中设置有多个导电端子时,补充部可以将各导电端子间隔开,以避免各导电端子短接。当然,在本技术实施例中,并不限定布线层中设置的导电端子的数量,具体可以根据实际需要进行设置。

21、第一导电结构和/或第二导电结构具有位于第一导电层远离衬底一侧表面的裸露部,其中该裸露部可以理解为:第一导电结构和/或第二导电结构中与补充部远离衬底的一侧表面平齐的表面;那么第一接触孔可以设置于裸露部之上,也即第一接触孔可以设置于第一导电结构的裸露部之上;或设置于第二导电结构的裸露部之上;又或者第一接触孔设置有多个时,部分第一接触孔设于第一导电结构的裸露部之上,其余部分第一接触孔设于第二导电结构的裸露部之上。

22、由于第一导电结构和第二导电结构为导电端子中的一部分,所以第一导电结构和第二导电结构也均是导电的,在第一接触孔位于第一导电结构和/或第二导电结构的裸露部之上时,可以保证导电连接件通过第一接触孔与第一导电结构和/或第二导电结构直接接触,从而实现导电连接件与导电端子电连接。

23、并且,在第一接触孔位于第一导电结构和/或第二导电结构的裸露部之上时,第一接触孔只需要贯穿第一绝缘层,这样可以降低第一接触孔的制作难度,避免在制作第一接触孔时对其他结构造成不良影响,从而在降低芯片的制作难度的同时,提高芯片的可靠性。

24、情况2:第一接触孔位于非裸露部之上。

25、如果导电端子作为测试pad被测试针扎过时,第一导电结构中可能会出现翘起,这时可以采用刻蚀工艺对翘起进行刻蚀处理,该刻蚀工艺可以为干法刻蚀、湿法刻蚀或其他用于实现刻蚀效果的工艺,以便于将翘起刻蚀掉,同时会在第一导电结构中留下凹槽,该凹槽的深度与刻蚀工艺相关,如果刻蚀的较深,可能会将第一导电结构穿透,使得凹槽的槽底为导电阻挡层,如果刻蚀的不深,可能不会穿透第一导电结构,这时凹槽的槽底依然为第一导电结构。

26、并且,如果导电阻挡层的截面形状为u字型时,在进行刻蚀处理时,可能会将第一导电结构全部刻蚀掉,此时在导电阻挡层的阻挡作用下,导电阻挡层围成的部分形成了凹槽,这时导电端子中仅存在第二导电结构和导电阻挡层,且凹槽的槽底和侧壁均为导电阻挡层。因此,对于凹槽的具体形状和深度,在本技术实施例中并不限定,具体可以根据刻蚀工艺而定。

27、这种情况下,在导电端子中形成了位于第一导电结构的凹槽,这时第一接触孔可以位于凹槽所处的区域,也即第一接触孔在衬底上的正投影位于凹槽在衬底上的正投影内。并且,在该情况2中,在凹槽内设置有填充部时,可以按照如下方式对第一接触孔进行设置:

28、方式1:

29、第一接触孔位于填充部之上,也即:第一接触孔的底部(即第一接触孔中朝向衬底的一端)位于填充部的顶部(也即填充部远离衬底的一侧表面)。

30、其中,填充部的顶部可以与补充部的表面平齐;

31、或者,填充部的顶部还可以低于补充部的表面,此时填充部并未将凹槽全部填满,未填满的部分可以在制作第一绝缘层时采用绝缘材料填充;

32、又或者,填充部中可以设有凹坑,第一接触孔的底部可以设于凹坑内,而凹坑内除第一接触孔的位置同样可以在制作第一绝缘层时采用绝缘材料填充。

33、此时,填充部的制作材料可以包括导电材料,使得填充部具有导电功能;不管填充部与第一导电结构直接接触,还是填充部与导电阻挡层直接接触,均可以实现填充部与导电端子的电连接,在导电连接件通过第一接触孔与填充部电连接时,可以实现导电连接件与导电端子的电连接。

34、如此,第一接触孔可以仅贯穿第一绝缘层,导电连接件可以通过第一接触孔与填充部电连接,由于填充部与导电端子电连接,所以实现了导电连接件通过第一接触孔与导电端子电连接,同时还可以降低第一接触孔的制作难度,降低芯片的制作成本。

35、方式2:

36、第一接触孔贯穿填充部,使得第一接触孔不仅可以贯穿第一绝缘层,还可以贯穿填充部。

37、其中,在该方式2中,填充部的顶部可以与补充部的表面平齐还可以低于补充部的表面,具体可以根据实际需要而定,在此并不限定。

38、并且,在凹槽的槽底为第一导电结构时,第一接触孔的底部与第一导电结构接触,此时导电连接件和第一导电结构可以通过第一接触孔实现电连接;

39、在凹槽的槽底为导电阻挡层时,第一接触孔的底部可以位于导电阻挡层的顶部(即远离衬底的一侧表面)或导电阻挡层的内部,此时导电连接件和导电阻挡层可以通过第一接触孔实现电连接;或者,第一接触孔的底部还可以位于第二导电结构的顶部(即远离衬底的一侧表面)或内部,使得第一接触孔依次贯穿了第一绝缘层、填充部和导电阻挡层,此时导电连接件和第二导电结构可以通过第一接触孔实现电连接。

40、也就是说,第一接触孔的底部既可以位于导电阻挡层的上方、内部或下方,具体可以根据实际情况而定,在此不作限定。

41、这时,填充部的制作材料可以包括介电材料,使得填充部具备绝缘性能;在一些实施例中,介电材料可以但不限于包括:氧化硅、氮化硅、碳化硅等介电材料。当然,填充部的制作材料还可以包括导电材料,只要能够实现填充效果即可,在此并不限定。

42、这样,不管采用上述方式1还是方式2,通过导电阻挡层的设置,可以极大地降低后续针痕和翘起处理工艺的工艺难度和风险,从而提高芯片的制作良率,避免在后续针痕和翘起处理时对芯片造成二次伤害;并且还可以在后续针痕和翘起处理工艺中对凹槽的底部轮廓上进行有效控制,从而便于实现堆叠设置。

43、总之,在具体实施时,可以根据实际需要采用上述情况1或情况2对第一接触孔进行设置,以满足不同应用场景的需要,提高设计的灵活性。

44、并且,在一种可能的实施方式中,第一接触孔(以及后续内容提及的第二接触孔)可以为via结构、tsv结构或其他形式的接触孔,只要能够实现两个导电结构的互联即可,对于第一接触孔的具体设置形式,在此不作限定。

45、需要指出的是,上述情况2中介绍了在导电端子中设有凹槽时第一接触孔的设置方式,而在上述情况1中并未提及凹槽,但是在一些实施例中,导电端子同样可以设有凹槽,且凹槽内可以设有填充部,这时裸露部可以理解为导电端子中未被凹槽占用的位置,由于第一接触孔位于裸露部之上,所以填充部可以采用任意材料制作,在此不作限定。

46、在一些实施例中,本技术可以应用至芯片堆叠的场景中,也可以应用至非堆叠场景中。

47、1、芯片堆叠场景。

48、在芯片堆叠场景中,各芯片可以沿着垂直于衬底表面的方向进行堆叠。

49、并且,在一些实施例中,可以通过各芯片中的导电连接件进行贴合。

50、在实际情况中,在芯片的制作过程中,可以包括前段工艺(即feol,front end ofthe line)和后段工艺(即beol,back end of the line),前段工艺一般为器件的制作工艺,例如但不限于晶体管的制作工艺,后段工艺一般为布线工艺,且在进行布线时可以包括至少一层布线层,以实现前段工艺中制作出的器件实现电连接。在本技术实施例中,导电端子可以位于后段工艺中的某个或某些布线层,或者位于后段工艺中的顶部布线层,以便于在对所在的布线层对应的器件的性能进行测试时提供测试pad。并且,在导电端子位于后段工艺中的布线层时,衬底可以理解为:起到支撑作用的基底与在制作导电端子之前形成在基底之上的各层结构的总和。

51、其中,在导电端子位于后段工艺中的顶部布线层,且在单个芯片制作完成(即完成了该芯片的后段工艺)后,可以在此基础之上再设置一重布线层,以便于通过重布线层实现多个芯片的堆叠;在这种应用场景下,导电连接件即位于重布线层,或者可以理解为导电连接件所在的膜层即为重布线层,重布线层可以设置有一层或多层,至少部分重布线层中可以设置有导电连接件;并且,导电连接件的结构可以设置为与导电端子的结构相同,即导电连接件中也可以设置有导电阻挡层,从而在实现多个芯片堆叠的同时,便于实现各重布线层的测试。当然,导电连接件的结构也可以与导电端子的结构不同,即导电连接件中不存在导电阻挡层,这样可以简化导电连接件的制作难度。

52、在另一种可能的实施方式中,除了可以通过导电连接件进行贴合之外,还可以在各芯片中均设置贴合部,贴合部采用导电材料制作,该贴合部与导电连接件可以通过第二绝缘层隔开,且通过第二接触孔连接,使得贴合部与导电连接件电连接并具有相同的电位;这样,各芯片中的贴合部贴合,可以实现各芯片的堆叠,以及各芯片的电连接关系。

53、其中,在贴合部所在膜层中,除了贴合部之外的区域采用介电材料制作,使得在两个芯片的堆叠界面存在导电材料与导电材料的贴合,以及介电材料与介电材料的贴合,这种贴合方式可以称之为hybrid bonding(即混合贴合)。

54、当然,在本技术实施例中,在两个芯片的堆叠界面可以仅存在介电材料与介电材料的贴合,也即可以在制作出第一绝缘层,且第一绝缘层采用介电材料制作时,将两个芯片的第一绝缘层贴合,或者可以在制作出第二绝缘层,且第二绝缘层采用介电材料制作时,将两个芯片的第二绝缘层贴合,这种贴合方式可以称之为fusion bonding(即熔融贴合),并且,在贴合之后可以制作tsv结构的通孔,以实现各芯片的电连接。

55、2、非堆叠场景。

56、在该场景中,导电连接件可以无需与另一个芯片进行堆叠贴合,可以用于实现其他功能,例如但不限于将导电端子中的电位通过导电连接件引出等,在此不作限定。

57、第二方面,本技术实施例还提供了一种芯片的制备方法,可以包括:

58、提供一衬底;

59、形成设置在衬底之上的至少一层布线层;其中,至少部分布线层中设有用于进行扎针测试的导电端子;导电端子内设有导电阻挡层,导电阻挡层与导电端子的刻蚀选择比不同;导电阻挡层将导电端子分割为第一导电结构和第二导电结构,第一导电结构设于第二导电结构远离衬底一侧的至少部分表面之上。

60、这样,导电阻挡层与导电端子的刻蚀选择比不同,使得在对第一导电结构进行刻蚀处理时,并不会或很难刻蚀掉导电阻挡层,并且,刻蚀选择比的差异越大,导电阻挡层就越难被刻蚀,导电阻挡层的保护阻隔作用就越强,从而可以通过设置导电阻挡层避免第二导电结构被刻蚀,为刻蚀处理提供了边界,对导电阻挡层之下的结构进行较好的保护,避免出现过腐蚀的现象,提高了芯片的制作良率。

61、并且,通过设置导电阻挡层,在刻蚀处理时若将第一导电结构刻穿而到达导电阻挡层时,因导电阻挡层提供了刻蚀边界,所以可以较好地控制刻蚀区域的界面形态,这样不仅便于对刻蚀区域进行填埋,还可以在器件堆叠时降低堆叠界面的厚度,增加芯片的散热功能。

62、在一些实施例中,形成设置在衬底之上包括导电端子的布线层,包括:

63、形成设置在衬底之上的第二导电结构和导线;

64、形成设置在第二导电结构之上的导电阻挡层;

65、形成设置在导电阻挡层之上的第一导电结构;第一导电结构和第二导电结构形成导电端子。

66、这样可以得到导电端子,以便于通过内部的导电阻挡层避免在进行刻蚀时第二导电结构被刻蚀,为刻蚀处理提供了边界,对导电阻挡层之下的结构进行较好的保护,避免出现过腐蚀的现象,提高了芯片的制作良率。

67、在一些实施例中,在制作导电阻挡层,且导电阻挡层的截面形状为一字型时,无需增加新的掩模版,可以采用制作第二导电结构的掩模版继续制作导电阻挡层,从而可以有效降低芯片的制作难度和制作成本。

68、在一些实施例中,在形成第一导电结构之后,制作方法还包括:

69、形成设置在导电端子表面的第一绝缘层;

70、刻蚀形成贯穿第一绝缘层的第一接触孔;

71、形成设置在第一绝缘层之上的导电连接件,且第一接触孔中填充有导电连接件的制作材料;导电连接件和导电端子通过第一接触孔连接。

72、在一些实施例中,第一绝缘层可以采用至少一层材料制作,例如,采用一层二氧化硅材料制作形成第一绝缘层,或者依次采用二氧化硅材料和氮化硅材料形成由两层材料构成的第一绝缘层,或者依次采用二氧化硅材料、氮化硅材料和二氧化硅材料形成由三层材料构成的第一绝缘层等等,具体可以根据实际需要而定,只要能够形成第一绝缘层即可,对于第一绝缘层的具体结构不作限定。

73、在一些实施例中,在第一导电结构未被测试针扎过时,可以在导电端子表面直接设置第一绝缘层;而在第一导电结构被测试针扎过时,第一导电结构的表面很可能出现翘起,这时:

74、在导电端子表面设置第一绝缘层之前,对第一导电结构进行刻蚀处理,使得形成位于第一导电结构的凹槽;并对凹槽进行填充,以在凹槽内形成填充部;

75、在填充部的制作材料为导电材料,且第一接触孔设计为仅贯穿第一绝缘层时,可以在导电端子表面直接设置第一绝缘层;或者,在填充部的制作材料包括介电材料,且在实现刻蚀形成贯穿第一绝缘层的第一接触孔时,可以刻蚀形成贯穿第一绝缘层和填充部的第一接触孔。

76、其中,在形成填充部时,可以参见上述芯片中的相关部分描述,在此不再详述。

77、在一些实施例中,若需要将各芯片堆叠设置时,还可以将各芯片中的导电连接件贴合。当然,除了采用导电连接件进行贴合之外,还可以在导电连接件之上设置贴合部,通过贴合部进行贴合。

78、如此,即可实现芯片的制备,使得制备出的芯片具有较好的可靠性,同时还可以对刻蚀区域的界面形态进行较好的控制,在填埋之后且进行芯片的堆叠时,可以降低堆叠界面的厚度,增加芯片的散热功能。

79、第三方面,本技术实施例还提供一种三维堆叠芯片,包括:堆叠设置的多个芯片,多个芯片中的至少部分可以为上述实施例中介绍的芯片,如全部芯片为上述实施例中介绍的芯片,或部分芯片为上述实施例中介绍的芯片,将这些芯片堆叠后,从而形成三维堆叠芯片。

80、应理解,堆叠设置的多个芯片,可以分配给不同的厂商进行分别制作,从而能有效保证各芯片的制作效率和质量。当然,也可以分配给同一家厂家进行制作,最后再将各芯片进行堆叠,实现三维堆叠芯片。

81、第四方面,本技术实施例还提供一种电子设备,包括pcb;

82、还包括:如上述内容所介绍的芯片和/或三维堆叠芯片,其中芯片和/或三维堆叠芯片设置在pcb的表面。

83、示例性地,该电子设备包括但不限于:智能手机、智能手表、平板电脑、vr设备、ar设备、车载设备、台式计算机、个人计算机、手持式计算机或个人数字助理。

- 还没有人留言评论。精彩留言会获得点赞!