N型及P型MOS管、CMOS电路、芯片及其制作方法与流程

本申请实施例涉及半导体技术,尤指n型及p型mos管、cmos电路、芯片及其制作方法。

背景技术:

1、集成电路技术的发展要求不断更新换代,每一代技术都能实现更高的电路密度。传统的平面cmos(互补场效应管)技术已经达到了极限。14nm以及更先进的技术节点被半立体的finfet结构取代,但如果超越5nm,finfet技术也可能遇到极限。业界正在研发立体的环栅晶体管结构,包括垂直环栅(vgaa)以及水平环栅(hgaa),也有人在研究双层水平环栅的cfet结构。

2、但环栅技术的加工非常复杂,还面临很难处理的浮体效应,能否批量生产,批量生产后成本对市场是否有吸引力,仍然有疑问。

技术实现思路

1、本申请实施例提供了一种n型及p型mos管、cmos电路、芯片及其制作方法,加工更简单,能够极大地提高电路密度,并消除浮体效应。

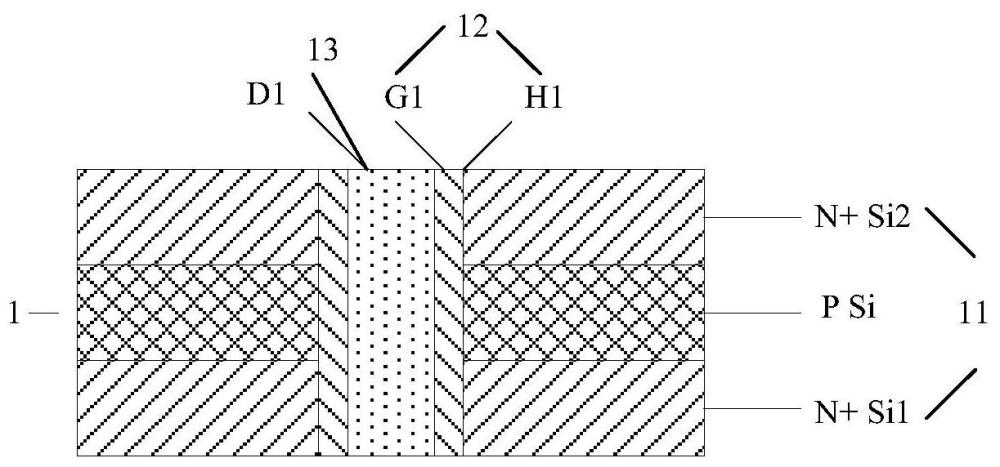

2、本申请实施例提供了一种n型mos管,可以包括:

3、由多层不同掺杂的硅si或锗硅gesi组成的第一基本结构,所述第一基本结构上具有在垂直方向具有贯穿孔的第一环形结构;以及,

4、位于所述第一环形结构内与所述第一环形结构绝缘的第一栅极;

5、所述第一基本结构包括:

6、第一层第一掺杂浓度的n型si;

7、设置于所述第一层第一掺杂浓度的n型si上的一层p型si或gesi;以及,

8、设置于所述p型si或gesi上的第二层第一掺杂浓度的n型si;

9、其中,所述第一层第一掺杂浓度的n型si和所述第二层第一掺杂浓度的n型si一个作为所述n型mos管的源极,另一个作为所述n型mos管的漏极;其中,所述n型mos管的所述源极和所述漏极的第一掺杂浓度高于所述n型mos管的沟道区域的第二掺杂浓度。

10、该实施例方案加工更简单,极大地提高了电路密度,并消除了浮体效应。

11、本申请实施例还提供了一种p型mos管,可以包括:

12、由多层不同掺杂的硅si或锗硅gesi组成的第二基本结构,所述第二基本结构上具有在垂直方向具有贯穿孔的第二环形结构;以及,

13、位于所述第二环形结构内与所述第二环形结构绝缘的第二栅极;所述第二基本结构包括:

14、第一层第一掺杂浓度的p型si;

15、设置于所述第一层第一掺杂浓度的p型si上的一层n型si或gesi;以及,

16、设置于所述n型si或gesi上的第二层第一掺杂浓度的p型硅si;

17、其中,所述第一层第一掺杂浓度的p型si和所述第二层第一掺杂浓度的p型si一个作为所述p型mos管的源极,另一个作为所述p型mos管的漏极;其中,所述p型mos管的所述源极和所述漏极的第一掺杂浓度高于所述p型mos管的沟道区域的第二掺杂浓度。

18、本申请实施例还提供了一种cmos电路,可以包括:所述的n型mos管以及所述的p型mos管;

19、所述p型mos管和所述n型mos管垂直衬底方向堆叠设置;

20、所述n型mos管的栅极和所述p型mos管的栅极连接且均沿着垂直衬底的方向延伸。

21、本申请实施例还提供了一种芯片,可以包括:一层或多层所述的cmos电路;每层cmos电路包括多个所述cmos电路;

22、处于同一层的多个所述cmos电路的源极或漏极在电路需要时相互连接。

23、本申请实施例还提供了一种cmos电路的制作方法,基于所述的cmos电路;所述方法可以包括:

24、将所述cmos电路中n型mos管的第一基本结构与所述cmos电路中p型mos管的第二基本结构垂直叠加;

25、在所述第一基本结构和所述第二基本结构上设置所述cmos电路的栅极。

26、本申请的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本申请而了解。本申请的其他优点可通过在说明书以及附图中所描述的方案来实现和获得。

技术特征:

1.一种n型mos管,其特征在于,包括:

2.一种p型mos管,其特征在于,包括:

3.一种cmos电路,其特征在于,包括:如权利要求1所述的n型mos管以及如权利要求2所述的p型mos管;

4.根据权利要求3所述的cmos电路,其特征在于,所述n型mos管和所述p型mos管之间设置有绝缘层;相互连接的所述n型mos管的栅极和所述p型mos管的栅极贯通所述绝缘层。

5.一种芯片,其特征在于,包括:一层或多层如权利要求3或4所述的cmos电路;每层cmos电路包括多个所述cmos电路;

6.根据权利要求5所述的芯片,其特征在于,当包含多层cmos电路时,还包括设置于层与层之间的垂直互联通孔。

7.一种cmos电路的制作方法,其特征在于,基于权利要求3或4所述的cmos电路;所述方法包括:

8.根据权利要求7所述的cmos电路的制作方法,其特征在于,所述p型mos管叠加于所述n型mos管的上方;

9.根据权利要求8所述的cmos电路的制作方法,其特征在于,在所述第一基本结构的上表面设置所述第二基本结构之前,所述方法还包括:

10.根据权利要求9所述的cmos电路的制作方法,其特征在于,所述方法还包括:

11.根据权利要求10所述的cmos电路的制作方法,其特征在于,所述在所述第一基本结构和所述第二基本结构上设置所述mos电路的栅极,包括:

12.根据权利要求10所述的mos电路的制作方法,其特征在于,所述在所述第一基本结构和所述第二基本结构上设置所述cmos电路的栅极,包括:

技术总结

本申请实施例提供了一种N型及P型MOS管、MOS电路、芯片及其制作方法,该N型MOS管包括:由多层不同掺杂的硅或锗硅组成的第一基本结构,第一基本结构上具有在垂直方向具有贯穿孔的第一环形结构;位于第一环形结构内与第一环形结构绝缘的第一栅极;第一基本结构包括第一层第一掺杂浓度的N型Si;第一层第一掺杂浓度的N型Si上的一层P型Si或GeSi;P型Si或GeSi上的第二层第一掺杂浓度的N型Si;第一层第一掺杂浓度的N型Si和第二层第一掺杂浓度的N型Si一个作为源极,一个作为漏极;源极和漏极的第一掺杂浓度高于沟道区域的第二掺杂浓度。该实施例方案加工更简单,极大地提高了电路密度,并消除了浮体效应。

技术研发人员:戴瑾,王文奇

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!