一种多栅极可控型IGBT芯片及其工作方法与流程

一种多栅极可控型igbt芯片及其工作方法

技术领域

1.本发明属于半导体器件制造领域,具体为一种多栅极可控型igbt芯片及其工作方法。

背景技术:

2.绝缘栅双极型晶体管(insulated gate bipolar transistor,igbt)是由双极型三极管(bipolar junction transistor,bjt)和绝缘栅型场效应管(metal oxide semiconductor,mos)组成的复合全控型电压驱动式功率半导体器件,兼有mosfet的高输入阻抗和gtr的低导通压降两方面的优点。具体来说:gtr饱和压降低、载流密度大,但驱动电流较大;mosfet驱动功率小、开关速度快,但导通压降大、载流密度小。igbt综合了以上两种器件的优点,即驱动功率小而饱和压降低,因而在电压为300v及以上的变流系统如交流电机、变频器、开关电源、照明电路、牵引传动等领域中得到了广泛应用。为实现更好的应用效果,igbt自发明以来就朝着高频率、低功耗、大电流密度的方向发展,但其多项性能参数之间却存在着相互制约的关系。

3.第一,饱和压降(vcesat)是衡量igbt是否过流的重要指标。igbt芯片在栅极驱动下、饱和导通时芯片集电极与发射极之间的电压降即为饱和压降。影响饱和压降的主要因素有:p+集电极与n+截止层之间的导通压降、漂移区电阻及栅极jfet区沟道电阻。其中,对于si衬底,其p+集电极与n+截止层之间的导通压降约0.7v。再者,漂移区电阻与漂移区厚度及掺杂浓度有关,使用场截止技术可有效降低漂移区厚度,从而降低漂移区电阻,同时达到耐压要求。另外,使用沟槽栅技术可降低栅极jfet区沟道电阻,具体来说,栅极的宽度越宽、栅极长度与源极长度之间的比例越大、沟道电阻越小,从而使得饱和压降低;但是随着栅极的宽度越宽、栅极长度与源极长度之间的比例越大,栅极与集电极的正对面积也会越大,即其米勒电容越大;米勒电容所带来的米勒效应会导致igbt在实际使用中表现为功耗增加、系统稳定性降低等缺点。因此,igbt芯片存在着栅极jfet区沟道电阻越小、米勒电容越大的负面制约关系,即因栅极jfet区沟道电阻引起的饱和压降与米勒电容之间存在负面制约关系。

4.第二,耐短路能力是衡量igbt芯片性能质量的重要指标,短路条件下,器件温度升高,当温度达到一个临界值时,器件会出现破坏性失效,同时集电极电流瞬间增大,在破坏性失效之前、器件所能承受的最大短路时间即代表其耐短路能力。由b. j. baliga, fundamentals of power semiconductor devices. newyork,ny,usa:springer,2008中,可得:t

scsoa

=[(t

cr-t

hs

)w

si

cv]/(k

tjc,satvcs

)上式中,t

scsoa

是器件所能承受的最大短路时间;t

hs

是器件初始温度;t

cr

是器件失效临界温度;w

si

是硅片厚度;cv是容积比热;k

t

代表器件的非均匀温度系数;j

c,sat

是初始电流密度;v

cs

是集电极与发射极之间的电压。基于该公式,可得器件的耐短路时间与电流密度为负相关的关系。因此,igbt芯片朝大电流密度方向发展的同时,其耐短路能力却越来越

弱。

[0005]

综上所述,如何优化各项性能参数之间的折衷关系,是在igbt芯片设计和生产过程中不可避免的问题。然而在现有的市场和技术中,常规igbt芯片流片后,其各项性能参数就已经确定,无法再调节其各项性能参数之间的折衷关系;由此,会使得所制成的igbt芯片在实际使用中受到较多的限制,且无法发挥最好的效果,甚至是产生一定的负面影响。

技术实现要素:

[0006]

本发明的目的在于提供一种多栅极可控型igbt芯片及其工作方法,以解决上述背景技术中所提到的问题:即现有技术中,由于常规igbt芯片流片后、其各项性能参数就已经确定,从而导致所制成的igbt芯片在实际使用中受到较多的限制。

[0007]

本发明是采用以下技术方案实现的:一种多栅极可控型igbt芯片,包括芯片主体,所述芯片主体的内部设有多组沟槽,每组沟槽内有n个栅极沟槽,芯片主体的一面上设有n个栅极和发射极,芯片主体的另一面上设有集电极;n个栅极沟槽与n个栅极对应连接,其中n≥2。

[0008]

在多栅极可控型igbt芯片的流片过程中,可以灵活调节栅极和栅极沟槽的数量,比如n取3时,则3个栅极沟槽为一组,3个栅极沟槽分别连接3个栅极;n取5时,则5个栅极沟槽为一组,5个栅极沟槽分别连接5个栅极;需要特别指出的是,每组的第一个沟槽均连接相对应的同一个栅极,比如沟槽组a的沟槽1连接栅极1,沟槽组b的沟槽1也连接栅极1。因此,对于这种多栅极的igbt芯片,能够通过改变其与外部栅极驱动相连接的栅极数量,从而相对改变igbt芯片饱和压降的高低和米勒电容的大小、以及电流密度的大小和耐短路时间的长短。

[0009]

进一步的,所述n个栅极沟槽上均开设栅极接触孔。在栅极沟槽上开栅极接触孔后,栅finger或栅bus可穿过栅极接触孔将栅极沟槽与栅极连接。

[0010]

进一步的,所述栅极沟槽为条形或其他多边形。本发明不对栅极沟槽的具体形状做限制,栅极沟槽可为长条形、方形、正六边形等其他形状;另外,本发明不对芯片的具体材料做限制,可为碳化硅、氮化镓等其他半导体材料。

[0011]

一种多栅极可控型igbt芯片的工作方法,应用于以上所述的一种多栅极可控型igbt芯片,包括全部栅极沟槽导通模式、部分栅极沟槽导通模式、单独栅极沟槽导通模式和屏蔽沟槽栅结构模式。基于多栅极可控型igbt芯片的结构,该芯片在实际使用时,可根据使用需求来灵活匹配工作模式,不同的工作模式对应不同的性能参数大小。

[0012]

进一步的,所述全部栅极沟槽导通模式下,n个栅极均与外部栅极驱动相连接。n个栅极均与外部栅极驱动相连接时,全部栅极沟槽导通,使得jfet区沟道电阻最小、即igbt芯片的饱和压降最小,同时igbt芯片的电流密度最大;这种情况下,芯片耐短路时间与电流密度负相关、为最短,栅极与集电极正对面积最大、即米勒电容最大。

[0013]

进一步的,所述部分栅极沟槽导通模式下, nm个栅极与外部栅极驱动相连接,其余栅极悬空,其中2≤nm《n。部分栅极沟槽导通模式与全部栅极沟槽导通模式相比,只有部分jfet区沟道打开,因此jfet区沟道电阻变大、即igbt芯片的饱和压降变大,同时igbt芯片的电流密度变大;这种情况下,芯片耐短路时间变长,米勒电容降低。

[0014]

进一步的,所述单独栅极沟槽导通模式下,1个栅极与外部栅极驱动相连接,其余

栅极悬空。1个栅极与外部栅极驱动相连接时,只有最少的栅极沟槽导通,使得jfet区沟道电阻最大、即igbt芯片的饱和压降最大,同时igbt芯片的电流密度最小;这种情况下,芯片的耐短路时间最长,米勒电容最小。

[0015]

进一步的,所述屏蔽沟槽栅结构模式下,n

l

个栅极与外部栅极驱动相连接,其余栅极与发射极相连接,其中 1≤ n

l 《n。这种情况下,igbt芯片内部形成屏蔽栅结构,屏蔽栅连接发射极,降低了栅极长度与源极长度之间的比例,可进一步降低米勒电容,从而降低开通损耗。

[0016]

本发明实现的有益效果是:通过在igbt芯片表面开设数量可调的多个栅极,使流片后制成的芯片具有多种工作模式;与现有的、在流片后各项性能参数就已经确定的常规igbt芯片相比,本多栅极芯片为可控型,即在实际使用时、可根据使用需求来灵活匹配工作模式,不同的工作模式对应不同的性能参数大小。因此,本芯片在流片后可调节其各项性能参数之间的折衷关系,从而有助于igbt芯片发挥最好的效果,并且制作简单、可靠性高。

附图说明

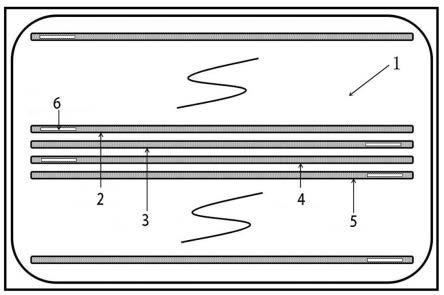

[0017]

图1是本发明实施例中所述芯片的内部结构示意图;图2是本发明实施例中所述芯片的正面结构示意图;图3是本发明实施例中所述工作模式a下的芯片打线连接示意图;图4是本发明实施例中所述工作模式b下的芯片打线连接示意图;图5是本发明实施例中所述工作模式c下的芯片打线连接示意图;图6是本发明实施例中所述工作模式d下的芯片打线连接示意图;图7是本发明实施例中所述工作模式d下的芯片内部结构示意图。

[0018]

图中:1、芯片主体;2、栅极沟槽ⅰ;3、栅极沟槽ⅱ;4、栅极沟槽ⅲ;5、栅极沟槽ⅳ;6、栅极接触孔;7、发射极;8、集电极。

具体实施方式

[0019]

为清楚说明本发明中的方案,下面结合附图做进一步说明:请参照图1至图2,一种四栅极可控型igbt芯片,包括芯片主体1;芯片主体1的内部设有条形栅极沟槽,每4条栅极沟槽为一组,图1中所示的一组沟槽包括栅极沟槽ⅰ2、栅极沟槽ⅱ3、栅极沟槽ⅲ4、栅极沟槽ⅳ5;上述4条栅极沟槽上的一端均开设有栅极接触孔6,4个栅极接触孔6交错分布;栅多晶硅丝(或金属丝)穿过栅极接触孔6,使栅极沟槽ⅰ2与栅极g1连接、栅极沟槽ⅱ3与栅极g2连接、栅极沟槽ⅲ4与栅极g3连接、栅极沟槽ⅳ5与栅极g4连接;如图2所示,具有上述结构的igbt芯片流片完成后,栅极g1、栅极g2、栅极g3、栅极g4均匀分布在芯片主体1正面的4个角上,另外芯片主体1的正面和背面分别设有发射极7和集电极8。

[0020]

一种四栅极可控型igbt芯片的工作方法,应用于以上所述的四栅极可控型igbt芯片,具体包括如下4种工作模式:工作模式a:如图3所示,4个栅极均与外部栅极驱动相连接,此时4条栅极沟槽全部导通,使得jfet区沟道电阻最小、即igbt芯片的饱和压降最小,同时igbt芯片的电流密度最大;芯片耐短路时间最短,米勒电容最大。

[0021]

工作模式b:如图4所示,栅极g1和栅极g3与外部栅极驱动相连接,栅极g2和栅极g4悬空,与工作模式a相比,此时只有部分jfet区沟道打开,因此jfet区沟道电阻变大、即igbt芯片的饱和压降变大,同时igbt芯片的电流密度变小;芯片耐短路时间变长,米勒电容降低。

[0022]

工作模式c:如图5所示,栅极g1与外部栅极驱动相连接,其余3个栅极悬空,即只有最少的1条栅极沟槽导通,使得jfet区沟道电阻最大、即igbt芯片的饱和压降最大,同时igbt芯片的电流密度最小;芯片的耐短路时间最长,米勒电容最小。

[0023]

工作模式d:如图6所示,栅极g1和栅极g3与外部栅极驱动相连接,栅极g2和栅极g4与发射极7连接;这种情况下,igbt芯片内部形成如图7所示的屏蔽栅结构,屏蔽栅连接发射极7,降低了栅极长度与源极长度之间的比例,可进一步降低米勒电容,从而降低开通损耗。

[0024]

综上所述,本四栅极芯片在实际使用时,可根据使用需求来灵活匹配工作模式,不同的工作模式对应不同的性能参数;因此,本芯片在流片后可调节其各项性能参数之间的折衷关系,从而能够发挥最好的效果。

[0025]

当然,上述内容仅为本发明的较佳实施例,不能被认为用于限定对本发明的实施例范围。本发明也并不仅限于上述举例,本技术领域的普通技术人员在本发明的实质范围内所做出的均等变化与改进等,均应归属于本发明的专利涵盖范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1