一种高稳定性的GaN器件以及GaN桥式集成电路

本发明涉及高稳定性的gan器件以及gan桥式电路的集成方法,属于电力电子器件领域。

背景技术:

1、在gan器件中可以利用极化效应在势垒层和沟道层间形成一层高电子迁移率的二维电子气沟道,因此,gan功率器件可以实现低的导通电阻和高的工作频率。然而,gan功率器件经过关断态漏极高耐压后,缓冲层中会形成负电荷积累,导致器件的导通电阻增大,即出现电流崩塌效应。同时,作为分立器件在互连过程中的寄生效应会限制gan器件的工作频率。通过gan功率器件的单片集成,可以进一步提升电路工作频率,但是在常规的gan-on-si外延平台中,单片集成会被衬底效应所限制,衬底效应会导致器件导通特性严重退化。

2、目前,一种p-gan和欧姆电极混合的漏极技术被提出(h.okita,m.hikita,a.nishio,t.sato,k.matsunaga,h.matsuo,m.mannoh,and y.uemoto,“through recessedand regrowth gate technology for realizing process stability of gan-gits”,inproc.ispsd,prague,czech republic,june 2016,pp.23-26),通过关态在漏极一侧注入空穴来抑制电流崩塌效应,然后该器件需要再生长gan技术,该工艺复杂且成本更高。

3、目前,一种gan-on-soi技术被提出(t.cosnier et al.,“200v gan-on-soi smartpower platform for monolithic gan power ics”,ieee international electrondevices meeting(iedm),2021,pp.5.1.1-5.1.4),通过氧化层的绝缘特性来限制衬底效应,然而绝缘层上硅(soi)技术的成本更高,且技术工艺复杂。

技术实现思路

1、为了实现高稳定性、低电流崩塌效应的gan器件,本发明提出了一种新的gan器件结构,该器件结构对电流崩塌效应有抑制作用。同时,该器件实现了对衬底效应的抑制作用,基于本发明提出的器件,本发明再提出一种新的gan桥式电路集成方法。

2、本发明的技术方案如下:

3、本发明的gan器件是在传统的hemt增强型器件结构基础上,在沟道层和缓冲层之间插入了一个背部阻挡层,沟道层和背部阻挡层之间可以形成一层额外的空穴扩展层,该背部阻挡层可以在外延生长中通过mocvd(金属有机化学气相淀积)来制备。

4、上述背部阻挡层的材料可以是铝镓氮、氮化铝、氮化铟和氮化铝铟镓中的一种或多种。从能带角度看,该背部阻挡层的价带顶要低于沟道层的价带顶,从而可以阻挡空穴注入到衬底中。所述背部阻挡层的厚度为1~100nm,优选的范围为15~25nm。

5、如图1所示,本发明典型的gan器件结构包括衬底以及在衬底上依次层叠的过渡层、缓冲层、背部阻挡层、沟道层和势垒层,源极和漏极设置在势垒层上的有源区内,栅极位于源极和漏极之间。其中栅极和势垒层之间为空穴注入层(见图1中s01),空穴注入层为p型掺杂的半导体,如p型掺杂的氮化镓、铝镓氮、氮化铝、氮化铟等。

6、图2展示了该器件抑制电流崩塌效应和衬底效应的基本原理,当栅极(g)和源极(s)加正偏压时,空穴注入层会注入空穴至背部阻挡层,并被背部阻挡层阻挡,同时空穴会沿着背部阻挡层扩展,从而在背部阻挡层上表面形成一层导电的空穴扩展层,该空穴扩展层可以屏蔽缓冲层中的负电中心。不仅如此,该空穴扩展层还可以屏蔽衬底电压对二维电子气的调制作用,从而实现对衬底效应的抑制作用。

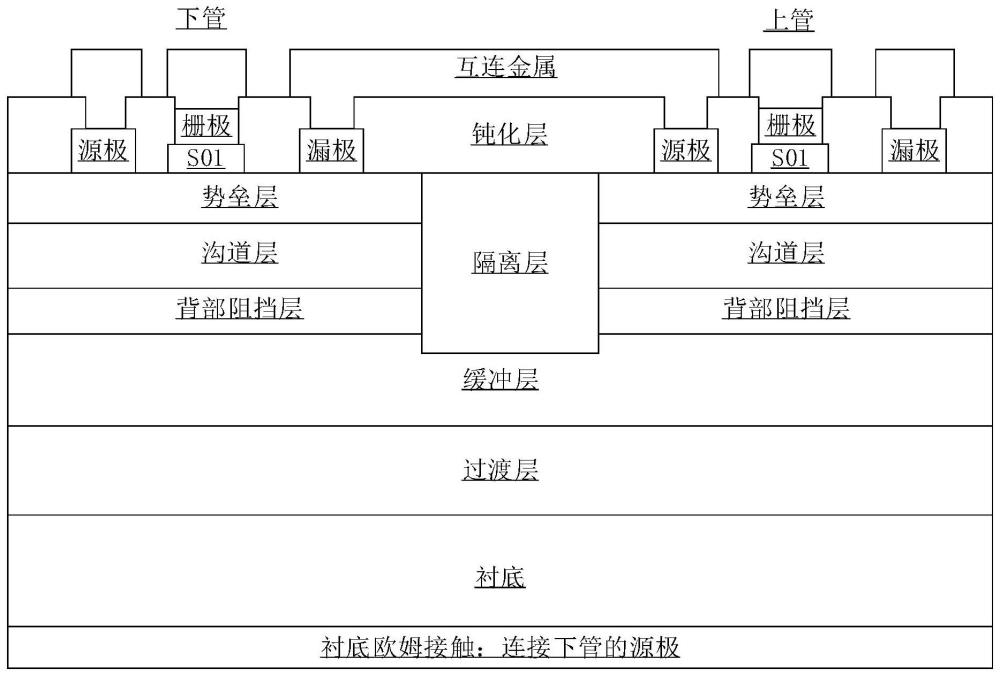

7、基于该器件对衬底效应的抑制作用,可以屏蔽集成平台中的衬底效应。如图4所示,是基于本发明的gan器件制备的一种gan桥式集成电路,包括制备在同一个衬底上的两个gan晶体管:上管和下管,上管的源极和下管的漏极相连,衬底背面的欧姆接触电极和下管的源极相连,上管受到的衬底负偏压效应会被抑制。又如图5所示,是基于本发明的gan器件制备的另一种gan桥式集成电路,包括制备在同一个衬底上的两个gan晶体管:上管和下管;上管的源极和下管的漏极相连,衬底背面的欧姆接触电极和上管的源极相连,下管受到的衬底正偏压效应会被抑制。

8、本发明的有益效果:

9、本发明提供的具有背部阻挡层和空穴扩展层的gan器件能有效地抑制电流崩塌效应和衬底效应,从而实现高动态稳定性、低动态导通电阻的gan器件。通过本发明所提供gan桥式电路集成平台,可以有效地降低器件互连时的寄生效应,提高gan电路的工作频率和工作效率,且该集成平台中的衬底效应可以被导电的空穴扩展层抑制。

技术特征:

1.一种gan器件,为hemt增强型器件,其特征在于,在沟道层和缓冲层之间插入了一个背部阻挡层。

2.如权利要求1所述的gan器件,其特征在于,所述gan器件包括衬底以及在衬底上依次层叠的过渡层、缓冲层、背部阻挡层、沟道层和势垒层,源极和漏极设置在势垒层上的有源区内,栅极位于源极和漏极之间,栅极和势垒层之间为空穴注入层。

3.如权利要求1或2所述的gan器件,其特征在于,所述背部阻挡层的材料是铝镓氮、氮化铝、氮化铟和氮化铝铟镓中的一种或多种。

4.如权利要求1或2所述的gan器件,其特征在于,所述背部阻挡层的厚度为1~100nm,优选为15~25nm。

5.如权利要求2所述的gan器件,其特征在于,所述空穴注入层为p型掺杂的半导体。

6.一种gan桥式集成电路,包括制备在同一个衬底上的两个gan晶体管:上管和下管;其中,上管的源极和下管的漏极相连;衬底浮空,或者在衬底背面制备欧姆接触电极和下管的源极相连,又或者,在衬底背面制备欧姆接触电极和上管的源极相连;其特征在于,上管和下管均在沟道层和缓冲层之间均插入了一个背部阻挡层。

7.如权利要求6所述的gan桥式集成电路,其特征在于,所述gan晶体管包括衬底以及在衬底上依次层叠的过渡层、缓冲层、背势垒层、沟道层和势垒层,源极和漏极设置在势垒层上的有源区内,栅极位于源极和漏极之间,栅极和势垒层之间为空穴注入层。

8.如权利要求7所述的gan桥式集成电路,其特征在于,所述空穴注入层为p型掺杂的半导体。

9.如权利要求6或7所述的gan桥式集成电路,其特征在于,所述背部阻挡层的材料是铝镓氮、氮化铝、氮化铟和氮化铝铟镓中的一种或多种。

10.如权利要求6或7所述的gan桥式集成电路,其特征在于,所述背部阻挡层的厚度为1~100nm,优选为15~25nm。

技术总结

本发明公开了一种高稳定性的GaN器件以及GaN桥式集成电路。所述GaN器件是在传统的HEMT增强型器件结构基础上,在沟道层和缓冲层之间插入了一个背部阻挡层。当栅极和源极加正偏压时,会在背部阻挡层上表面形成一层空穴扩展层,该空穴扩展层可以屏蔽缓冲层中的负电中心,还可以屏蔽衬底电压对二维电子气的调制作用,从而能有效地抑制电流崩塌效应和衬底效应,从而实现高动态稳定性、低动态导通电阻的GaN器件。基于该GaN器件的桥式集成电路可以有效地降低器件互连时的寄生效应,提高GaN电路的工作频率和工作效率,且集成平台中的衬底效应可以被导电的空穴扩展层抑制。

技术研发人员:魏进,杨俊杰

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!