形成半导体封装的方法和半导体封装与流程

本申请涉及半导体器件,并且特别地涉及形成半导体封装的方法和相应的半导体封装。

背景技术:

1、许多类型的半导体器件对诸如寄生互连电阻和电感、寄生电容耦合等的寄生电气效应高度灵敏。例如,开关、rf(射频)功率放大器、低噪声放大器(lna)、天线调谐器、混频器等都对寄生电气效应高度灵敏。用于减少封装的半导体器件上的寄生电气效应的技术往往导致更高的总成本、更大的封装尺寸、更复杂的制造过程、降低的器件性能等。

技术实现思路

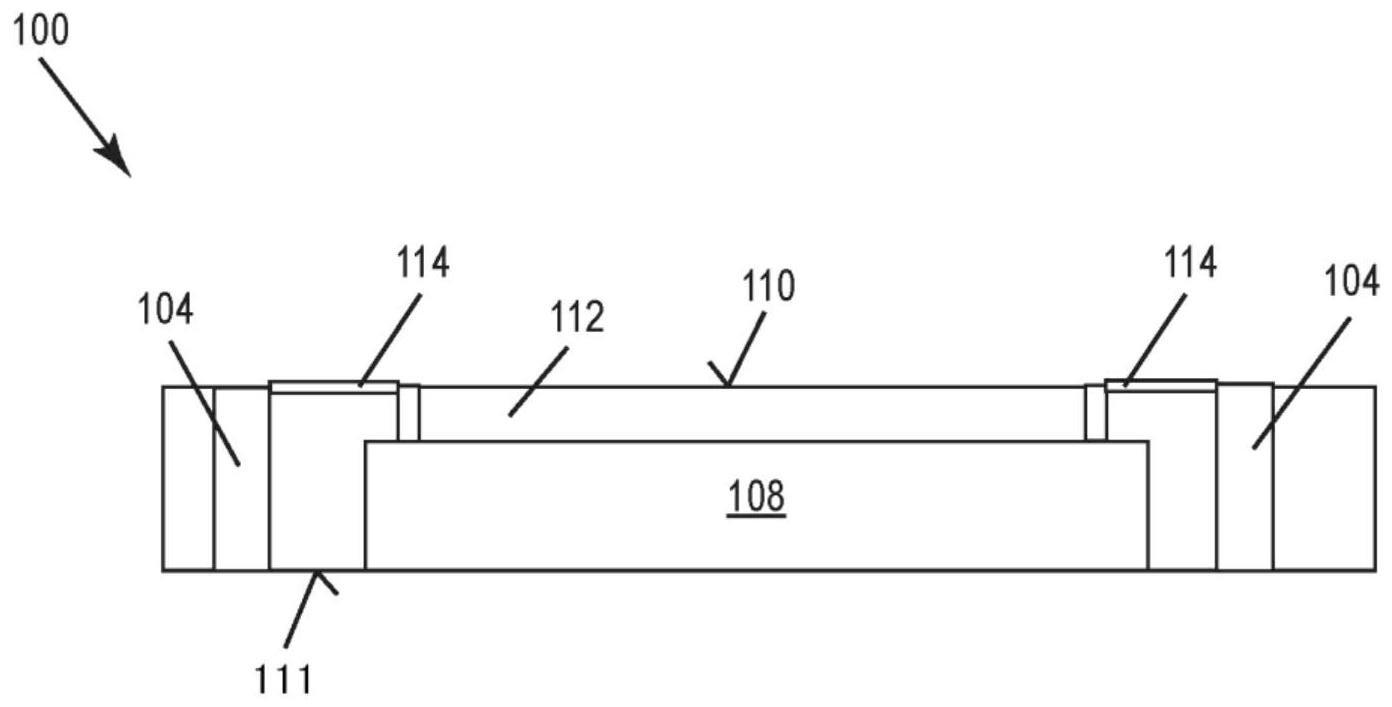

1、公开了一种形成半导体封装的方法。根据实施方式,该方法包括:提供金属基板,该金属基板包括基部和多个金属柱,基部是具有基本均匀厚度的平面盘(pad),多个金属柱各自从基部的平面上表面向上延伸;在金属基板的上表面上安装半导体管芯(die);在基部的上表面上形成电绝缘模制料(mold compound)的封装体;将半导体管芯的端子电连接至金属柱;以及去除基部,以便在封装体的第一表面处从金属柱形成封装触点。

2、单独地或组合地,封装触点包括金属柱的在封装体的第一表面和封装体的第二表面中的一者或两者处露出的端部,该第二表面与第一表面相对。

3、单独地或组合地,去除基部包括以下中的一项或更多项:化学蚀刻、机械研磨、铣削或激光。

4、单独地或组合地,半导体管芯在端子中的至少一些背离金属基板的情况下被安装,并且其中,将半导体管芯的端子电连接至金属柱包括:在形成封装体之前在半导体管芯的端子上设置背离基板的导电支柱;在形成封装体之后在封装体的第二表面处露出导电支柱的上端;以及在封装体的第二表面中形成导电轨道(track)。

5、单独地或组合地,该方法还包括用阻焊材料覆盖导电轨道。

6、单独地或组合地,电绝缘模制料包括可被激光激活的模制料,并且其中,形成导电轨道:包括将激光施加至封装体的第二表面从而在封装体的第二表面中形成被激光激活的迹线(trace),并且执行选择性地在被激光激活的迹线中形成导电轨道(track)的电镀工艺。

7、单独地或组合地,执行电镀工艺包括:执行形成导电轨道的种子层部分的无电镀工艺(electroless plating);以及执行在种子层部分之上形成导电轨道的较厚金属层部分的电镀工艺(electroplating process),该较厚金属层比种子层部分厚,并且其中,金属基板的基部在电镀工艺期间保持完好无损。

8、单独地或组合地,形成导电轨道包括激光辅助金属沉积,或喷墨金属印刷。

9、单独地或组合地,该方法还包括:在基部的上表面的第一区域中设置第一盘;在基部的上表面的第二区域中设置第二盘,第二盘包括金属;在第一盘上安装第一半导体管芯;以及在第二盘上安装第二半导体管芯,其中,在去除基部之后金属盘从封装体的第一表面露出并且在半导体封装的外表面与第二半导体管芯之间形成热传导路径。

10、单独地或组合地,第一盘是电绝缘结构。

11、单独地或组合地,第二盘是导电结构。

12、单独地或组合地,半导体管芯是逻辑器件,第二半导体管芯是功率开关器件,并且该方法还包括将半导体管芯的端子电连接至第二半导体管芯的端子。

13、单独地或组合地,金属基板被设置成包括在基部的上表面上的金属迹线,并且其中,金属迹线接触金属柱。

14、单独地或组合地,金属基板被设置成包括在金属基板的上表面上的管芯附接区域,其中,至少一个金属迹线在管芯附接区域与金属柱之间延伸,并且其中,半导体管芯被安装在管芯附接区域上,使得半导体管芯的端子之一面对金属轨迹并与金属迹线电连接。

15、单独地或组合地,金属迹线连接在金属柱中的第一个与金属柱中的第二个之间,其中,将半导体管芯的端子电连接至金属柱包括在封装体的与封装体的第一表面相对的第二表面中形成导电轨道,并且其中,导电轨道将半导体的端子之一电连接至金属柱中的第一个。

16、单独地或组合地,该方法还包括形成半导体封装的引线尖端检查特征,其中,形成引线尖端检查特征包括对封装体进行结构化以形成金属柱之一的露出侧壁,其中,露出侧壁在封装体的第一表面与封装体的与第一表面相对的第二表面之间完全延伸。

17、单独地或组合地,形成引线尖端检查特征还包括对封装体进行结构化以形成金属柱之一的第二露出侧壁,其中,第二露出侧壁在封装体的第一表面与第二表面之间完全延伸,并且其中,第一露出侧壁和第二露出侧壁彼此形成有角度的交叉。

18、单独地或组合地,该方法还包括:设置在基部的上表面上导电的第一盘,该第一盘包括主盘部分和在金属盘部分与至少一个金属柱之间延伸的连接件;以及在第一盘上安装半导体管芯,使得半导体管芯的端子中的至少一个面对主盘部分并电连接至主盘部分。

19、单独地或组合地,形成电气互连包括在形成封装体之后执行的金属结构化工艺。

20、公开了一种半导体封装。根据实施方式,半导体封装包括:半导体管芯;封装半导体管芯的、电绝缘模制料的封装体;多个金属柱,其在封装体的第二表面与封装体的与封装体第二表面相对的第一表面之间延伸;以及在半导体管芯的端子与金属柱之间的电连接,其中,从封装体的第二表面或第一表面露出的金属柱的端部形成半导体封装的封装触点。

21、单独地或组合地,封装体包括可被激光激活的模制料,并且其中,电互连件中的至少一些包括形成在封装体的第二表面中的导电轨道。

22、单独地或组合地,导电轨道包括较薄的种子层部分和在较薄的种子层部分的顶部的较厚部分,其中,较薄的种子层部分的厚度不大于1μm,并且其中,较厚部分的厚度为至少5μm。

23、单独地或组合地,该半导体封装还包括:在半导体封装的第一区域中的电绝缘盘;以及在半导体封装的第二区域中的金属盘;其中,半导体管芯被安装在电绝缘盘上,使得半导体管芯通过电绝缘盘与半导体封装的外表面电隔离,其中,半导体封装还包括被安装在金属盘上的第二半导体管芯,其中,金属盘在第一表面处从封装体露出,并且在半导体封装的外表面与第二半导体管芯之间形成热传导路径。

24、单独地或组合地,该半导体封装还包括:引线尖端检查特征,其中,引线尖端检查特征包括金属柱中的从封装体露出的一个金属柱的露出侧壁,其中,露出侧壁完全在封装体的第一表面与第二表面之间延伸。

技术特征:

1.一种形成半导体封装的方法,所述方法包括:

2.根据权利要求1所述的方法,其中,所述封装触点包括所述金属柱的端部中的在所述封装体的第一表面和所述封装体的第二表面中的一者或两者处露出的端部,所述第二表面与所述第一表面相对。

3.根据权利要求1所述的方法,其中,去除所述基部包括以下中的一种或更多种:化学蚀刻、机械研磨、铣削或激光。

4.根据权利要求1所述的方法,其中,所述第一半导体管芯被安装成使得所述端子中的至少一些端子背离所述金属基板,并且其中,将所述第一半导体管芯的端子电连接至所述金属柱包括:

5.根据权利要求4所述的方法,还包括:利用阻焊材料覆盖所述导电轨道。

6.根据权利要求4所述的方法,其中,所述电绝缘的模制料包括可被激光激活的模制料,并且其中,形成所述导电轨道包括:

7.根据权利要求6所述的方法,其中,执行所述电镀工艺包括:

8.根据权利要求4所述的方法,其中,形成所述导电轨道包括:

9.根据权利要求1所述的方法,还包括:

10.根据权利要求9所述的方法,其中,所述第一盘是电绝缘结构。

11.根据权利要求9所述的方法,其中,所述第一盘是导电结构。

12.根据权利要求9所述的方法,其中,所述第一半导体管芯是逻辑器件,其中,所述第二半导体管芯是功率开关器件,并且其中,所述方法还包括将所述第一半导体管芯的端子电连接至所述第二半导体管芯的端子。

13.根据权利要求1所述的方法,其中,所述金属基板被设置成在所述基部的上表面上包括金属迹线,并且其中,所述金属迹线接触所述金属柱。

14.根据权利要求13所述的方法,其中,所述金属基板被设置成在所述金属基板的上表面上包括管芯附接区域,其中,所述金属迹线在所述管芯附接区域与所述金属柱之间延伸,并且其中,所述第一半导体管芯被安装在所述管芯附接区域上,使得所述第一半导体管芯的端子之一面向所述金属迹线并与所述金属迹线电连接。

15.根据权利要求13所述的方法,其中,所述金属迹线被连接在所述金属柱中的第一金属柱与所述金属柱中的第二金属柱之间,其中,将所述第一半导体管芯的端子电连接至所述金属柱包括在所述封装体的与所述封装体的第一表面相对的第二表面中形成导电轨道,并且其中,所述导电轨道将所述第一半导体管芯的端子之一电连接至所述金属柱中的第一金属柱。

16.根据权利要求1所述的方法,还包括:形成所述半导体封装的引线尖端检查特征,其中,形成所述引线尖端检查特征包括将所述封装体构造成形成所述金属柱之一的第一露出侧壁,并且其中,所述第一露出侧壁完全在所述封装体的第一表面与所述封装体的与所述第一表面相对的第二表面之间延伸。

17.根据权利要求16所述的方法,其中,形成所述引线尖端检查特征还包括:将所述封装体构造成形成所述金属柱之一的第二露出侧壁,其中,所述第二露出侧壁完全在所述封装体的第一表面与第二表面之间延伸,并且其中,所述第一露出侧壁与所述第二露出侧壁彼此形成成角度的相交。

18.根据权利要求1所述的方法,还包括:

19.根据权利要求4所述的方法,其中,形成所述导电轨道包括在形成所述封装体之后执行的金属结构化工艺。

20.一种半导体封装,包括:

21.根据权利要求20所述的半导体封装,其中,所述封装体包括可被激光激活的模制料,并且其中,施加至所述封装体的激光能量在所述封装体的第二表面中形成导电轨道。

22.根据权利要求21所述的半导体封装,其中,所述导电轨道包括较薄的种子层部分和在所述较薄的种子层部分的顶部的较厚部分,其中,所述较薄的种子层部分的厚度不大于1μm,并且其中,所述较厚部分的厚度为至少5μm。

23.根据权利要求20所述的半导体封装,还包括:

24.根据权利要求20所述的半导体封装,还包括引线尖端检查特征,其中,所述引线尖端检查特征包括所述金属柱中之一的从所述封装体露出的露出侧壁,其中,所述露出侧壁完全在所述封装体的第一表面与第二表面之间延伸。

技术总结

公开了一种形成半导体封装的方法和半导体封装。该方法包括:设置具有基部和多个金属柱的金属基板,基部是具有基本上均匀厚度的平面盘,多个金属柱各自从基部的平面上表面向上延伸;在金属基板的上表面上安装第一半导体管芯;在基部的上表面上形成电绝缘的模制料的封装体;将第一半导体管芯的端子电连接至金属柱;以及去除基部,以在封装体的第一表面处从金属柱形成封装触点。

技术研发人员:张超发,托尔斯滕·迈尔,谢征林,沃恩·肯·达里尔韦,吕志鸿,李瑞家,诺莉扎·莫尔班,凯·什万·安德鲁索

受保护的技术使用者:英飞凌科技股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!