一种采用RDL技术降低封装基板层数的集成方法与流程

本发明属于微系统封装集成领域,具体涉及一种采用rdl技术降低封装基板层数的集成方法。

背景技术:

1、微系统封装集成技术是将多个芯片和其他组件都集成到同一个封装系统中,形成微系统芯片,该芯片可以作为电子系统或子系统运行。国防军工领域对高端器件和国产化替代有迫切需求。现代战争是以高科技武器装备为基础的信息化战争,军用电子信息处理系统是装备信息化、智能化、一体化发展的重要支撑,通过对型号电子系统的高度“优化、提炼和浓缩”,通过系统、芯片与工艺的协同设计使其在功能、性能密度、体积、重量和可靠性等方面得以大幅度提升,是电子系统升级换代、自主可控的“精髓”所在,对武器装备作战性能具有举足轻重的作用。特别是在世界新军事变革深入发展,作战模式逐步转向以突防为主,对电子信息处理系统在高动态、高实时运行模式下,提出了超高的性能体积比等要求,进而对信息微系统设计与制造提出了更高要求。现代战争中武器系统发展的目标是提高打击精度、提高毁伤效果和降低附带损害,同时降低己方人员、装备被敌方发现的几率,具有信息化争夺、网络化协同和智能化决策等特点,因此需要每个处于网络中的节点都需要具有探测感知、信息处理、数据传输和指令执行多种或全部能力。由于微系统封装集成产品集成了探测、通讯、处理、执行甚至能源等部分或全部功能,能极大的降低了武器装备体积和重量,在极其有限的空间内实现更快的运算速度,可以广泛应用于控制、导航、制导、计算组件、数据链、单兵装备和智能终端等多个领域,有效的满足未来作战新模式的需要,从而对武器装备的发展起到倍增器的作用。因此微系统封装集成对武器装备系统也具有重大意义。

2、目前微系统封装集成大量采用有机bt或abf基板进行集成,但由于目前行业产能紧张和国内工艺能力限制,超过6层的bt或abf基板存在交货周期长,制造风险高等问题。为提高微系统封装集成的实现性,降低集成设计对于基本设计复杂度和工艺能力的依赖,需要采用新的方法解决该问题。

技术实现思路

1、(一)要解决的技术问题

2、本发明要解决的技术问题是如何提供一种采用rdl技术降低封装基板层数的集成方法,以解决微系统封装集成大量采用有机bt或abf基板进行集成,但由于目前行业产能紧张和国内工艺能力限制,超过6层的bt或abf基板存在交货周期长,制造风险高等的问题。

3、(二)技术方案

4、为了解决上述技术问题,本发明提出一种采用rdl技术降低封装基板层数的集成方法,该方法包括如下步骤:

5、s11、根据微系统产品内多种芯片间互联关系的关联度,确定采用rdl层降低基板互联密度的两颗或多颗裸芯片,并对rdl层的走线进行设计开发;

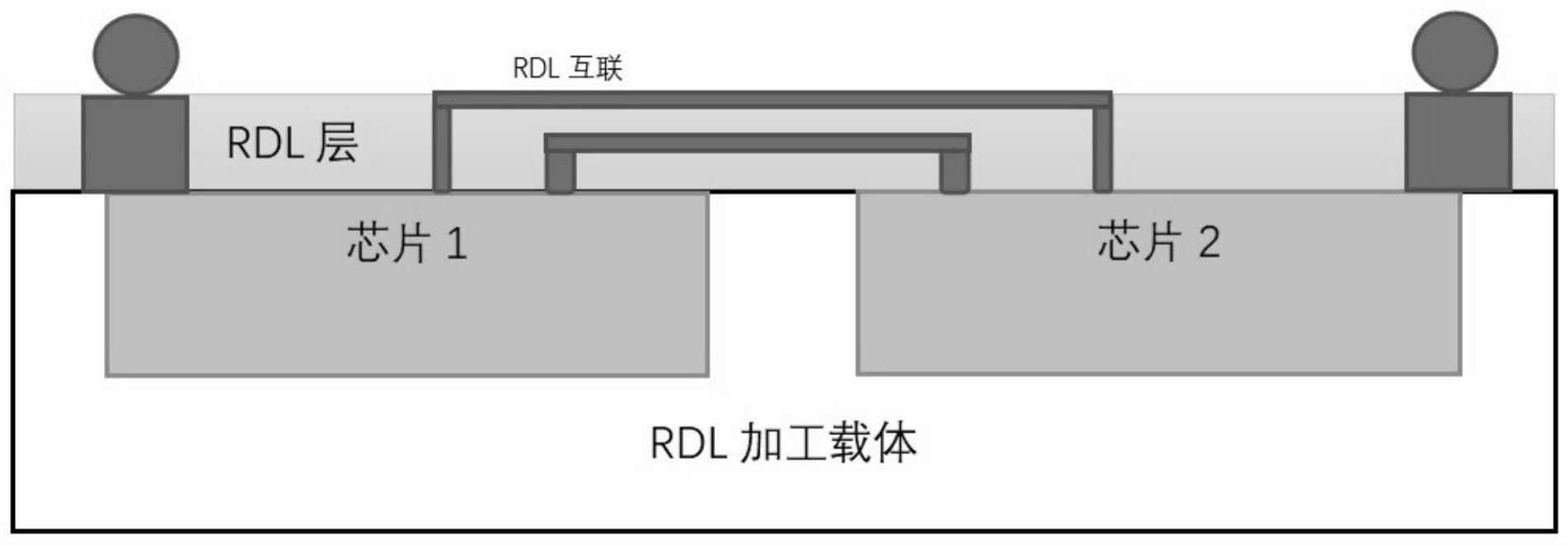

6、s12、将确定采用rdl层加工的芯片放入载体中,采用芯片光刻工艺加工rdl层,将两个芯片间的互联信号用rdl层进行互联,两个或多个芯片需要引出的信号形成rdl层上的pad点;

7、s13、重新按照做好rdl层的组合芯片进行微系统集成设计,从而降低基板的互联复杂度。

8、进一步地,所述步骤s11中,以最优信号路径的方式确定采用rdl层降低基板互联密度的两颗或多颗裸芯片。

9、进一步地,所述步骤s12中,载体为硅基载体。

10、进一步地,所述步骤s12中,载体为面板类载体。

11、本发明还提供一种采用rdl技术降低封装基板层数的集成方法,该方法包括如下步骤:

12、s21、根据微系统产品内多种芯片间互联关系的关联度,确定最优的采用rdl层降低基板互联密度的两颗或多颗裸芯片,并对rdl层的走线进行设计开发;

13、s22、重新按照做好rdl层的芯片模组进行微系统集成设计;

14、s23、将做好rdl层的芯片模组与其他不同封装类型的芯片倒装在微系统基板上进行二次集成。

15、进一步地,所述步骤s21中,以最优信号路径的方式确定采用rdl层降低基板互联密度的两颗或多颗裸芯片。

16、进一步地,所述步骤s21中,rdl层为两层或四层。

17、进一步地,所述步骤s21具体包括如下步骤:

18、s211、将确定采用rdl层加工的芯片放入已经加工好芯片安置凹槽的载体中;

19、s212、采用rdl加工工艺,将两个芯片间的互联信号用rdl层进行互联,两个或多个芯片需要引出的信号形成rdl层上的pad点;

20、s213、将完成rdl层和pad加工的载体材料按照最小尺寸进行切割,形成后续微系统集成应用的芯片模组。

21、进一步地,所述步骤s211中,载体为硅基载体。

22、进一步地,所述步骤s211中,载体为面板类载体。

23、(三)有益效果

24、本发明提出一种采用rdl技术降低封装基板层数的集成方法,本发明针对复杂微系统封装集成中普遍采用高密度复杂、多层、大尺寸封装基板的问题,采用在原有封装集成之前,对部分器件采用再布线层(rdl)技术互联好,之后再进行基板的集成,从而降低微系统封装集成中对于基板层数的需求,降低基板的设计难度和成本,缩短微系统产品的研发周期。

25、本发明涉及一种采用rdl技术降低封装基板层数的集成方法,可以有效降低系统封装设计中对于基板层数的需求,提高微系统封装集成的效率和可靠性,降低基板设计难度和成本。

技术特征:

1.一种采用rdl技术降低封装基板层数的集成方法,其特征在于,该方法包括如下步骤:

2.如权利要求1所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s11中,以最优信号路径的方式确定采用rdl层降低基板互联密度的两颗或多颗裸芯片。

3.如权利要求1所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s12中,载体为硅基载体。

4.如权利要求1所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s12中,载体为面板类载体。

5.一种采用rdl技术降低封装基板层数的集成方法,其特征在于,该方法包括如下步骤:

6.如权利要求5所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s21中,以最优信号路径的方式确定采用rdl层降低基板互联密度的两颗或多颗裸芯片。

7.如权利要求6所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s21中,rdl层为两层或四层。

8.如权利要求5-7任一项所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s21具体包括如下步骤:

9.如权利要求8所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s211中,载体为硅基载体。

10.如权利要求8所述的采用rdl技术降低封装基板层数的集成方法,其特征在于,所述步骤s211中,载体为面板类载体。

技术总结

本发明涉及一种采用RDL技术降低封装基板层数的集成方法,属于微系统封装集成领域。本发明根据微系统产品内多种芯片间互联关系的关联度,确定以最优信号路径的方式采用RDL层降低基板互联密度的两颗或多颗裸芯片,并对RDL层的走线进行设计开发;将确定采用RDL层加工的芯片放入载体中,采用芯片光刻工艺加工RDL层,将两个芯片间的互联信号用RDL层进行互联,两个或多个芯片需要引出的信号形成RDL层上的Pad点;重新按照做好RDL层的组合芯片进行微系统集成设计,从而降低基板的互联复杂度,可以有效降低基板的层数和密度。

技术研发人员:朱天成,章飚,曾永红,张楠,徐艺轩,朱琳,付月

受保护的技术使用者:天津津航计算技术研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!