一种碳化硅栅极氧化层的制备方法以及相应的器件

1.本发明涉及碳化硅技术领域,具体为一种碳化硅栅极氧化层的制备方法以及相应的器件。

背景技术:

2.碳化硅栅氧界面的状态对器件的性能有较大影响,如何有效低成本降低界面态和近界面缺陷是目前碳化硅mosfet商业化应用较为关注的问题,目前主流碳化硅栅氧工艺主要分两步,第一步利用高温热氧化或者化学气相沉积法形成栅氧,第二步使用no或者n2o退火对栅氧进行氮钝化。

3.高温热氧化法与化学气相沉积法在形成栅氧方面存在各自的优点与缺点:1、化学气相沉积法由于不需要高温加热环节而使得大规模生产成本更低,但生成的氧化层较高温热氧化法更加疏松造成漏电;2、高温热氧化法生成的sio2氧化层可能会导致sic与sio2界面处和氧化层侧近界面处的氧原子浓度低,从而形成氧空位、碳空位、碳间隙原子及团簇等缺陷。

技术实现要素:

4.本发明的目的在于克服根据现有制备方法制备得到的栅极氧化层存在缺陷的问题,提供了一种碳化硅栅极氧化层的制备方法以及相应的器件。

5.为了实现上述目的,本发明提供一种碳化硅栅极氧化层的制备方法,包括以下步骤:提供碳化硅外延;利用低压化学气相沉积法在所述碳化硅外延表面形成第一栅氧化层,再利用热氧化法透过第一栅氧化层在所述碳化硅外延表面形成第二栅氧化层,从而得到完整的栅极氧化层;其中,所述栅极氧化层包括位于所述碳化硅外延表面的第二栅氧化层和位于所述第二栅氧化层表面的第一栅氧化层,所述第一栅氧化层的厚度为所述栅极氧化层厚度的1/6—1/5。

6.作为一种可实施方式,在得到栅极氧化层之后还包括以下步骤:对所述栅极氧化层进行钝化。

7.作为一种可实施方式,对所述栅极氧化层进行钝化的步骤具体包括:采用no或者n2o退火对所述栅极氧化层进行钝化。

8.作为一种可实施方式,所述第一栅氧化层的厚度范围为10-15nm,所述栅极氧化层的厚度范围为55-70nm。

9.作为一种可实施方式,利用热氧化法在所述碳化硅外延表面形成第二栅氧化层的步骤具体包括:利用热氧化法使得o2透过疏松的第一栅氧化层到达碳化硅外延与第一栅氧化层的界面处,从而氧化所述碳化硅外延表面的碳化硅生成二氧化硅,得到更加致密的第二栅

氧化层。

10.相应的,本发明还提供一种mos电容器的制作方法,包括以下步骤:提供碳化硅外延;利用低压化学气相沉积法在所述碳化硅外延表面形成第一栅氧化层,再利用热氧化法透过第一栅氧化层在所述碳化硅外延表面形成第二栅氧化层,从而得到完整的栅极氧化层,其中,所述栅极氧化层包括位于所述碳化硅外延表面的第二栅氧化层和位于所述第二栅氧化层表面的第一栅氧化层,所述第一栅氧化层的厚度为所述栅极氧化层厚度的1/6—1/5;对所述栅极氧化层进行钝化,再基于后续工艺制备得到mos电容器。

11.作为一种可实施方式,利用热氧化法在所述碳化硅外延表面形成第二栅氧化层的步骤具体包括:利用热氧化法使得o2透过第一栅氧化层到达碳化硅外延与第一栅氧化层的界面处,从而氧化所述碳化硅外延表面的碳化硅生成二氧化硅,得到第二栅氧化层。

12.作为一种可实施方式,对所述栅极氧化层进行钝化的步骤具体包括:采用no或者n2o退火对所述栅极氧化层进行钝化。

13.相应的,本发明还提供一种mos电容器,所述mos电容器是采用所述mos电容器的制作方法形成的。

14.相应的,本发明还提供一种半导体器件,包括如所述碳化硅栅极氧化层的制作方法形成的栅极氧化层。

15.本发明的有益效果:本发明公开了一种碳化硅栅极氧化层的制备方法以及相应的器件,首先利用低压化学气相沉积法在所述碳化硅外延表面形成第一栅氧化层,再利用热氧化法透过第一栅氧化层在所述碳化硅外延表面形成第二栅氧化层,从而得到由第一栅氧化层和第二栅氧化层组成的栅极氧化层;其中,所述第一栅氧化层的厚度为所述栅极氧化层厚度的1/6—1/5;使得在降低碳空位等缺陷的同时又可以有效防止漏电及保证较高的栅氧可靠性。

附图说明

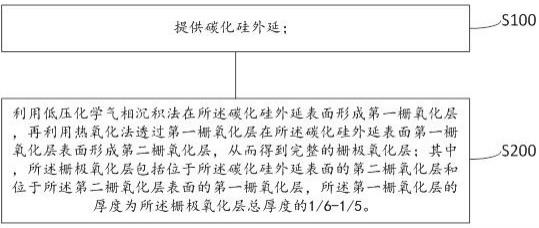

16.图1为本发明碳化硅栅极氧化层的制备方法步骤示意图;图2为本发明mos电容器的制备方法步骤示意图。

具体实施方式

17.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

18.参见图1,本实施例提供一种技术方案:一种碳化硅栅极氧化层的制备方法,包括以下步骤:步骤s100,提供碳化硅外延;步骤s200,利用低压化学气相沉积法在所述碳化硅外延表面形成第一栅氧化层,

再利用热氧化法透过第一栅氧化层在所述碳化硅外延表面形成第二栅氧化层,从而得到完整的栅极氧化层,其中,所述栅极氧化层包括位于所述碳化硅外延表面的第二栅氧化层和位于所述第二栅氧化层表面的第一栅氧化层,所述第一栅氧化层的厚度为所述栅极氧化层厚度的1/6—1/5;进一步地,在得到栅极氧化层之后还包括以下步骤:对所述栅极氧化层进行钝化。

19.所述碳化硅外延为半导体衬底表面形成的碳化硅外延层,所述半导体衬底为硅衬底、锗衬底、碳化硅衬底、玻璃衬底等。

20.其中本实施例选择使用低压化学气相沉积法,使得形成的第一栅氧化层的厚度更加均匀,不会因氧化层厚度不均导致器件性能急剧下降。

21.具体的,所述第一栅氧化层的厚度范围为10-15nm,所述栅极氧化层的厚度范围为55-70nm。

22.利用热氧化法在所述碳化硅外延表面形成第二栅氧化层的步骤具体包括:利用热氧化法使得o2透过疏松的第一栅氧化层到达碳化硅外延与第一栅氧化层的界面处,从而氧化所述碳化硅外延表面的碳化硅生成二氧化硅,得到更加致密的第二栅氧化层。

23.在现有技术中,采用单一高温热氧化法或者低压化学气相沉积法制备栅极氧化层都存在着各自的缺点,而本实施例有效的联合了两种方法各自的优点。

24.首先,申请人通过实验发现,虽然化学气相沉积法生成的氧化层较高温热氧化法更加疏松造成漏电,但是其实,化学气相沉积法生成的疏松sio2氧化层有利于氧分子或氧原子迁移到sic与sio2氧化层界面处,从而降低碳空位缺陷;而且,虽然热氧化法生成的sio2氧化层可能会导致sic与sio2氧化层界面处和氧化层侧近界面处的氧原子浓度低,从而形成氧空位、碳空位、碳间隙原子及团簇等缺陷,但是热氧化法生成的sio2氧化层足够致密,可以有效防止漏电及具有较高的栅氧可靠性。

25.因此,本实施例为了解决两种方式存在的问题,先在碳化硅外延表面用低压化学气相沉积法生长一层薄且疏松的sio2氧化层即第一栅氧化层,这样生成的sio2氧化层会比直接热氧化法生成的sio2氧化层质地稀疏,有利于氧分子或氧原子迁移到碳化硅外延表面的sic与sio2氧化层界面处,从而降低碳空位缺陷,从而避免由于sio2氧化层太过致密导致碳化硅外延表面的sic不能完全被氧化,生成氧空位、碳空位、碳间隙原子及团簇等缺陷;然后再采用热氧化法,o2将通过薄且疏松的sio2氧化层即第一栅氧化层到达碳化硅外延表面的sic与第一栅氧化层的界面处从而氧化sic生成二氧化硅,得到致密性好的第二栅氧化层,从而使得最终形成的栅极氧化层更加致密一些,从而有效防止漏电及提高栅氧可靠性。

26.而换一种思路,当先使用热氧化法再使用低压化学气相沉积法时:先热氧化法生成的sio2层将非常致密,导致氧空位、碳空位、碳间隙原子及团簇等缺陷产生,随后低压化学气相沉积法产生的sio2将不能直接与热氧化法产生的sio2层融合,有可能出现分层,不能起到两种方法互补的作用,因此不能采用这种方式。

27.基于同一发明构思,参见图2,本发明实施例还提供一种mos电容器的制作方法,包括以下步骤:步骤s100,提供碳化硅外延;

步骤s200,利用低压化学气相沉积法在所述碳化硅外延表面形成第一栅氧化层,再利用热氧化法透过第一栅氧化层在所述碳化硅外延表面形成第二栅氧化层,从而得到完整的栅极氧化层;其中,所述栅极氧化层包括位于所述碳化硅外延表面的第二栅氧化层和位于所述第二栅氧化层表面的第一栅氧化层,所述第一栅氧化层的厚度为所述栅极氧化层厚度的1/6—1/5;步骤s300,对所述栅极氧化层进行钝化,再基于后续工艺制备得到mos电容器。

28.对所述栅极氧化层进行钝化的步骤具体包括:采用no或者n2o 退火对所述栅极氧化层进行钝化。

29.利用热氧化法在所述碳化硅外延表面形成第二栅氧化层的步骤具体包括:利用热氧化法使得o2透过第一栅氧化层到达碳化硅外延与第一栅氧化层的界面处,从而氧化所述碳化硅外延表面的碳化硅生成二氧化硅,得到第二栅氧化层。

30.进一步地,所述第一栅氧化层的厚度范围为10-15nm,所述栅极氧化层的厚度范围为55-70nm。

31.具体地,本实施例可以采用正硅酸乙酯低压化学气相沉积法在n型碳化硅外延表面生成10-15nm左右厚度的第一栅氧化层;利用高温热氧化法制备45-55nm厚度的第二栅氧化层;得到由第一栅氧化层和第二栅氧化层组成的栅极氧化层,通过no或n2o退火钝化栅极氧化层,再基于后续工艺制作mos电容;通过测试基于本方法得到的mos电容器电子辐照前后的平带电压、界面态密度以及栅氧可靠性,并且与根据现有技术制备的mos电容比较,可以得知本方法得到的mos电容器同时保证了可靠性更好、致密性更好等的优点。

32.基于同一发明构思,本发明实施例还提供一种mos电容器,所述mos电容器是采用所述mos电容器的制作方法形成的。

33.基于同一发明构思,本发明实施例还提供一种半导体器件,包括根据所述碳化硅栅极氧化层的制作方法形成的栅极氧化层。

34.其中,所述半导体器件包括mos电容器、mos晶体管等。

35.本发明有效联合了高温热氧化法与低压化学气相沉积法两种方法制备栅氧各自的优点,首先通过低压化学气相沉积法生成的疏松氧化层有利于氧分子或氧原子迁移到所述碳化硅外延表面的sic与第一栅氧化层的sio2界面处,从而降低碳空位等缺陷;再通过高温热氧化法生成的第二栅氧化层足够致密,可以有效防止漏电及较高的栅氧可靠性。

36.本发明虽然己以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1