一种应用芯片堆叠结构的激光雷达模组及其芯片堆叠方法与流程

1.本发明涉及芯片封装技术领域,具体为一种应用芯片堆叠结构的激光雷达模组及其芯片堆叠方法。

背景技术:

2.dtof(直接飞行时间)模组,是直接测量飞行时间的模组,广泛应用于激光测距技术和3d成像技术中,进而在智能移动终端、机器人、航空航天和汽车领域得到广泛应用。

3.dtof模组的核心组件包括vcsel(垂直腔面发射激光器)、spad(单光子雪崩二极管)和tdc(时间数字转换器);其中spad是一种具有单光子探测能力的光电探测雪崩二极管,只要有微弱的光信号就能产生电流。dtof模组的具体工作原理为vcsel向场景中发射脉冲波光信号,spad接收从目标物体反射回来的脉冲波光信号,tdc记录每次接收到的脉冲波光信号的飞行时间,也就是发射脉冲波光信号和接收脉冲波光信号之间的时间间隔;dtof会在单帧测量时间内发射和接收n次脉冲波光信号,然后对记录的n次飞行时间做直方图统计,获取出现频率最高的飞行时间,用以计算待测物体的深度。

4.现有技术中dtof模组的vcsel芯片和spad芯片是分开摆放,进行单独封装,导致形成的dtof模组产品结构尺寸偏大。其主要表现在于芯片设计spad芯片与vcsel芯片没有专门设计应用连接,无法通过flip chip倒装工艺进行线路的引脚进行连接导通。

技术实现要素:

5.本发明的目的之一在于提供一种应用芯片堆叠结构的激光雷达模组,能减小dtof模组产品结构尺寸。

6.本发明提供的基础方案一:一种应用芯片堆叠结构的激光雷达模组,包括:vcsel芯片与spad芯片;

7.所述vcsel芯片倒装贴合在spad芯片上,vcsel芯片和spad芯片分别在其贴合面上设置有若干连接引脚,且vcsel芯片的连接引脚与spad芯片的连接引脚对应连接。

8.进一步,所述vcsel芯片通过flip chip(倒装芯片技术)倒装形式贴合在spad芯片上。

9.进一步,所述vcsel芯片在其与spad芯片的贴合面上设置有凹槽,vcsel芯片的若干连接引脚设置在凹槽底面,凹槽外的贴合面上也设置有若干连接引脚。

10.进一步,所述vcsel芯片的连接引脚与spad芯片的连接引脚通过植金球形式进行对应连接。

11.进一步,所述spad芯片与vcsel芯片贴合面上设置有引出电路,所述引出电路一端与spad芯片的连接引脚连接,另一端设置有连接点,用于与外部电路连接。

12.进一步,所述spad芯片与vcsel芯片贴合面上还设置有mark(标记)点,用于机器识别时进行对准定位。

13.本方案的原理及优点在于:本方案中dtof模组的vcsel芯片与spad芯片采用堆叠

结构,vcsel芯片通过flip chip倒装形式贴合在spad芯片上,且vcsel芯片和spad芯片分别在其贴合面上均设置有若干连接引脚,vcsel芯片的连接引脚与spad芯片的连接引脚通过植金球形式对应连接,使vcsel芯片与spad芯片通过pin to pin方式,采用flip chip封装工艺方式进行连接结合,形成一个集成一体化的dtof模组的芯片,vcsel芯片和spad芯片无需分开摆放,进行单独封装,极大的减小了dtof模组产品结构尺寸,本方案spad芯片与vcsel芯片设计有应用链接,从而可以通过flip chip倒装工艺进行线路的引脚进行链接导通。

14.spad芯片的若干连接引脚设置在其与vcsel芯片的贴合面上,vcsel芯片在其与spad芯片的贴合面上设置有凹槽,vcsel芯片的若干连接引脚设置在凹槽底面,凹槽外的也贴合面上设置有若干连接引脚,从而vcsel芯片倒装贴合在spad芯片上,其连接引脚与spad芯片的连接引脚相对接触,由于凹槽的设置可以减小vcsel芯片和spad芯片之间的间隙,使贴合更紧密,进一步减小dtof模组产品结构尺寸。

15.此外,spad芯片与vcsel芯片贴合面上还设置有mark点和引出电路,其中mark点用于机器识别时进行对准定位,以便于加工时,机器对每个芯片进行准确定位,进而保障加工的准确性;引出电路一端与spad芯片的连接引脚连接,另一端设置有连接点,用于与外部电路连接,以便于形成一体化的dtof模组与其他模组连接。

16.本发明的目的之二在于提供一种应用芯片堆叠结构的芯片堆叠方法,以减少dtof模组产品结构尺寸。

17.本发明提供基础方案二:一种应用芯片堆叠结构的芯片堆叠方法,包括如下内容:

18.s2、在spad芯片的连接引脚上进行金球值球;

19.s3、vcsel芯片倒装贴合在spad芯片上,贴合面上vcsel芯片的连接引脚与金球进行焊接导通。

20.进一步,还包括:s1、将spad芯片设置于基板上方。

21.进一步,还包括:s4、在spad芯片上进行底部点胶。

22.进一步,还包括:s5、对spad芯片和vcsel芯片进行一体集成dtof模组封装。

23.本方案的原理及优点在于:本方案用于加工dtof模组,具体为用于加工上述应用芯片堆叠结构的激光雷达模组,其中将vcsel芯片与spad芯片加工为堆叠结构,vcsel芯片倒装贴合在spad芯片上,且vcsel芯片和spad芯片分别在其贴合面上均设置有若干连接引脚,vcsel芯片的连接引脚与spad芯片的连接引脚通过植金球形式对应焊接连接,使vcsel芯片与spad芯片通过pin to pin方式,对spad芯片和vcsel芯片进行一体集成dtof模组封装,形成一个集成一体化的dtof模组的芯片,vcsel芯片和spad芯片无需分开摆放,进行单独封装,极大的减小了dtof模组产品结构尺寸。

附图说明

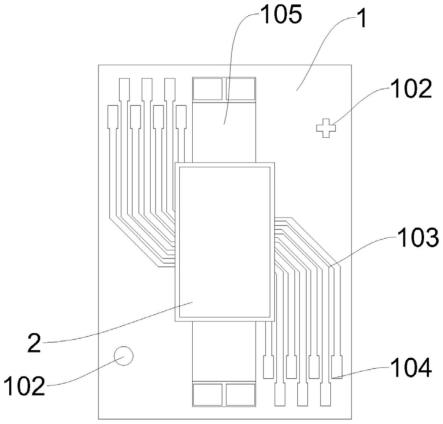

24.图1为本发明一种应用芯片堆叠结构的激光雷达模组实施例的结构示意图;

25.图2为本发明一种应用芯片堆叠结构的激光雷达模组实施例的侧视图;

26.图3为本发明一种应用芯片堆叠结构的激光雷达模组实施例中spad芯片的正视图;

27.图4为本发明一种应用芯片堆叠结构的激光雷达模组实施例中spad芯片的结构示

意图;

28.图5为本发明一种应用芯片堆叠结构的激光雷达模组实施例中vcsel芯片的正视图;

29.图6为本发明一种应用芯片堆叠结构的激光雷达模组实施例中vcsel芯片的结构示意图。

具体实施方式

30.下面通过具体实施方式进一步详细说明:

31.说明书附图中的附图标记包括:spad芯片1、vcsel芯片2、第一连接引脚101、mark点102、引出电路103、连接点104、逻辑区域105、凹槽201、第二连接引脚202。

32.在本技术的描述中,除非另有明确的规定和限定,术语“第一”、“第二”仅用于描述的目的,而不能理解为指示或暗示相对重要性;除非另有规定或说明,术语“多个”是指两个或两个以上;术语“连接”、“固定”等均应做广义理解,例如,“连接”可以是固定连接,也可以是可拆卸连接,或一体地连接,或电连接;可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

33.本说明书的描述中,需要理解的是,本技术实施例所描述的“上”、“下”、“左”、“右”等方位词是以附图所示的角度来进行描述的,不应理解为对本技术实施例的限定。此外,在上下文中,还需要理解的是,当提到一个元件连接在另一个元件“上”、“下”、“左”或“右”时,其不仅能够直接连接在另一个元件“上”、“下”、“左”或“右”,也可以通过中间元件间接连接在另一个元件“上”、“下”、“左”或“右”。

34.实施例一

35.实施例基本如附图1所示:一种应用芯片堆叠结构的激光雷达模组,包括:spad芯片1与vcsel芯片2;

36.vcsel芯片2倒装贴合在spad芯片1上,如图2所示,vcsel芯片2和spad芯片1分别在其贴合面上均设置有若干连接引脚,且vcsel芯片2的连接引脚与spad芯片1的连接引脚对应连接。

37.具体地,vcsel芯片2通过flip chip倒装形式贴合在spad芯片1上,如图3和图4所示,spad芯片1的若干连接引脚设置在其与vcsel芯片2的贴合面上,作为第一连接引脚101,本实施例中采用焊接方式设置连接引脚;如图5和图6所示,vcsel芯片2在其与spad芯片1的贴合面上设置有凹槽201,vcsel芯片2的若干连接引脚设置在凹槽201底面,凹槽201外的也贴合面上设置有若干连接引脚,且凹槽201内的连接引脚和凹槽201外的连接引脚顶面均处于同一平面,作为第二连接引脚202,保障贴合的稳定性,并且凹槽201的设置可以减小vcsel芯片2和spad芯片1之间的间隙,使贴合更紧密,进一步减小dtof模组产品结构尺寸;vcsel芯片2的连接引脚与spad芯片1的连接引脚通过植金球形式进行对应焊接连接,其中焊接采用超声波焊接。

38.此外,spad芯片1与vcsel芯片2贴合面上设置有mark点102和引出电路103,其中mark点102,用于机器识别时进行对准定位;引出电路103一端与spad芯片1的连接引脚连接,另一端设置有连接点104,用于与外部电路连接。spad芯片1与vcsel芯片2贴合面上还设

置有逻辑区域105。

39.本方案中dtof模组的vcsel芯片2与spad芯片1采用堆叠结构,vcsel芯片2通过flip chip倒装形式贴合在spad芯片1上,且vcsel芯片2和spad芯片1分别在其贴合面上均设置有若干连接引脚,vcsel芯片2的连接引脚与spad芯片1的连接引脚通过植金球形式对应连接,使vcsel芯片2与spad芯片1通过pin to pin方式,采用flip chip封装工艺方式进行连接结合,形成一个集成一体化的dtof模组的芯片,vcsel芯片2和spad芯片1无需分开摆放,进行单独封装,极大的减小了dtof模组产品结构尺寸。

40.实施例二

41.实施例基本如附图1所示:一种应用芯片堆叠结构的芯片堆叠方法,用于上述应用芯片堆叠结构的激光雷达模组的加工,包括如下内容:

42.s1、将spad芯片1设置于基板上方;具体地,spad芯片1水平放置在基板上,spad芯片1的连接点104和基板的连接点通过导线进行连接;

43.s2、在spad芯片1的连接引脚上进行金球值球,即将金球焊接在spad芯片1的连接引脚顶面;

44.s3、vcsel芯片2倒装贴合在spad芯片1上,贴合面上vcsel芯片2的连接引脚与金球进行焊接导通;其中焊接采用超声波焊接;

45.s4、在spad芯片1上进行底部点胶,进行spad芯片1和vcsel芯片2封装加固;

46.s5、对spad芯片1和vcsel芯片2进行一体集成dtof模组封装。

47.本方案能加工出一体化话的dtof模组,其中将vcsel芯片2与spad芯片1加工为堆叠结构,vcsel芯片2倒装贴合在spad芯片1上,且vcsel芯片2和spad芯片1分别在其贴合面上均设置有若干连接引脚,vcsel芯片2的连接引脚与spad芯片1的连接引脚通过植金球形式对应焊接连接,使vcsel芯片2与spad芯片1通过pin to pin方式,对spad芯片1和vcsel芯片2进行一体集成dtof模组封装,形成一个集成一体化的dtof模组的芯片,vcsel芯片2和spad芯片1无需分开摆放,进行单独封装,极大的减小了dtof模组产品结构尺寸。

48.以上所述的仅是本发明的实施例,方案中公知的具体结构及特性等常识在此未作过多描述,所属领域普通技术人员知晓申请日或者优先权日之前发明所属技术领域所有的普通技术知识,能够获知该领域中所有的现有技术,并且具有应用该日期之前常规实验手段的能力,所属领域普通技术人员可以在本技术给出的启示下,结合自身能力完善并实施本方案,一些典型的公知结构或者公知方法不应当成为所属领域普通技术人员实施本技术的障碍。应当指出,对于本领域的技术人员来说,在不脱离本发明结构的前提下,还可以作出若干变形和改进,这些也应该视为本发明的保护范围,这些都不会影响本发明实施的效果和专利的实用性。本技术要求的保护范围应当以其权利要求的内容为准,说明书中的具体实施方式等记载可以用于解释权利要求的内容。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1