紫外发光二极管及其制造方法与流程

1.本公开涉及半导体技术领域,特别涉及一种紫外发光二极管及其制造方法。

背景技术:

2.基于(al)gan材料的紫外发光二极管在空气净化、杀菌消毒、紫外光疗、生化检测、保密通信等领域的应用非常广泛,是氮化物半导体研究领域的一个重要研究内容。

3.然而,(al)gan基的duv led具有独特的光学偏振特性,首先是随着a1组份不断上升,duv led发光波长变短,光的偏振态从横向电极化模式(te)向横向磁极化模式(tm)转化。而因为algan的折射率与空气的折射率相差巨大,tm偏振光又主要沿横向传播,因此界面入射角较大,在不同材料界面处发生的全反射作用会导致(a1)gan基duv led的光提取效率(lee)很低,严重降低了紫外发光二极管的出光效率。

技术实现要素:

4.本公开实施例提供了一种紫外发光二极管及其制造方法,通过形成第一凹槽和第二凹槽,改变紫外led的内部结构,可以打破紫外led内部的全反射效应,提高紫外led的光提取效率。所述技术方案如下:

5.第一方面,提供了一种紫外发光二极管,所述紫外发光二极管包括衬底、外延层、n型电极和p型电极,所述外延层包括依次层叠在所述衬底上的缓冲层、n型层、多量子阱层和p型层;

6.所述紫外发光二极管具有第一凹槽和第二凹槽,所述第一凹槽从所述p型层开设至所述n型层,所述第一凹槽的槽底为所述n型层,所述n型电极设置在所述第一凹槽槽底的所述n型层上,所述p型电极设置在所述第一凹槽外的所述p型层上;所述第二凹槽从所述第一凹槽槽底的所述n型层开设至所述缓冲层或所述衬底,所述第二凹槽的槽底为所述缓冲层或所述衬底。

7.可选的,所述紫外发光二极管还包括第一接触层和第二接触层;

8.所述p型层的除所述p型电极设置区域外的其他区域上、所述第一凹槽的侧壁上、以及所述第一凹槽槽底除所述n型电极设置区域外的其他区域上均铺设有所述第一接触层,所述第一接触层为钝化层或增透膜层;

9.所述第二凹槽的侧壁和槽底均铺设有所述第二接触层,所述第二接触层为增透膜层或反射层,或者,所述第二接触层的材料与所述n型电极或所述n型层的材料相同。

10.可选的,所述紫外发光二极管还包括反射层,所述反射层覆盖所述n型电极、所述p型电极、所述第一接触层和所述第二接触层。

11.可选的,所述紫外发光二极管还包括n型焊盘、p型焊盘和p型焊盘连接层;

12.其中,所述p型焊盘连接层设置在所述反射层的远离所述衬底的一面上,且所述p型焊盘连接层位于所述p型电极的正上方,所述p型焊盘位于所述p型焊盘连接层的远离所述衬底的一面上;

13.所述n型焊盘设置在所述反射层的远离所述衬底的一面上,且所述n型焊盘位于所述n型电极的正上方。

14.可选的,所述紫外发光二极管还包括钝化层,所述反射层上除所述p型焊盘连接层和所述n型焊盘的设置区域外的其它区域上均铺设有所述钝化层。

15.第二方面,提供了一种紫外发光二极管的制造方法,所述制造方法包括:

16.在衬底上生长外延层得到外延片,所述外延层包括依次生长在衬底上的缓冲层、n型层、多量子阱层和p型层;

17.对所述外延层进行多次刻蚀,以在所述外延层上形成第一凹槽和第二凹槽,所述第一凹槽从所述p型层开设至所述n型层,所述第一凹槽的槽底为所述n型层;所述第二凹槽从所述第一凹槽槽底的所述n型层开设至所述缓冲层或所述衬底,所述第二凹槽的槽底为所述缓冲层或所述衬底;

18.在所述第一凹槽槽底的所述n型层上形成n型电极;

19.在所述第一凹槽外的所述p型层上形成p型电极。

20.可选的,所述制造方法还包括:

21.在所述p型层的除所述p型电极设置区域外的其他区域上、所述第一凹槽的侧壁上、以及所述第一凹槽槽底除所述n型电极设置区域外的其他区域上形成第一接触层,所述第一接触层为钝化层或增透膜层;

22.在所述第二凹槽的侧壁和槽底形成第二接触层,所述第二接触层为增透膜层或反射层,或者,所述第二接触层的材料与所述n型电极或所述n型层的材料相同。

23.可选的,所述制造方法还包括:

24.在所述n型电极、所述p型电极、所述第一接触层和所述第二接触层上形成反射层。

25.可选的,所述制造方法还包括:

26.在所述反射层的远离所述衬底的一面上形成p型焊盘连接层,所述p型焊盘连接层位于所述p型电极的正上方;

27.在所述p型焊盘连接层的远离所述衬底的一面上形成p型焊盘;

28.在所述反射层的远离所述衬底的一面上形成n型焊盘,所述n型焊盘位于所述n型电极的正上方。

29.可选的,所述制造方法还包括:

30.在所述反射层上除p型焊盘连接层和n型焊盘的设置区域外的其它区域上形成钝化层。

31.本公开实施例提供的技术方案带来的有益效果是:

32.通过在紫外led内形成第一凹槽和第二凹槽,以改变led的内部结构。其中,第一凹槽从p型层开设至n型层,第二凹槽从第一凹槽槽底的n型层开设至缓冲层或衬底。通过设置第二凹槽可以减少多量子阱层产生的光子在n型层到缓冲层或衬底内产生的全反射效应。多量子阱层产生的光子不仅可以从衬底方向出光,还可以从第一凹槽和第二凹槽的侧壁出光,以改变光子的传播方向,使得光子在led内部形成多次反射,从而可以减少光子在器件内的全反射效应,提高芯片的光提取效率。

附图说明

33.为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

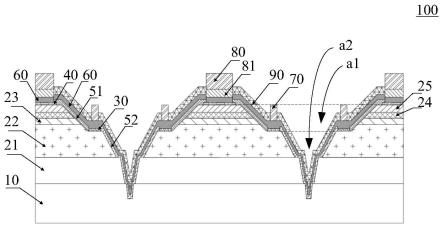

34.图1是本公开实施例提供的一种紫外发光二极管的截面示意图;

35.图2是本公开实施例提供的一种紫外发光二极管的制造方法流程图;

36.图3是本发明实施例提供的一种外延片刻蚀截面示意图。

具体实施方式

37.为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

38.图1是本公开实施例提供的一种紫外发光二极管的截面示意图,如图1所示,该紫外发光二极管100包括衬底10、外延层、n型电极30和p型电极40。外延层包括依次层叠在衬底10上的缓冲层21、n型层22、多量子阱层23和p型层25。

39.紫外发光二极管100具有第一凹槽a1和第二凹槽a2。第一凹槽a1从p型层25开设至n型层22,第一凹槽a1的槽底为n型层22。n型电极30设置在第一凹槽a1槽底的n型层22上。p型电极40设置在第一凹槽a1外的p型层25上。第二凹槽a2从第一凹槽a1槽底的n型层22开设至缓冲层21或衬底10。第二凹槽a2的槽底为缓冲层21或衬底10

40.本发明实施例通过在紫外led内形成第一凹槽和第二凹槽,以改变led的内部结构。其中,第一凹槽从p型层开设至n型层,第二凹槽从第一凹槽槽底的n型层开设至缓冲层或衬底。通过设置第二凹槽可以减少多量子阱层产生的光子在n型层到缓冲层或衬底内产生的全反射效应。多量子阱层产生的光子不仅可以从衬底方向出光,还可以从第一凹槽和第二凹槽的侧壁出光,以改变光子的传播方向,使得光子在led内部形成多次反射,从而可以减少光子在器件内的全反射效应,提高芯片的光提取效率。

41.在本实施例的一种实现方式中,第二凹槽a2的底面宽度小于第一凹槽a1的底面宽度。且从外延层的p型层25至衬底10方向,第二凹槽a2的宽度逐层减小。

42.可选的,第一凹槽a1可以通过一次刻蚀成型。第一凹槽a1的刻蚀深度为h1,h2<h1≤h3,h2为n型层上方的外延层的厚度,h3为缓冲层上方的外延层厚度,h3-h2为n型层的厚度。考虑到后续的工艺与钝化层材料的覆盖性,第一凹槽a1的刻蚀角度在5

°

~75

°

。其最优的刻蚀角度可根据量子阱层的全反射角度进行计算,本实施例中,较优的角度在35

°

。其中刻蚀角度不同,形成的第一凹槽a1的侧壁的倾斜角度即不同。

43.第二凹槽a2可以通过多次刻蚀得到。例如,通过对n型层22进行一次刻蚀,刻蚀深度为h4,0um<h4≤h5,h5为剩余n型层的厚度,刻蚀角度在5

°

~80

°

;对缓冲层21进行二次刻蚀,刻蚀深度为h6在0<h6≤h7,h7为缓冲层厚度,刻蚀角度在10

°

~85

°

;得到槽底为缓冲层21的第二凹槽a2。此时第二凹槽a2通过两次刻蚀得到。

44.或者,通过对n型层22进行一次刻蚀,刻蚀深度为h4,0um<h4≤h5,h5为剩余n型层的厚度,刻蚀角度在5

°

~80

°

;对缓冲层21进行二次刻蚀,刻蚀深度为h6在0<h6≤h7,h7为缓冲层厚度,刻蚀角度在10

°

~85

°

;对衬底10进行三次刻蚀,h8在0<h8≤h9,h9为衬底厚

度,刻蚀角度在5

°

~85

°

,得到槽底为衬底10的第二凹槽a2。此时第二凹槽a2通过三次刻蚀得到。

45.需要说明的是,刻蚀形成的上述第一凹槽a1和第二凹槽a2的横截面形状可以为圆柱形、正梯形、倒梯形等,刻蚀侧壁可进行粗化,刻蚀的台面可进行粗化、光子晶体、图形化等设计,本发明实施例对此不做限定。

46.在本实施例中,衬底1可以为蓝宝石衬底。缓冲层21可以为a1n层,生长缓冲层2主要是为了缓解蓝宝石衬底与algan材料的晶格失配和热失配。但是该层的厚度不宜过厚,因为该层晶体质量较差,如果生长过厚,则会影响后续外延结构的生长并且会吸光,影响外量子效率。n型层22可以为掺si的algan层。多量子阱层23可以包括多个周期交替生长的量子阱层和量子垒层其中量子阱层为al

x

ga

1-x

n层,0<x<1,量子垒层为alyga

1-y

n层,0<y<1。量子阱层和量子垒层中al组分含量不同,即x和y的取值不同,以提供不同的禁带宽度。根据不同的紫外波长,x和y可以选取不同的取值组合。p型层25可以为掺mg的algan层。n型层22提供的电子和p型层25提供的空穴可以在多量子阱层23中进行辐射复合发光。n型电极30的材料包括但不限于cr、al、ti、pt、au等组合金属或者叠层金属、外延二次生长的高电导性n型半导体等。例如,当n型电极30的材料为组合金属结构时,厚度为200~500nm。p型电极40的材料包括但不限于niau、氧化铟锡、rh等。例如当p型电极40的材料为氧化铟锡时,厚度为10~70nm。

47.可选地,如图1所示,紫外发光二极管还包括设置在多量子阱层23和p型层25之间的电子阻挡层24,电子阻挡层24可以为掺mg的a1gan层。通过设置电子阻挡层可以有效阻挡电子从多量子阱层23逃逸到p型层25,从而可以提高led的内量子效率。

48.可选的,紫外发光二极管100还包括第一接触层51和第二接触层52。

49.p型层25的除p型电极40设置区域外的其他区域上、第一凹槽a1的侧壁上、以及第一凹槽a1槽底除n型电极30设置区域外的其他区域上均铺设有第一接触层51,第一接触层51为钝化层或增透膜层。

50.第二凹槽a2的侧壁和槽底均铺设有第二接触层52,第二接触层52为增透膜层或反射层,或者,第二接触层52的材料与n型电极或n型层的材料相同。

51.其中,当第一接触层51为钝化层时,可以起到绝缘和保护的作用。增透膜是一种表面光学镀层,它通过减少反射光来增加光在表面的透过率。当第一接触层51和第二接触层52均为增透膜层时,可以进一步减少紫外led中光的全反射,从而光的提取效率。

52.当第二接触层52为反射层时,可以将原本被损耗的光子尽可能反射到衬底背面,进一步提高芯片的光提取效率。当第二接触层的材料与n型电极或n型层的材料相同时,可以充当电流扩展层或者二次外延的接触电极,降低器件电压的同时,减少工艺步骤,降低器件成本提高良率等。在本实施例中,第二接触层的材料可以为例如cr、ti、al、pt、au等单层或者叠层金属材料。

53.可选的,紫外发光二极管100还包括反射层60,反射层60覆盖n型电极30、p型电极40、第一接触层51和第二接触层52。

54.在本实施例中,反射层60可以为al、rh等单层结构的反射层,或者多层金属构成的odr(omni-directionasrefiector,全角反射镜)或者dbr(distributed bragg reflection,分布式布拉格反射镜)结构。

55.可选地,反射层可以为cr/al基反射结构,即掺cr/al的反射层。这样反射层不仅可以起到反射作用,同时也是对n型电极与p型电极进行加厚,使其具有更均匀的电流扩展。

56.可选的,紫外发光二极管还包括n型焊盘70、p型焊盘80和p型焊盘连接层81。

57.其中,p型焊盘连接层81设置在反射层60的远离衬底10的一面上,且p型焊盘连接层81位于p型电极40的正上方,p型焊盘80位于p型焊盘连接层81的远离衬底10的一面上。

58.n型焊盘70设置在反射层60的远离衬底10的一面上,且n型焊盘70位于n型电极30的正上方。

59.在本实施例中,p型焊盘连接层81可以为cr/al/ti/pt/au层,厚度例如可以为300nm。p型焊盘连接层81不仅可以起到连接p型电极的作用,还可以起到加厚p型电极的作用。n型焊盘70和p型焊盘80的材料可以为ausn,厚度可以为1.9um。

60.可选的,紫外发光二极管还包括钝化层90,反射层60上除p型焊盘连接层81和n型焊盘70的设置区域外的其它区域上均铺设有钝化层90。钝化层90可以起到绝缘和保护作用。示例性的,钝化层90的厚度可以为1um。

61.需要说的是本发明实施例提供的紫外发光二极管可以为uva长波紫外发光二极管,也可以为uvb中波紫外发光二极管或者uvc短波紫外发光二极管,本发明对此不作限定。

62.本发明实施例还提供了一种紫外发光二极管的制造方法,用于制造如图1所示的紫外发光二极管。图2是本公开实施例提供的一种紫外发光二极管的制造方法流程图,如图2所示,该制造方法包括:

63.步骤201、在衬底上生长外延层得到外延片。

64.其中,衬底可以为蓝宝石衬底。外延层包括依次生长在衬底上的缓冲层、n型层、多量子阱层、电子阻挡层和p型层。外延层各层的具体可以参见如图1的相关描述,在此不再赘述。

65.在本实施例中,可以采用veeco k465i or c4 or rb mocvd(metal organic chemical vapor deposition,金属有机化合物化学气相沉淀)设备实现外延层的生长。采用高纯h2(氢气)或高纯n2(氮气)或高纯h2和高纯n2的混合气体作为载气,高纯nh3作为n源,三甲基镓(tmga)及三乙基镓(tega)作为镓源,三甲基铟(tmin)作为铟源,硅烷(sih4)作为n型掺杂剂,三甲基铝(tmal)作为铝源,二茂镁(cp2mg)作为p型掺杂剂。

66.在执行完步骤s201之后,执行步骤s202之前,该制造方法还可以包括:

67.将外延片使用丙酮和异丙醇分别超声清洗5min,去除表面的有机物;再用去离子水冲洗5min,甩干机甩干。

68.步骤202、对外延层进行多次刻蚀,以在外延层上形成第一凹槽和第二凹槽。

69.其中,第一凹槽从p型层开设至n型层,第一凹槽的槽底为n型层;第二凹槽从第一凹槽槽底的n型层开设至缓冲层或衬底,第二凹槽的槽底为缓冲层或衬底。

70.在本实施例中,第一凹槽a1可以通过一次刻蚀成型。具体可以通过正性光刻胶作为掩膜,使用感应耦合等离子体(icp)对外延片进行mesa台面刻蚀,刻蚀比为3∶1,刻蚀深度为450~850nm,较优的刻蚀角度为35

°

。将刻蚀后的外延片放在85℃去胶液、丙酮和异丙醇各超声10min、5min和5min,去离子水冲洗5min,去除表面正性光刻胶,以形成第一凹槽。

71.在本实施例中,可以通过多次刻蚀得到第二凹槽。例如,通过对n型层进行一次刻蚀,刻蚀深度为h4,0um<h4≤h5,h5为剩余n型层的厚度,刻蚀角度在5

°

~80

°

;对缓冲层进

行二次刻蚀,刻蚀深度为h6在0<h6≤h7,h7为缓冲层厚度,刻蚀角度在10

°

~85

°

;得到槽底为缓冲层的第二凹槽。此时第二凹槽通过两次刻蚀得到。

72.或者,通过对n型层进行一次刻蚀,刻蚀深度为h4,0um<h4≤h5,h5为剩余n型层的厚度,刻蚀角度在5

°

~80

°

(优选为45

°

);对缓冲层进行二次刻蚀,刻蚀深度为h6在0<h6≤h7,h7为缓冲层厚度,刻蚀角度在10

°

~85

°

(优选为55

°

);对衬底进行三次刻蚀,h8在0<h8≤h9,h9为衬底厚度,刻蚀角度在5

°

~85

°

,得到槽底为衬底的第二凹槽。

73.其中,在刻蚀n型层和缓冲层时,可以采用正性光刻胶作为掩膜,在bcl3和cl2的混合气氛下,使用感应耦合等离子体(icp)进行刻蚀。通过调节掩膜版与样品的距离,可以使得光刻胶在台面具有一定的角度,光刻胶的胶厚可以为8~10um。由于衬底相对于外延层更难刻蚀,因此,可以通过二氧化硅与光刻胶共同掩膜的方法,采用干法刻蚀与湿法刻蚀相结合的方法对衬底进行刻蚀,刻蚀衬底时,较优的刻蚀角度为36

°

,刻蚀深度为20~30um。

74.图3是本发明实施例提供的一种外延片刻蚀截面示意图,如图3所示,此时外延片上形成有第一凹槽a1和第二凹槽a2。

75.可选地,在执行完步骤s202之后,执行步骤s203之前,该方法还可以包括:

76.对外延片进行划片道刻蚀。

77.示例性的,可以采用icp刻蚀法对外延片进行划片道刻蚀,刻蚀深度为4~5um。通过对外延片进行划片道刻蚀,以便于后续对外延片进行划片。

78.步骤203、在第一凹槽槽底的n型层上形成n型电极。

79.其中,n型电极的材料包括但不限于cr、al、ti、pt、au等组合金属或者叠层金属、外延二次生长的高电导性n型半导体等。例如,当n型电极的材料为组合金属结构时,厚度为200~500nm。

80.在本实施例中,可以通过蒸镀、退火、刻蚀的方法形成n型电极,此为常规技术,在此不再赘述。其中,n型电极的退火条件可以为氮气氛围、800~900℃、快速退火1min。

81.步骤204、在第一凹槽外的p型层上形成p型电极。

82.其中,p型电极的材料包括但不限于niau、氧化铟锡、rh等。例如当p型电极的材料为氧化铟锡时,厚度为10~70nm。

83.在本实施例中,可以通过蒸镀、退火、刻蚀的方法形成p型电极,此为常规技术,在此不再赘述。其中,p型电极的退火条件可以为氧气氛围、500℃、快速退火5min。

84.可选地,该制造方法还可以包括:

85.在p型层的除p型电极设置区域外的其他区域上、第一凹槽的侧壁上、以及第一凹槽槽底除n型电极设置区域外的其他区域上形成第一接触层,第一接触层为钝化层或增透膜层。

86.在第二凹槽的侧壁和槽底形成第二接触层,第二接触层为增透膜层或反射层,或者,第二接触层的材料与n型电极或n型层的材料相同。

87.示例性的,当第一接触层为钝化层时,可以采用pecvd(plasma enhanced chemical vapor deposition,等离子体增强化学的气相沉积)法沉积钝化层。当第一接触层和第二接触层为增透膜层时,可以采用pecvd法沉积一层厚度为四分之一波长奇数倍的二氧化硅层,得到增透膜层。当第二接触层为反射层时,可以采用电子束蒸发沉积反射层,或者采用pecvd设备或者电子枪真空蒸镀系统(e-gun)沉积高低折射率差的多层钝化层材

料,得到反射层。当第二接触层的材料与n型电极或n型层的材料相同时,可以采用电子束蒸发或者磁控溅射等方法制备得到。

88.可选地,该制造方法还可以包括:

89.在n型电极、p型电极、第一接触层和第二接触层上形成反射层。

90.在本实施例中,可以使用负性光刻胶作为掩膜,采用电子束蒸发蒸镀的方法制备反射层,然后使用剥离液将负性光刻胶进行剥离。

91.可选地,该制造方法还可以包括:

92.在反射层的远离衬底的一面上形成p型焊盘连接层,p型焊盘连接层位于p型电极的正上方;

93.在p型焊盘连接层的远离衬底的一面上形成p型焊盘;

94.在反射层的远离衬底的一面上形成n型焊盘,n型焊盘位于n型电极的正上方。

95.在本实施例中,可以采用蒸镀的方法制备p型焊盘连接层、p型焊盘和n型焊盘。具体的,在制备p型焊盘连接层n型焊盘之前,可以先采用pecvd法在反射层的远离衬底的一面上沉积一层二氧化硅保护层,以对n区进行保护。然后将p型层正上方的二氧化硅保护层进行腐蚀在腐蚀区域蒸镀金属cr/al/ti/pt/au以形成p型焊盘连接层。最后,可以通过光刻掩膜与icp刻蚀工艺去除剩余的二氧化硅保护层。p型焊盘和n型焊盘的蒸镀方式与p型焊盘连接层类似蒸镀的金属可以为ausn电极。

96.可选地,该制造方法还可以包括:

97.在反射层上除p型焊盘连接层和n型焊盘的设置区域外的其它区域上形成钝化层。

98.在本实施例中,可以采用蒸镀的方法制备钝化层,蒸镀厚度约1um,蒸镀温度约220℃。

99.需要说的是,可以在制备p型焊盘连接层之后,制备p型焊盘和n型焊盘之前,形成上述钝化层。

100.本发明实施例通过在紫外led内形成第一凹槽和第二凹槽,以改变led的内部结构。其中,第一凹槽从p型层开设至n型层,第二凹槽从第一凹槽槽底的n型层开设至缓冲层或衬底。通过设置第二凹槽可以减少多量子阱层产生的光子在n型层到缓冲层或衬底内产生的全反射效应。多量子阱层产生的光子不仅可以从衬底方向出光,还可以从第一凹槽和第二凹槽的侧壁出光,以改变光子的传播方向,使得光子在led内部形成多次反射,从而可以减少光子在器件内的全反射效应,提高芯片的光提取效率。

101.以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1