一种基于石墨烯电极的二维半导体器件阵列构建工艺

本发明属于微电子工艺和器件应用领域,具体涉及一种基于石墨烯电极的二维半导体器件阵列构建工艺。

背景技术:

1、随着器件尺寸的小型化,硅基材料之后的下一代半导体材料研发引发了人们广泛的兴趣。目前的研究显示二硫化钼(mos2)、黑磷等新型二维半导体作为沟道材料在场效应管、光电探测等器件领域上显示了巨大的应用潜力;但值得注意的是,由于二维半导体材料原子级的厚度,使其在金属电极生长中很容易受到损伤或无意掺杂,形成非理想/二维半导体界面,从而限制了器件的性能,这成为了二维半导体材料在微电子器件应用之路上必须要解决的问题。

2、在二维半导体材料电极接触的问题研究上,其中一种思路是采用石墨烯(graphene)作为电极材料,这是因为graphene是一种典型的二维半金属材料,一方面可以通过转移graphene与二维半导体材料接触,形成理想的范德华接触;另一方面实验显示即使是侧面接触,graphene及其相关的垂直异质结(如mos2/graphene)也能与传统工艺制备的金属电极形成理想的欧姆接触,因此可以通过graphene电极将二维半导体材料和金属电极连接在一起。虽然目前已经在实验上证明了上述graphene电极方案的可行新,但是实现的工艺主要是采用机械剥离graphene在光学系统上转移到沟道化的mos2上,只能作为单个器件的展示,无法实现器件在尺寸、位置和数量上的可控,无法适用于实际中不同电路的需求。

3、所以,研究一种与现有微电子光刻工艺兼容,能够在器件尺寸、位置和数量上实现可控,以graphene为电极的二维半导体器件阵列的构建工艺,对于推动二维半导体材料在微电子器件领域中的发展具有重要的意义。

技术实现思路

1、本发明的目的在于:提供一种基于graphene电极的二维半导体器件阵列构建工艺,推进二维半导体材料在微电子领域中的应用。

2、二维半导体器件至少包括工作衬底、金属电极、graphene电极和二维半导体材料沟道四部分,其中graphene电极以二维半导体/graphene垂直异质结的结构呈现。此种结构的器件可以不仅可以在二维半导体材料表面上达到理想的范德华电极接触,而且工艺与现有的微电子工艺兼容,可以实现器件阵列的可控构建。

3、本发明采用的技术方案如下:

4、(1)准备大面积graphene(例如采用化学气相沉积(cvd)法在铜箔生长大面积graphene,具体见实施案例)。

5、(2)准备大面积二维半导体沟道材料(例如采用化学气相沉积(cvd)法在蓝宝石衬底上生长大面积mos2,具体见实施案例)。

6、(3)制备带有金属标记的工作衬底:清洗工作衬底,接着在处理好的工作衬底上旋涂光刻胶,然后采用紫外曝光机光刻、显影,随后用电子束蒸镀金属,最后去胶剥离,即可获得图案化的金属标记,以用于后续制备图案化graphene电极、二维半导体材料和金属电极的校准,其流程示意图如图1所示。

7、(4)制备图案化的graphene电极:将大面积graphene转移到在步骤(3)中制备的带有标记的工作衬底,接着旋涂光刻胶,然后采用紫外曝光光刻、显影,随后反应离子刻蚀,最后去胶,即可得到图案化的graphene沟道,其流程示意图如图2所示。

8、(5)制备图案化的二维半导体材料:将大面积二维半导体材料转移到步骤(4)中制备的带有图案化graphene电极的工作衬底,接着旋涂光刻胶,然后采用紫外曝光光刻、显影,随后反应离子刻蚀,最后去胶,即可得到图案化的二维半导体材料沟道。图案化的二维半导体材料分为两部分,一部分作为器件的沟道,另一部分与graphene电极图案一致(宽度上可以略小一些,以确保在光刻对准误差下二维半导体材料下方均是石墨烯,见图3),覆盖在graphene上方形成垂直的异质结结构,避免了graphene电极在反应离子刻蚀过程中被刻蚀掉,其流程示意图如图3所示。

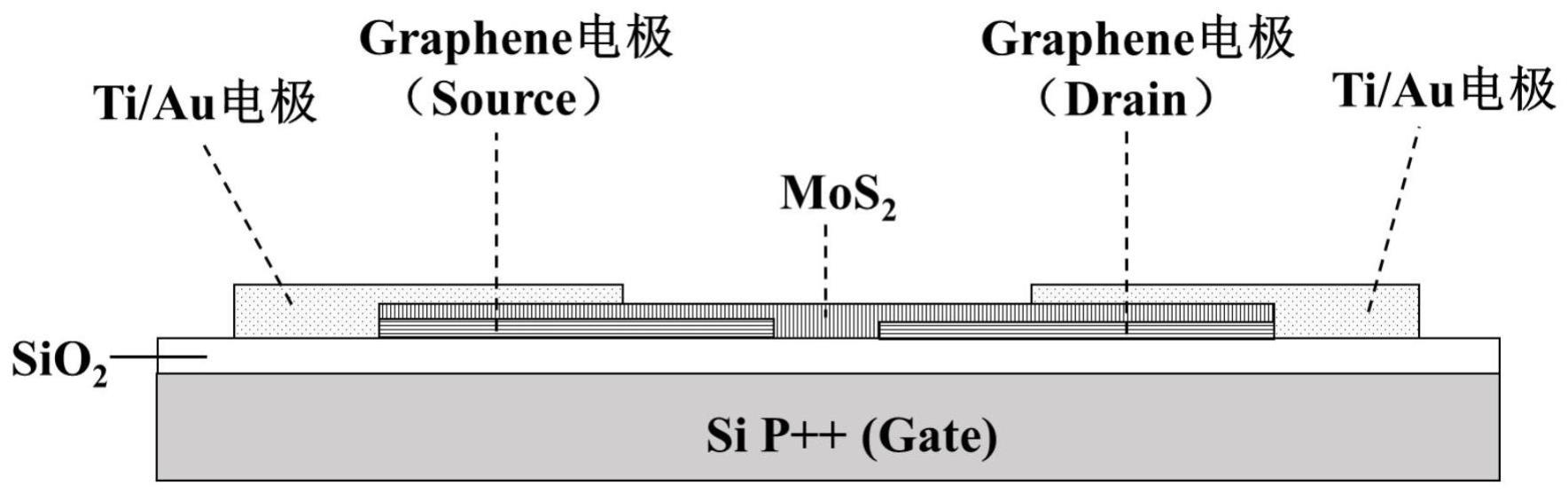

9、(6)制备图案化的金属电极:在步骤(5)制备的带有图案化graphene电极和二维半导体材料的工作衬底上旋涂光刻胶,然后采用紫外曝光光刻、显影,随后用电子束蒸镀金属,最后去胶剥离,即可获得图案化的金属电极,其流程示意图如图4所示,器件整体结构的侧面示意图如图5所示。

10、其中,所述步骤(1)中选用的graphene尺寸只受限于现有紫外曝光设备的要求。

11、其中,所述步骤(2)中选用的二维半导体材料尺寸只受限于现有紫外曝光设备的要求。

12、其中,所述步骤(3)中选用的工作衬底为微电子器件中常用衬底,如二氧化硅/硅(sio2/si)衬底、蓝宝石衬底等。

13、其中,所述步骤(3)-(6)中的紫外曝光、显影、电子束镀膜、反应离子束刻蚀均采用常规工艺。

14、其中,所述步骤(5)种设计的二维半导体/graphene垂直异质结,不仅可以作为电极,在别的物理场下(如光照、栅电压等),也同样可以作为沟道与纯二维半导体材料沟道结合,应用在更多的场景。

15、综上所述,由于采用了上述技术方案,本发明的有益效果是:

16、(1)本发明中,以二维半导体/graphene垂直异质结的结构作为graphene电极,由于二维半导体的导电性能远差于graphene(半金属),因此在器件i区,电流从金属电极流入graphene,此接触界面为graphene与金属电极侧面形成的欧姆接触;在器件ii区,电流从二维半导体/graphene垂直结中的graphene层通过;在器件iii区,电流从graphene流入二维半导体沟道,然后通过二维半导体沟道,流入器件iv区,其中ii和iii区的界面、iii和iv的界面均为graphene与二维半导体形成的理想范德华接触;在器件iv区,电流从二维半导体/graphene垂直结中的graphene层通过;在器件v区,电流从graphene流入金属电极,此接触界面为graphene与金属电极侧面形成的欧姆接触。具体示意图见图5。

17、(2)本发明中,以二维半导体/graphene垂直异质结的结构作为graphene电极,异质结中的二维半导体层覆盖在graphene电极上方,这种设计使得graphene在图形化刻蚀二维半导体材料时免于反应,因此能够和常规微电子光刻工艺兼容,可以实现器件尺寸、位置和数量的可控,适用于不同电路的需求和进行规划化制备。

18、(3)本发明中,设计的二维半导体/graphene垂直异质结,因其性能也能被多种物理场(如光照、栅电压等)调制,所以也可以作为工作沟道与纯二维半导体材料沟道结合,应用在更多的场景。

技术特征:

1.一种基于石墨烯(graphene)电极的二维半导体器件阵列构建工艺,包括以下步骤:

2.根据权利要求1所述的一种基于graphene电极的二维半导体器件阵列构建工艺,其特征在于:所述步骤(1)中,graphene的制备方法无特需要求,尺寸只受限于现有紫外曝光设备的要求。

3.根据权利要求1所述的一种基于graphene电极的二维半导体器件阵列构建工艺,其特征在于:所述步骤(2)中,二维半导体材料的类型和制备方法无特需要求,尺寸只受限于现有紫外曝光设备的要求。

4.根据权利要求1所述的一种基于graphene电极的二维半导体器件阵列构建工艺,其特征在于:所述步骤(3)中,选用的工作衬底为微电子器件中常用衬底,如二氧化硅/硅(sio2/si)衬底、蓝宝石衬底等。

5.根据权利要求1所述的一种基于graphene电极的二维半导体器件阵列构建工艺,其特征在于:所述步骤中,采用的紫外曝光、显影、电子束镀膜、反应离子束刻蚀均为常规工艺。

6.根据权利要求1所述的一种基于graphene电极的二维半导体器件阵列构建工艺,其特征在于:所述步骤(5)中,设计的二维半导体/graphene垂直异质结,不仅可以作为电极,在别的物理场下(如光照、栅电压等),也同样可以作为沟道与纯二维半导体材料沟道结合,应用在更多的场景。

技术总结

发明名称:一种基于石墨烯电极的二维半导体器件阵列构建工艺摘要:本发明公开了一种基于石墨烯(Graphene)电极的二维半导体器件阵列构建工艺,属于微电子工艺和器件应用领域。本发明中,以二维半导体/Graphene垂直异质结的结构作为Graphene电极,异质结中的二维半导体层覆盖在Graphene电极上方,这种设计使得Graphene在图形化刻蚀二维半导体材料时免于反应,因此能够和常规微电子光刻工艺兼容,可以实现器件尺寸、位置和数量的可控,适用于不同电路的需求和进行规划化制备。

技术研发人员:曹倪,邓云锋,李萍剑,李雪松

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!