一种自适应耗尽空穴路径的新型IGBT结构

一种自适应耗尽空穴路径的新型igbt结构

技术领域

1.本发明涉及半导体领域,具体涉及一种自适应耗尽空穴路径的新型igbt结构。

背景技术:

2.半导体功率器件是电力电子系统进行功率控制和转换的基本电子元件。大量实践证明,半导体功率器件的发展是电力电子系统技术更新换代的关键。如今,能源消耗日益增长,尤其是电力需求矛盾日益尖锐。大力发展新型电力电子器件的设计制造和模块的开发应用是一个重要课题。因此,兼具mosfet栅极电压控制特性和bjt低导通电阻特性的igbt正成为电力电子系统的关键功率半导体器件。igbt与mosfet一样具有电压控制、大输入阻抗、低驱动功率、低导通电阻、低开关损耗、高工作频率和宽soa特性等优点。igbt是低噪声、智能化、高性能中小容量电力电子设备的首选器件。为了进一步提高igbt的导通特性具有p型浮空区结构的igbt结构被提出。

3.众所周知,具有p型浮空区结构的igbt由于具有高载流子注入增强(ie)效应,可以改善von和eoff之间的权衡关系,因此,p型浮空区结构已成为当前igbt器件的常规结构之一。然而,它具有较差的导通dic/dt可控性,因为来自p型浮空区的位移电流无意中增加了栅极电压。如何在确保导通压降较低的前提下增加导通电流变化率的可控性是当前igbt的研究重心之一。

技术实现要素:

4.针对增加igbt导通电流变化率的可控性、降低emi噪声,同时导通压降维持较低的需求,本发明提供了一种自适应耗尽空穴路径的新型igbt结构如图2所示。

5.本发明解决上述技术问题所采用的技术方案是:一种自适应耗尽空穴路径的新型igbt结构,其元胞结构从下往上依次为:p+集电区(1)、n型缓冲层(2)和n型漂移区(3),由p型基区(4)、p+型发射区(5)和n+型发射区(6)所组成的主流区,以及由p型浮空区(7)、p-掺杂区(8)所构成的自适应耗尽空穴路径区共同组成器件的正面结构。发射区间有sio2氧化层(9)和多晶硅(10)构成的栅极。p型基区(4)和p型浮空区(7)与n型漂移区(3)邻接,且所述p型浮空区(8)与p型基区(5)深度相同。

6.本发明的技术方案相对常规igbt器件,在p型浮空区(7)上方引入p-掺杂区(8),并使p-掺杂区(8)与发射极相连。且p-掺杂区(8)深度不宜太浅,以确保空穴不会穿过完全耗尽的p-掺杂区(8)。新器件在开启初期p-掺杂区(8)与发射极相连直接抽取p型浮空区(7)内的空穴,同时钳位p型浮空区(7)电位至低电位,从而抑制位移电流,降低emi噪声;在开启后期p-掺杂区(8)内部耗尽区逐渐拓宽至完全耗尽,由p型浮空区(7)、p-掺杂区(8)所构成的自适应耗尽空穴路径完全截断,ie效应增强,器件导通压降较低。另外,新器件在关断阶段自适应耗尽空穴路径导通并加速抽取基区空穴,从而加快器件关断,减小关断损耗。

7.进一步地,p型基区(4)和p型浮空区(7)与n型漂移区(3)邻接,且所述p型浮空区(7)的深度需比沟槽栅深度稍大。

8.进一步地,p型基区(4)和p型浮空区(7)下方添加载流子存储层(11),载流子存储层(11)深度不超过沟槽栅深度,且所述p型浮空区(7)与p型基区(4)深度相同。

9.进一步地,增大p-掺杂区(8)的掺杂浓度,增加开启阶段p-掺杂区(8)完全耗尽的时间,从而获得更好的emi特性。

10.本发明的有益效果为:本发明提供了一种自适应耗尽空穴路径的新型igbt结构,该结构在常规igbt结构的基础上,引入p-掺杂区,使p型浮空区与p-掺杂区构成的自适应耗尽空穴路径,该空穴路径在器件刚开启时打开,并随着栅极电压的增大而逐渐关闭,从而实现器件在低导通压降的条件下,拥有较低的emi噪声。另外,该空穴路径在器件关断时能提供额外的空穴抽取路径,从而减小器件关断时间,降低关断损耗。

附图说明

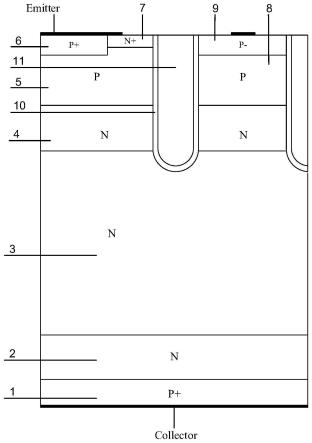

11.图1为常规igbt的结构示意图;

12.图2为实施例1的结构示意图;

13.图3为实施例2的结构示意图;

14.图4为实施例3的结构示意图;

具体实施方式

15.下面对本发明的具体实施方式进行描述,以便于本技术领域的技术人员理解本发明,但应该清楚,本发明不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本发明的精神和范围内,这些变化是显而易见的,一切利用本发明构思的发明创造均在保护之列。

16.实施例1

17.如图2所示,本例的自适应耗尽空穴路径的新型igbt结构,其元胞结构从下往上依次为:p+集电区(1)、n型缓冲层(2)、n型漂移区(3)、p型基区(4)、p+型发射区(5)、n+型发射区(6)、p型浮空区(7)和p-掺杂区(8)。发射区间有sio2氧化层(9)和多晶硅(10)构成的栅极。其中,p-掺杂区(8)与发射极相连,p型浮空区(7)和p-掺杂区(8)构成自适应耗尽空穴路径。p型基区(4)和p型浮空区(7)与n型漂移区(3)邻接,且所述p型浮空区(8)与p型基区(5)深度相同。且p-掺杂区(8)深度不宜太浅,以确保空穴不会穿过完全耗尽的p-掺杂区(8)。

18.本例的工作原理为:

19.在器件开启阶段初期,p-掺杂区(8)还未产生耗尽层,此时p型浮空区(7)和p-掺杂区(8)构成的自适应耗尽空穴路径导通,钳位p型浮空区(7)电位,位移电流较小,栅极电压稳定,电流变化率dic/dt可控性增强,emi噪声减小。在器件开启阶段末期,p-掺杂区(8)完全耗尽,形成空穴势垒区,阻止空穴经由此处被发射极提取,增强电导调制效应,从而降低导通压降。在器件关断阶段,p-掺杂区(8)逐渐恢复到准中性区,自适应空穴路径导通,加快器件关断,降低关断损耗。

20.实施例2

21.如图3所示,本例与实施例1的区别在于所述p型浮空区(7)的深度需比沟槽栅深度稍大。与实施例1相比,本例器件在导通时发射极侧载流子更多分布在p型基区(4)下方,导通压降更低。

22.实施例3

23.如图4所示,本例与实施例1的区别在于所述p型基区(4)和p型浮空区(7)下方添加载流子存储层(11),且载流子存储层(11)深度不超过沟槽栅深度。与实施例1相比,载流子存储层(11)在器件导通时使p型基区(4)和p型浮空区(7)下方电位升高,导致聚集在发射极侧载的流子数量更多,从而降低导通压降。

24.进一步地,增大p-掺杂区(8)的掺杂浓度,增加开启阶段p-掺杂区(8)完全耗尽的时间,从而获得更好的emi特性。

25.综上所述,本发明提供了一种自适应耗尽空穴路径的新型igbt结构,该结构在常规igbt结构的基础上,引入p-掺杂区,使p型浮空区与p-掺杂区构成的自适应耗尽空穴路径,该空穴路径在器件刚开启时打开,并随着栅极电压的增大而逐渐关闭,从而在确保器件拥有低导通压降的同时,通过自适应耗尽的p-掺杂区控制空穴路径在开启阶段导通以实现较低的emi噪声。另外,p-掺杂区在器件关断时逐渐恢复成准中性,从而提供额外的空穴抽取路径,以此减小器件关断时间,降低关断损耗。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1