半导体结构及其制作方法、检测方法与流程

本公开涉及半导体,具体地,涉及一种半导体结构及其制作方法、检测方法。

背景技术:

1、随着集成电路工艺技术的高速发展,微电子封装技术逐渐成为制约半导体技术发展的主要因素。为了实现电子封装的高密度化,获得更优越的性能和更低的总体成本,技术人员研究出一系列先进的封装技术。其中三维封装技术具有良好的电学性能以及较高的可靠性,同时能实现较高的封装密度,被广泛应用于各种高速电路以及小型化系统中。硅通孔(tsv,throught silicon via)技术是三维集成电路中堆叠芯片实现互连的一种新技术,通过在晶圆上制作出许多垂直互连tsv结构来实现不同芯片之间的电互连。tsv技术能够使芯片在三维方向堆叠的密度最大、芯片之间的互连线最短、外形尺寸最小,并且大大改善芯片速度和低功耗的性能,是目前电子封装技术中最引人注目的一种技术。

2、然而,tsv技术仍然面临着一些挑战,例如tsv结构中铜扩散的情况时有发生,tsv中的铜扩散会造成一定的漏电,使得影响芯片的性能。如何及时的监测tsv中的漏电以避免更大的损失,成为亟待解决的问题。

3、公开内容

4、有鉴于此,第一方面,本公开实施例提出一种半导体结构,包括:

5、衬底;

6、第一介质层,位于所述衬底上,且所述衬底以及所述第一介质层被划分为沿第一方向分布的第一区域和第二区域;所述第一方向垂直于第二方向,所述第二方向为所述衬底的厚度方向;

7、多个第一导电通孔结构,位于所述第一区域以及所述第二区域中,每个所述第一导电通孔结构沿所述第二方向从所述第一介质层延伸至所述衬底中;

8、至少一个检测结构,所述至少一个检测结构位于所述第二区域中,每个所述检测结构均包括一个所述第一导电通孔结构以及至少一个第二导电通孔结构,每个所述第二导电通孔结构沿所述第二方向从所述第一介质层延伸至所述衬底中;所述检测结构用于检测所述第一导电通孔结构的漏电情况;

9、第二介质层,位于所述衬底以及所述第一导电通孔结构之间。

10、上述方案中,所述第一导电通孔结构延伸至所述衬底的深度大于所述第二导电通孔结构延伸至所述衬底的深度。

11、上述方案中,每个所述检测结构均包括一个第一导电通孔结构以及多个第二导电通孔结构。

12、上述方案中,所述第一导电通孔结构的材料以及所述第二导电通孔结构的材料均包括金属材料,且所述第一导电通孔结构的材料与所述第二导电通孔结构的材料相同或不同。

13、上述方案中,所述半导体结构还包括:第三导电通孔结构,所述第三导电通孔结构与所述第二导电通孔结构的结构基本相同。

14、上述方案中,所述第一区域包括器件区域,所述第二区域包括切割道区域。

15、上述方案中,所述第二导电通孔结构包括沿第二方向依次堆叠的第一子导电通孔结构、第二子导电通孔结构、第三子导电通孔结构,所述第一子导电通孔结构位于所述衬底中,所述第二子导电通孔结构以及所述第三子导电通孔结构位于所述第一介质层中。

16、上述方案中,所述半导体结构还包括重布线层,所述重布线层形成在第一介质层中与所述第一导电通孔结构和所述第二导电通孔结构接触,所述重布线层包括多个导电焊盘,且每个所述第一导电通孔结构以及每个所述第二导电通孔结构上均设置有一个导电焊盘。

17、第二方面,本公开实施例提出半导体结构的检测方法,包括:

18、提供如上述方案中任一方案所述的半导体结构;

19、检测所述检测结构中的第一导电通孔结构和第二导电通孔结构之间的漏电参数;

20、根据所述漏电参数判断所述第一导电通孔结构是否存在漏电。

21、上述方案中,所述漏电参数包括漏电流。

22、上述方案中,所述漏电参数为漏电流;所述根据所述漏电参数判断所述第一导电通孔结构是否存在漏电,包括:

23、当所述漏电流大于0时,所述第一导电通孔结构存在漏电;

24、当所述漏电流等于0时,所述第一导电通孔结构不存在漏电。

25、上述方案中,每个所述检测结构均包括一个第一导电通孔结构以及多个第二导电通孔结构;

26、所述检测所述检测结构中的第一导电通孔结构和第二导电通孔结构之间的漏电参数,包括:

27、检测所述检测结构中的第一导电通孔结构和每个第二导电通孔结构之间的漏电参数,得到多个漏电参数;

28、所述根据所述漏电参数判断所述第一导电通孔结构是否存在漏电,包括:

29、根据多个所述漏电参数判断所述第一导电通孔结构是否存在漏电。

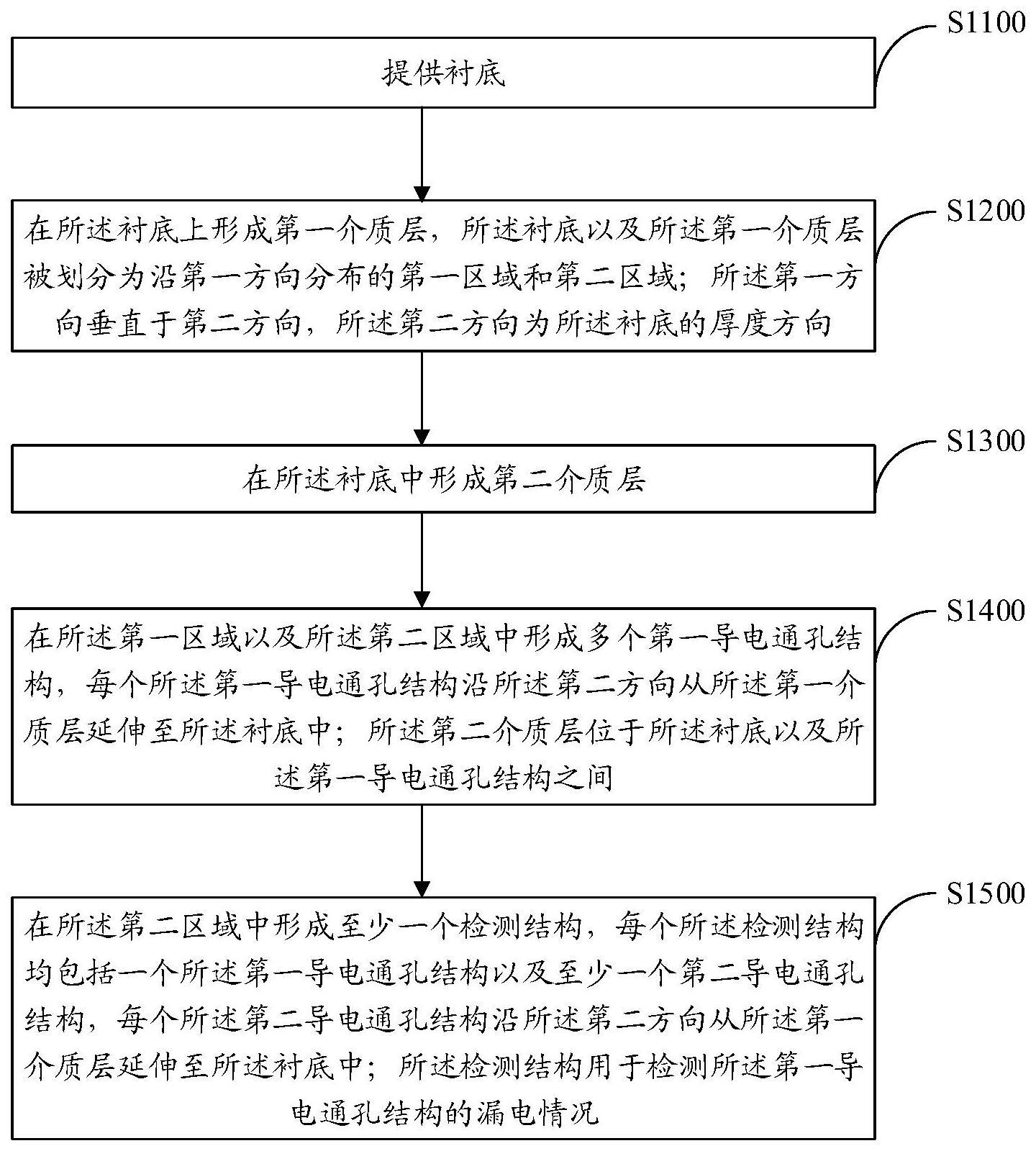

30、第三方面,本公开实施例提出半导体结构的制作方法,所述方法包括:

31、提供衬底;

32、在所述衬底上形成第一介质层,所述衬底以及所述第一介质层被划分为沿第一方向分布的第一区域和第二区域;所述第一方向垂直于第二方向,所述第二方向为所述衬底的厚度方向;

33、在所述衬底中形成第二介质层;

34、在所述第一区域以及所述第二区域中形成多个第一导电通孔结构,每个所述第一导电通孔结构沿所述第二方向从所述第一介质层延伸至所述衬底中;所述第二介质层位于所述衬底以及所述第一导电通孔结构之间;

35、在所述第二区域中形成至少一个检测结构,每个所述检测结构均包括一个所述第一导电通孔结构以及至少一个第二导电通孔结构,每个所述第二导电通孔结构沿所述第二方向从所述第一介质层延伸至所述衬底中;所述检测结构用于检测所述第一导电通孔结构的漏电情况。

36、上述方案中,所述第一导电通孔结构延伸至所述衬底的深度大于所述第二导电通孔结构延伸至所述衬底的深度。

37、上述方案中,所述方法还包括:

38、在形成第二导电通孔结构的同时,在所述第一区域中形成第三导电通孔结构;所述第三导电通孔结构与所述第二导电通孔结构的结构基本相同。

39、上述方案中,形成所述第二导电通孔结构包括:

40、形成沿第二方向依次堆叠的第一子导电通孔结构、第二子导电通孔结构、第三子导电通孔结构,所述第一子导电通孔结构位于所述衬底中,所述第二子导电通孔结构以及所述第三子导电通孔结构位于所述第一介质层中。

41、本公开实施例提供了一种半导体结构及其制作方法以及检测方法,所述半导体结构包括:衬底;第一介质层,位于所述衬底上,且所述衬底以及所述第一介质层被划分为沿第一方向分布的第一区域和第二区域;所述第一方向垂直于第二方向,所述第二方向为所述衬底的厚度方向;多个第一导电通孔结构,位于所述第一区域以及所述第二区域中,每个所述第一导电通孔结构沿所述第二方向从所述第一介质层延伸至所述衬底中;至少一个检测结构,所述至少一个检测结构位于所述第二区域中,每个所述检测结构均包括一个所述第一导电通孔结构以及至少一个第二导电通孔结构,每个所述第二导电通孔结构沿所述第二方向从所述第一介质层延伸至所述衬底中;所述检测结构用于检测所述第一导电通孔结构的漏电情况;第二介质层,位于所述衬底以及所述第一导电通孔结构之间。本公开实施例中,一方面;通过在第二区域中设置检测结构,且每个所述检测结构均包括一个所述第一导电通孔结构以及至少一个第二导电通孔结构,且第一导电通孔结构和第二导电通孔结构均延伸至衬底中,这样使得可以直接利用第二区域中的第一导电通孔结构和第二导电通孔结构共同检测第一导电通孔结构的漏电;另一方面,由于可以直接在检测结构上利用外部检测装置直接检测得到漏电参数,从而判断第一导电通孔结构的漏电情况,这样使得能及时检测到漏电问题,避免由于未能及时检测到漏电问题导致更大的损失。

技术实现思路

- 还没有人留言评论。精彩留言会获得点赞!