具有气隙的半导体结构的制备方法与流程

本公开关于一种半导体结构以及该半导体结构的制备方法。特别涉及一种具有一气隙的半导体结构以及该半导体结构的制备方法。

背景技术:

1、由于动态随机存取存储器(dram)的结构的简单性,与例如静态随机存取存储器(sram)的其他类型的存储器相比较,一dram可在每个芯片面积上提供更多的存储器胞。dram由多个dram胞所组成。每个dram胞具有一电容器以及一晶体管,该电容器用于存储信息,该晶体管则是耦合到该电容器以控制该电容器何时充电或放电。在一读取操作期间,字元线(wl)被有效化(asserted),借此导通该晶体管。导通的该晶体管允许一感测放大器经由一位元线(bl)读取跨经该电容器两端的一电压。在一写入操作期间,当接触wl时则将要写入的数据提供给bl。

2、为了满足更大的存储器存储容量的需求,dram存储器胞的尺寸不断缩减;如此一来,则大大增加该等dram的一封装密度。然而,由于dram存储器胞的尺寸缩减,导致寄生电容增加的电容耦合已成为越来越重要的问题。作为寄生电容的结果,dram存储器胞的速度则被非期望地降低,并且一整体元件性能受到负面影响。

3、上文“的“现有技术”说明仅提供背景技术,并未承认上文“的“现有技术”说明揭示本公开的标的,不构成本公开的现有技术,且上文“的“现有技术”的任何说明均不应作为本公开的任一部分。

技术实现思路

1、本公开的一实施例提供一种半导体结构的制备方法。该制备方法包括形成一第一位元线以及一第二位元线在一基底上;形成一图案化层在该第一位元线与该第二位元线之间,其中该图案化层覆盖该基底并围绕该第一位元线的一下部以及该第二位元线的一下部;形成一共形层在该图案化层上;形成一接触点在该共形层上以及在该第一位元线与该第二位元线之间,其中在该接触点的一顶部与该基底之间的一垂直距离大于在该图案化层的一顶部与该基底之间的一垂直距离;移除该图案化层与该共形层;以及形成一气隙在该接触点与该第一位元线之间,或是在该接触点与该第二位元线之间,其中该气隙被一介电层所密封。

2、在一些实施例中,该制备方法还包括形成一牺牲层在该第一位元线上、在该第二位元线上以及在该基底上;以及移除该牺牲层围绕该第一位元线的一上部以及该第二位元线的一上部的一部分,借此形成该图案化层。

3、在一些实施例中,该图案化层的一高度大致大于从该基底测量的该第一位元线的一金属层的一高度或是该第二位元线的一金属层的一高度。

4、在一些实施例中,该共形层覆盖该图案化层的一顶部、该第一位元线的一上部以及该第二位元线的一上部。

5、在一些实施例中,该制备方法还包括在形成该接触点之前,移除该图案化层的一部分以及该共形层的一部分,借此暴露基底。

6、在一些实施例中,该制备方法还包括沉积一接触点材料层在该共形层、该第一位元线以及该第二位元线上;以及移除该接触点材料层的一部分,借此形成该接触点,其中该接触点的一高度大致大于该图案化层的一高度。

7、在一些实施例中,在该接触点的一顶部与该第一位元线之间的一第一水平距离大致小于在该接触点的一下部与该第一位元线之间的一第二水平距离。

8、在一些实施例中,该第一水平距离由该共形层的一厚度所界定。

9、在一些实施例中,该第二水平距离由该图案化层的一厚度以及该共形层的一厚度所界定。

10、在一些实施例中,该气隙的形成包括沉积该介电层在该接触点与该第一位元线之间,或是在该接触点与该第二位元线之间;以及填满在该第一位元线与该接触点的一顶部之间的一空间,或是在该第二位元线与该接触点的该顶部之间的一空间。

11、在一些实施例中,该介电层的一厚度大致大于或等于该共形层的一厚度的一半。

12、在一些实施例中,该气隙的一宽度大致等于该图案化层的一厚度。

13、本公开的另一实施例提供一种半导体结构的制备方法。该制备方法包括形成一位元线在一基底上;形成一第一介电层在该基底上,并围绕该位元线的一下部;形成一第二介电层在该基底与该第一介电层上;形成一接触点在该第二介电层上,其中在该接触点的一顶部与该基底之间的一垂直距离大于在该第一介电层的一顶部与该基底之间的一垂直距离;移除该第一介电层与该第二介电层;以及共形地形成一第三介电层在该位元线、该基底以及该接触点上,借此形成一气隙在该接触点与该位元线之间。

14、在一些实施例中,该第一介电层的形成包括形成一第一共形层在该基底与该位元线上;形成一遮罩层在第一共形层上;移除该遮罩层的一部分以及该第一共形层的一部分,借此暴露该位元线的一上部;以及移除该遮罩层的一余留部分。

15、在一些实施例中,该第一介电层的该高度由该遮罩层所界定。

16、在一些实施例中,该第二介电层的制作技术包括一共形沉积。

17、在一些实施例中,该第一介电层的一厚度介于1到5纳米之间。

18、在一些实施例中,该第二介电层的一厚度介于5到12纳米之间。

19、在一些实施例中,该制备方法还包括在形成该接触点之前,蚀刻该第一介电层与该第二介电层,借此形成一间隙子结构以围绕该位元线;以及暴露该基底。

20、在一些实施例中,该间隙子结构朝向该位元线的一顶部逐渐变细。

21、在一些实施例中,该第一介电层、该第二介电层以及该第三介电层中的至少其中一个的制作技术包括原子层沉积。

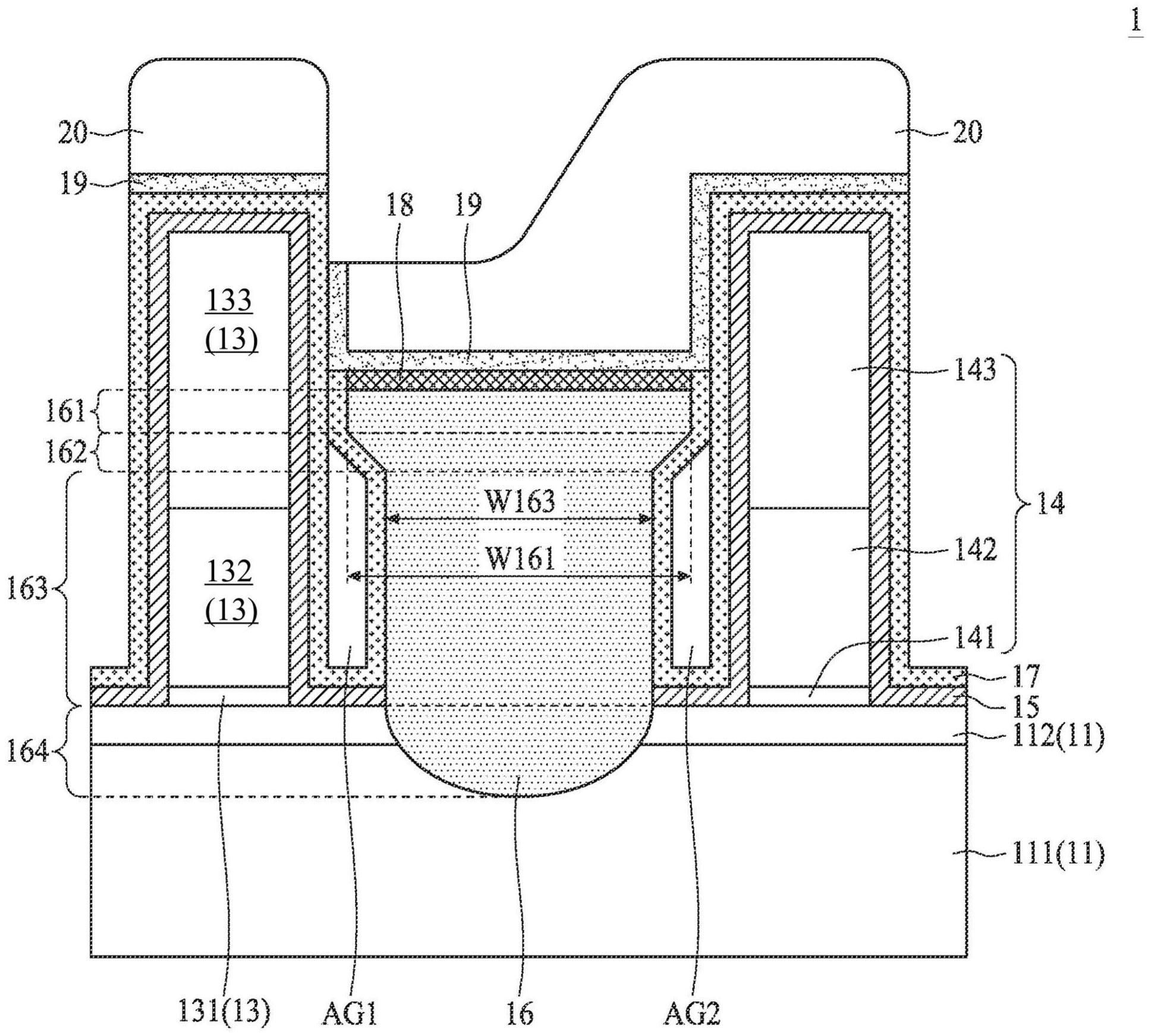

22、本公开的另一实施例提供一种半导体结构。该半导体结构包括一第一位元线,设置在一基底上;一接触点,邻近设置在该基底上的该第一位元线设置,其中在该接触点的一上部与该第一位元线之间的一第一距离小于该接触点的一下部与该第一位元线之间的一第二距离;一介电层,共形地设置在该第一位元线、该基底以及该接触点上;以及一第一气隙,被该介电层所密封,并且被该第一位元线、该基底以及该接触点所界定。

23、在一些实施例中,该第一位元线包括一金属层,且在该接触点的一顶部与该基底之间的一垂直距离大于在该金属层的一顶部与该基底之间的一垂直距离。

24、在一些实施例中,在该接触点的该顶部与该基底之间的该垂直距离大于在该金属层的该顶部与该基底之间的该垂直距离(约5到45纳米)。

25、在一些实施例中,该第一位元线包括一金属层,且在该第一气隙的一顶部与该基底之间的一垂直距离大于或等于在该金属层的一顶部与该基底之间的一垂直距离。

26、在一些实施例中,在该第一气隙的该顶部与该金属层的该顶部之间的一垂直距离介于0到10纳米之间。

27、在一些实施例中,该第一位元线的一顶部与该基底之间的一垂直距离大于在该接触点的一顶部与该基底之间的一垂直距离(约90到130纳米)。

28、在一些实施例中,在该基底上方的该接触点朝向该基底逐渐变细。

29、在一些实施例中,该接触点经配置而成一t形。

30、在一些实施例中,介电层的一厚度介于3到6纳米。

31、在一些实施例中,该介电层填满在该接触点的该顶部与该第一位元线之间的一空间。

32、在一些实施例中,在该第一距离与该第二距离之间的差大致等于该第一气隙的一宽度。

33、在一些实施例中,该半导体结构还包括一第二位元线,设置在该基底上,其中该接触点设置在该第一位元线与该第二位元线之间,而该介电层共形地设置在该第二位元线上;以及一第二气隙,被该介电层所密封,并且由该第二位元线、该基底以及该接触点所界定。

34、在一些实施例中,在该第二气隙的一顶部与该基底之间的一垂直距离大致大于在该第二位元线的一金属层的一顶部与该基底之间的一垂直距离。

35、在一些实施例中,在该接触点的该底部与该第二位元线之间的一第三距离大致小于在该接触点的该下部与该第二位元线之间的一第四距离。

36、上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或工艺而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离权利要求所界定的本公开的构思和范围。

- 还没有人留言评论。精彩留言会获得点赞!