半导体器件及其制造方法与流程

本发明涉及一种半导体器件及其制造方法,并且更特别地,涉及一种包括形成在层间绝缘膜中的接触孔的半导体器件及其制造方法。

背景技术:

1、作为功率器件,应用竖直沟槽栅极结构的功率mosfet(金属氧化物半导体场效应晶体管)和igbt(绝缘栅极双极晶体管)是已知的。包括功率器件的一些半导体器件(半导体芯片)除了其中形成主器件的单元区域之外还包括电阻区域和二极管区域。

2、例如,在日本未审查专利申请公开2006-324570中公开了一种包括功率mosfet和保护二极管的半导体器件。保护二极管形成在元件隔离部分上并且覆盖有层间绝缘膜。在层间绝缘膜中形成接触孔,并且在接触孔中嵌入栅极布线和源极电极。保护二极管的一端电连接到栅极布线,保护二极管的另一端电连接到源电极。

技术实现思路

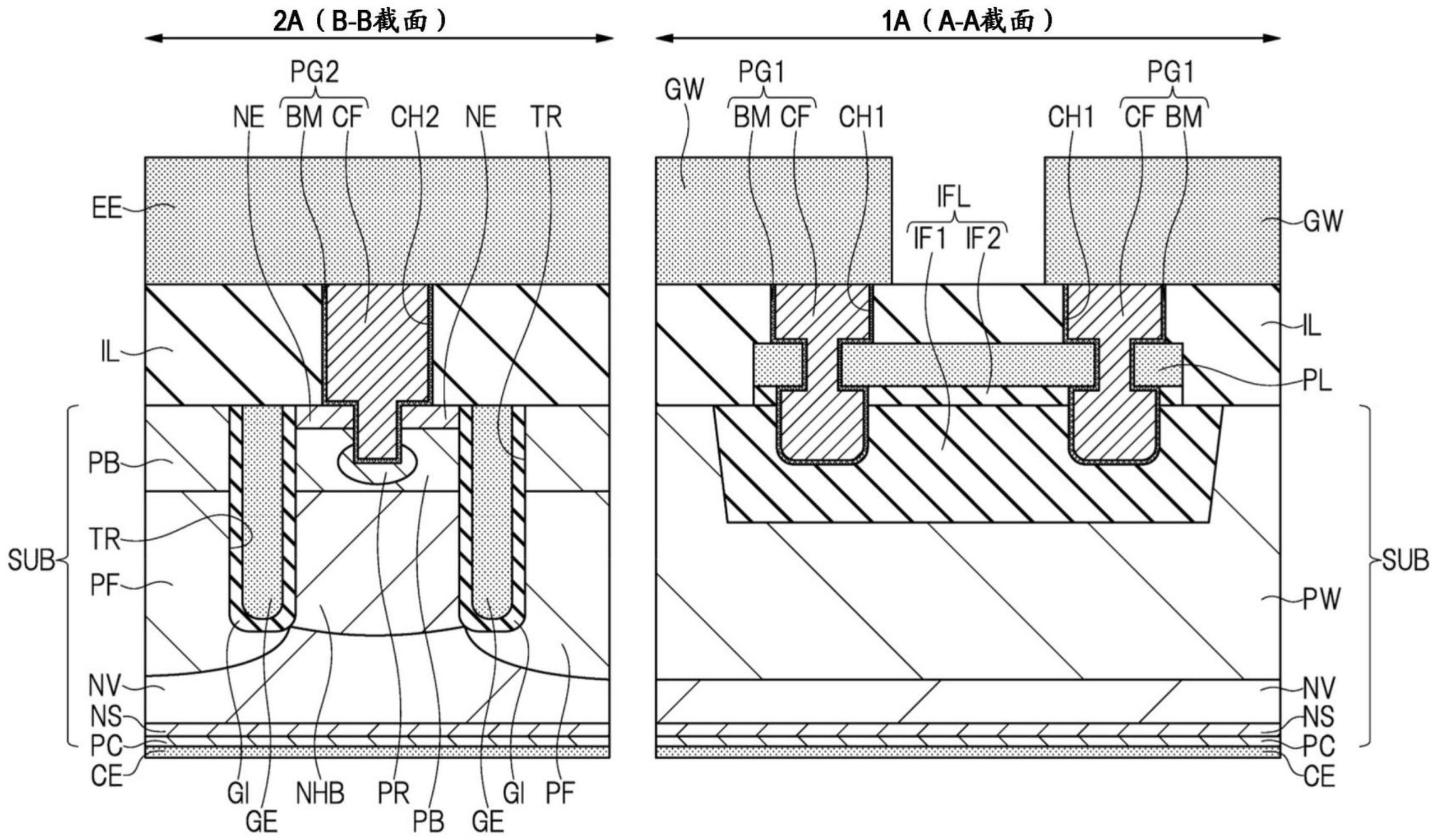

1、在下文中,将参考图27至图32描述由本技术的发明人研究的研究示例1至示例3的半导体器件。这些器件包括作为动力器件的igbt。图27至图32示出了其中形成电阻元件的区域,作为不同于igbt的示例性半导体元件。这里,导电膜pl构成电阻器件。

2、图27示出了研究示例1的半导体器件。如图27中所示,在研究示例1中,导电膜pl经由绝缘膜if2形成在半导体衬底sub的上表面上。绝缘膜if2例如是氧化硅膜。导电膜pl例如是多晶硅膜,并且构成电阻器件。在半导体衬底sub的上表面上形成层间绝缘膜il,以便覆盖导电膜pl。层间绝缘膜il例如是通过cvd方法形成的氧化硅膜。

3、在层间绝缘膜il中形成接触孔ch1。接触孔ch1在与到达igbt的体区域和发射极区域的接触孔相同的工艺中形成。

4、这里,接触孔ch1通过被蚀刻得比层间绝缘膜il的厚度更深而形成。因此,接触孔ch1也形成在导电膜pl的一部分中。如果导电膜pl的厚度足够厚(诸如600nm),则接触孔ch1的底部部分位于导电膜pl内部,并且接触孔ch1不会到达半导体衬底的sub。

5、图28示出了研究示例2的半导体器件。在研究示例2中,该器件比研究示例1中的器件更小型化。因此,如图28中所示,通过cmp方法在层间绝缘膜il的上表面上执行平坦化处理,以提高接触孔的加工精度。在诸如soc(片上系统)的精细工艺的半导体器件中,使用通过在开放空间中放置虚拟图案来进一步平坦化层间绝缘膜il的上表面的方法。另一个方面,在诸如igbt的功率器件中,使用此类方法不是很现实,因为几乎没有空间来填充虚拟图案。

6、因此,在研究示例2中,导电膜pl的厚度被设置为比研究示例1的薄,并且被设置为例如250nm。因此,层间绝缘膜il的上表面中的台阶差减小。

7、然而,由于导电膜pl的厚度和导电膜pl上的层间绝缘膜il的厚度减小,所以当形成接触孔ch1时,接触孔ch1的底部部分可能穿透导电膜if2。此外,取决于形成接触孔ch1时的蚀刻速率,接触孔ch1的底部部分到达半导体衬底的sub,并且出现短路故障。

8、为了避免此类问题,可以设想通过在与到达igbt的体区域和发射极区域的接触孔不同的制造过程中形成接触孔ch1来单独控制接触孔ch1的深度。然而,在此情况下,由于执行了掩模数量的增加和制造过程的添加,因此增加了制造成本。

9、图29至图32示出了研究示例3的半导体器件。在研究示例3中,如图29中所示,绝缘膜if1形成在绝缘膜if2下面。绝缘膜if1例如是通过热氧化方法形成的氧化硅膜。通过在导电膜pl下面设置绝缘层ifl,该绝缘层ifl是作为绝缘膜if1和绝缘膜if2的层压膜,即使接触孔ch1穿透绝缘膜if2,也可以防止接触孔ch1的底部到达半导体衬底的sub。

10、在最近的工艺中,为了增加插塞和嵌入在igbt的接触孔中的发射极区域之间的接触面积以及插塞pg1和导电膜pl之间的接触面积,在层间绝缘膜il上执行各向同性蚀刻工艺。在此各向同性蚀刻工艺中,使用包含氢氟酸的溶液,并且选择性地蚀刻氧化硅膜。

11、图30示出了各向同性蚀刻工艺后的状态。通过各向同性蚀刻工艺,层间绝缘膜il的侧表面收缩,并且导电膜pl的上表面被暴露。与此同时,由氧化硅膜制成的绝缘膜if2和绝缘膜if1的一部分也被退回,并且导电膜pl的下表面被暴露。

12、此后,如图31中所示,在接触孔ch1中形成阻挡金属膜bm,如图32中所示,在阻挡金属膜bm上形成导电膜cf以填充接触孔ch1的内部。阻挡金属膜bm和导电膜cf形成插塞pg1。阻挡金属膜bm通过cvd方法形成,并且由例如钛膜和氮化钛的层压膜形成。导电膜cf通过cvd方法形成并且由例如钨膜制成。

13、通过上面所描述的各向同性蚀刻工艺,在接触孔ch1中从导电膜pl的侧表面到层间绝缘膜il的侧表面的距离变为距离l2。从导电膜pl的下表面到接触孔ch1的底部部分的距离是距离l3。通过热氧化方法形成的绝缘膜if1的蚀刻速率略低于通过cvd方法形成的绝缘膜if2和层间绝缘膜il的蚀刻速率。因此,距离l3等于或短于距离l2。

14、如图31中所示,当距离l3短时,因为当形成阻挡金属膜bm时,在cvd方法中使用的气体没有充分供应到导电膜pl的下表面附近,所以很可能产生阻挡金属膜bm的厚度不够的部分。

15、当形成导电膜cf时,阻挡金属膜bm也用作晶种膜。因此,如图32中所示,在阻挡金属膜bm薄的部分,导电膜cf不太可能充分生长,并且可能在接触孔ch1中产生间隙。此外,在未形成阻挡金属膜bm的部分中,wf6气体与导电膜cf(多晶硅膜)反应,并且出现导电膜cf的一部分不存在的缺陷。此类位置在图32中示出为有缺陷的位置20并且在随后的制造步骤中容易腐蚀或变形。

16、为了增加距离l3,可以想到增加各向同性蚀刻工艺的持续时间,但是这也增加了距离l2并且加宽了接触孔ch1的开口宽度。因此,igbt的接触孔的开口宽度变得太宽,使得igbt的栅极电极暴露在igbt的接触孔中。因此,存在igbt的栅极电极电连接到发射极电极的问题。

17、本技术的主要目的是抑制上述缺陷并且提高半导体器件的可靠性。从本说明书和附图的描述中,其他目的和新颖特征将变得显而易见。

18、解决问题的手段

19、本技术中公开的典型实施例将简要描述如下。

20、根据实施例的半导体器件包括:

21、半导体衬底,具有上表面和下表面;

22、绝缘层,形成为从半导体衬底的上表面到半导体衬底的内部;

23、第一导电膜,形成在绝缘层上,

24、层间绝缘膜,形成在半导体衬底的上表面上以覆盖第一导电膜;

25、第一接触孔,形成在层间绝缘膜、第一导电膜和绝缘层中,使得第一接触孔的底部部分定位在绝缘层中;以及

26、第一插塞,形成为填充第一接触孔,

27、其中在第一接触孔中,层间绝缘膜的侧表面与第一导电膜的侧表面分离,使得第一导电膜的上表面的一部分从层间绝缘膜暴露,

28、其中在第一接触孔中,该绝缘层的侧表面与该第一导电膜的侧表面分离,使得该第一导电膜的下表面的一部分从该绝缘层暴露,并且

29、其中从第一导电膜的下表面的一部分到第一接触孔的底部部分的第一距离比从第一导电膜的侧表面到层间绝缘膜的侧表面的第二距离长。

30、根据实施例的制造半导体器件的方法包括:

31、(a)制备具有上表面和下表面的半导体衬底。

32、(b)在步骤(a)之后,形成从半导体衬底的上表面延伸到半导体衬底内部的第一绝缘膜;

33、(c)在步骤(b)之后,在第一绝缘膜上形成厚度比第一绝缘膜薄的第二绝缘膜;

34、(d)在步骤(c)之后,在第二绝缘膜上形成第一导电膜;

35、(e)在步骤(d)之后,在半导体衬底的上表面上形成层间绝缘膜,以便覆盖第一导电膜;

36、(f)在步骤(e)之后,在层间绝缘膜、第一导电膜、第二绝缘膜和第一绝缘膜中形成第一接触孔,使得第一接触孔的底部部分位于第一绝缘膜中,

37、(g)在步骤(f)之后,使层间绝缘膜、第二绝缘膜和第一绝缘膜经受各向同性蚀刻工艺,以及

38、(h)在步骤(g)之后,将第一插塞嵌入所述第一接触孔中,

39、其中通过步骤(g)中的各向同性蚀刻工艺,在第一接触孔中,层间绝缘膜的侧表面与第一导电膜的侧表面分离,使得第一导电膜的上表面的一部分从层间绝缘膜暴露,

40、其中通过该步骤(g)中的各向同性蚀刻工艺,在第一接触孔中,该第一绝缘膜的侧表面和该第二绝缘膜的侧表面与该第一导电膜的侧表面分离,使得该第一导电膜的下表面的一部分从该第一绝缘膜和第二绝缘膜暴露,并且

41、其中从第一导电膜的下表面到第一接触孔的底部部分的第一距离比从第一导电膜的侧表面到层间绝缘膜的侧表面的第二距离长。

42、根据实施例的制造半导体器件的方法是制造具有第一区域和不同于第一区域的第二区域的半导体器件的方法。一种制造该半导体器件的方法,包括以下步骤:

43、(a)制备具有上表面和下表面的半导体衬底的步骤,

44、(b)在步骤(a)之后,在第一区域中从高于半导体衬底的上表面的位置到半导体衬底的内部形成第一绝缘膜的步骤,

45、(c)在步骤(b)之后,在第二区域中的半导体衬底的上表面侧上形成沟槽的步骤,

46、(d)对第一绝缘膜进行各向同性蚀刻工艺以使第一绝缘膜的厚度在步骤(c)后变薄的步骤,(d)对第一绝缘膜进行各向同性蚀刻工艺,使得第一绝缘膜的厚度在步骤(c)之后变薄的步骤,

47、(e)在步骤(d)之后在沟槽中形成栅极绝缘膜的步骤,

48、(f)在步骤(e)之后,在栅极绝缘膜上形成栅极电极以填充沟槽的步骤,

49、(g)在步骤(f)之后,形成覆盖第一区域中的第一绝缘膜和覆盖第二区域中的栅极电极的第二绝缘膜的步骤,在步骤(f)之后,第二绝缘膜的厚度小于第一绝缘膜的厚度;

50、(h)在步骤(g)之后,在第一区域和第二区域中的第二绝缘膜上形成第二导电膜的步骤;

51、(i)在步骤(h)之后,移除第一导电膜和第二绝缘膜,使得第一导电膜和第二绝缘膜选择性地保留在第一绝缘膜上的步骤;

52、(j)在步骤(i)之后,在半导体衬底的上表面侧上形成第一导电类型的第一杂质区域,使得其底部部分定位在沟槽的底部部分上方的步骤,

53、(k)在步骤(j)之后,在第一杂质区域中形成与第一导电类型相反的第二导电类型的第二杂质区域的步骤,

54、(l)在步骤(k)之后,在第一区域和第二区域中的半导体衬底的上表面上形成层间绝缘膜以覆盖第一区域中的第一导电膜并且覆盖第二区域中的栅极电极、第一杂质区域和第二杂质区域的步骤,

55、(m)在步骤(l)之后,通过cmp方法对第一区域和第二区域中的层间绝缘膜执行平坦化处理的步骤;

56、(n)在步骤(m)之后,在第一区域中的层间绝缘膜、第一导电膜、第二绝缘膜和第一绝缘膜中形成第一接触孔,使得第一接触孔的底部部分位于第一绝缘膜中,并且在第二区域中的层间绝缘膜、第二杂质区域和第一杂质区域中形成第二接触孔,使得第二接触孔的底部部分位于第一杂质区域中;

57、(o)在步骤(n)之后,在第一接触孔中埋置第一插塞并且在第二接触孔中埋置第二插塞的步骤。

58、根据一个实施例,可以提高半导体器件的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!