一种用于SiC功率器件的复合终端结构及其制造方法

本发明涉及半导体功率器件,尤其涉及一种用于sic功率器件的复合终端结构及其制造方法。

背景技术:

1、碳化硅材料因其优越的宽禁带、高临界击穿电场、高电子迁移率等材料特性,其功率器件备受关注并广泛用于逆变器、高压开关和电机驱动器等领域。击穿电压电参数是衡量功率半导体器件可靠性的重要参数,然而,在采用平面扩散技术的实际功率半导体中,高压结必须在某一有限位置与表面相交,由此产生的结曲率压缩等势线,其中结弯曲到表面,并增加最大电场。为了改善击穿特性和可靠性,将最大电场点从表面转移到衬底内部并减小峰值是有效手段。

2、但需要高击穿电压的器件往往面临着结终端附近表面电场过大和体电场峰值过大之间的权衡问题。场限环(field limiting ring,n+场限环)作为一种减少主结处场拥挤量的有效手段已被广泛应用于结终端技术中,n+场限环是低压(1700v)应用中最常见的结构之一,随着电压等级的不断提高,n+场限环的环数需要增加且每个注入间隔需要高光刻精度,但传统的n+场限环由于硅氧化物界面附近的高电场峰值而存在氧化物可靠性问题。由此可见现有技术难以同时提高击穿电压和改善可靠性问题。

技术实现思路

1、有鉴于此,本发明的目的在于提出一种用于sic功率器件的复合终端结构及其制造方法,能够同时提高击穿电压和改善可靠性问题。

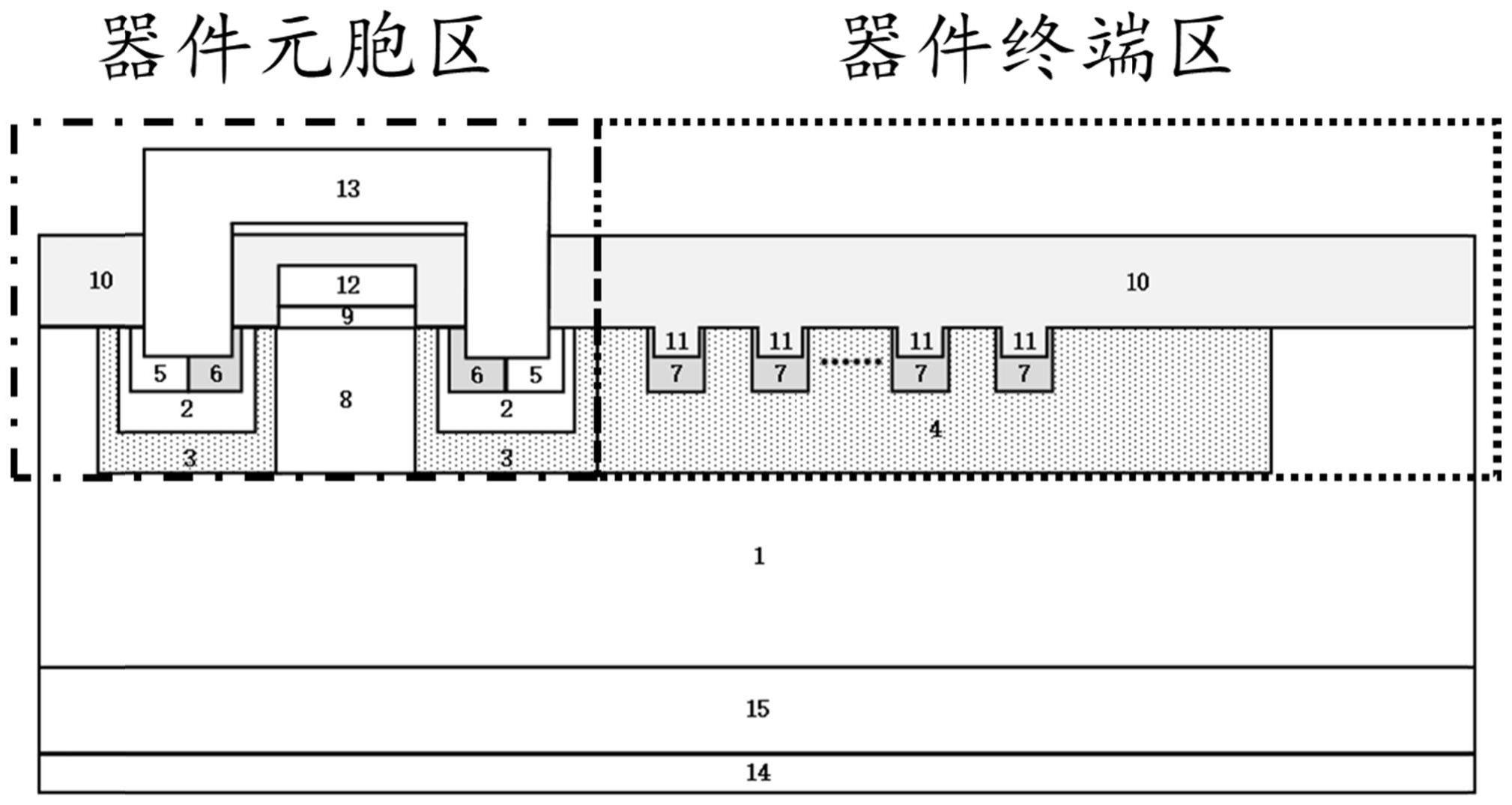

2、根据本发明的一个方面,提供一种用于sic功率器件的复合终端结构,包括形成于n型重掺杂衬底上的n-漂移区,所述n-漂移区之上依次设有器件元胞区和器件终端区;所述器件元胞区包括间隔设置的深p阱区,以及深p阱区与所述n-漂移区形成的pn结组成主结;

3、所述器件终端区包括:p型结终端拓展区、钝化层;该p型结终端拓展区靠近主结一侧间隔设置有若干n+场限环;所述p型结终端拓展区表面淀积有钝化层,在n+场限环蚀刻有刻蚀沟槽。

4、根据本发明的另一个方面,提供一种用于sic功率器件的复合终端结构的制备方法,所述方法包括:s1、取一碳化硅片上淀积sio2氧化层,在氧化层上布设光刻胶并刻蚀p阱区窗口,在碳化硅片上进行p型离子随机注入,在此同时形成p阱区;s2、在碳化硅片上淀积sio2氧化层,在氧化层上布设光刻胶并刻蚀深p阱区及p型结终端拓展区开孔,在碳化硅片上进行p型离子沟道注入,在此同时形成深p阱区及p型结终端拓展区;s3、在碳化硅晶片上淀积sio2氧化层,在氧化层上布设光刻胶并刻蚀深jfet区开孔;在碳化硅片上进行n型离子沟道注入,在此同时形成深jfet区;s4、在碳化硅片上淀积sio2氧化层,在氧化层上布设光刻胶并刻蚀p+体区开孔,在碳化硅片上进行p型离子注入,在此同时形成p+体区;s5、在碳化硅片上淀积sio2氧化层,在氧化层上布设光刻胶并刻蚀n+源区及n+场限环开孔,在碳化硅片上进行n型离子注入,在此同时形成n+源区及n+场限环;s6、在碳化硅片上淀积栅介质层和钝化层并刻蚀出沟槽开孔并刻蚀出刻蚀沟槽;在刻蚀沟槽中填充sio2后淀积栅极层、源极金属、漏极金属。

5、可以发现,以上方案,本发明通过随机注入和沟道注入两步形成深p阱区,一方面可以增强器件的抗短路能力,另一方面这种深结结构更适合结合本发明提出的沟槽n+场限环嵌入p型结终端拓展区的复合终端结构,在器件处于反向阻断状态时,器件元胞区的pn结和终端结构同时承受耐压,提高器件反向击穿电压,从而使器件更具有可靠性。本器件元胞区和终端区的结合设计不会对器件的导通电阻有负面影响。同时采用沟道注入方式,且使用低能量形成深结,这对于所发明的mosfet结构实现较强的耐短路能力,该结构结合p型结终端拓展区终端技术,可以使器件电场分布更均匀,提高器件耐压能力。传统的p型结终端拓展区结构性能依赖于p型结终端拓展区区的浓度,控制合适浓度的p型结终端拓展区才能使终端区的耗尽层得到充分拓展。本发明将n+场限环内嵌在p型结终端拓展区中而且同时n+场限环增加刻蚀沟槽,n型n+场限环和沟槽结构可以对结终端拓展区进行电荷调制,从而使表面峰值电场强度降低,可使n+场限环技术更稳定,同时解决了表面电场强度过高引起的sio2容易损坏的问题并降低了器件击穿电压对p型结终端拓展区区浓度的敏感性,只是需要附加一次沟槽刻蚀,且沟槽的刻蚀可以采用与n+场限环注入完全相同的掩膜。这种刻蚀沟槽n+场限环嵌入p型结终端拓展区的终端结构更适合深结器件。

技术特征:

1.一种用于sic功率器件的复合终端结构,其特征在于,包括形成于n型重掺杂衬底上的n-漂移区,所述n-漂移区之上依次设有器件元胞区和器件终端区;所述器件元胞区包括间隔设置的深p阱区,以及深p阱区与所述n-漂移区形成的pn结组成主结;

2.如权利要求1所述的一种用于sic功率器件的复合终端结构,其特征在于,所述p型结终端拓展区的深度与深p阱区的深度相同。

3.如权利要求1所述的一种用于sic功率器件的复合终端结构,其特征在于,所述n+场限环的深度小于p型结终端拓展区的深度。

4.如权利要求1所述的一种用于sic功率器件的复合终端结构,其特征在于,所述刻蚀沟槽的沟槽截面形状为矩形、梯形、v形、台阶形或u形中的一种或多种。

5.如权利要求1所述的一种用于sic功率器件的复合终端结构,其特征在于,

6.如权利要求5所述的一种用于sic功率器件的复合终端结构,其特征在于,所述栅介质材料为sio2、al2o3、aln、hfo2、ga2o3、mgo、sinx、sc2o3材料中的一种或任意几种的组合。

7.制备如权利要求1-6任一项所述的一种用于sic功率器件的复合终端结构的方法,其特征在于,所述方法包括:

8.如权利要求7所述的制备一种用于sic功率器件的复合终端结构的方法,其特征在于,所述s1-s5中在离子注入p型离子可选al或b,注入的n型离子可选n或p或as;所述s2、s3中沟道注入时,注入离子的半径小于原子排之间敞开的距离,注入方向沿着敞开的晶方向。

9.如权利要求7所述的制备一种用于sic功率器件的复合终端结构的方法,其特征在于,所述s1是注入离子的掺杂浓度为1e18~5e19cm-3之间,注入能量在350kev~960kev之间,深度在0.5~1μm之间;所述s4、s5注入离子浓度大于1e19cm-3,深度在0.3~0.5μm之间。

10.如权利要求7所述的制备一种用于sic功率器件的复合终端结构的方法,其特征在于,所述栅介质层厚度为200-300nm之间,钝化层材料为sin或si3n4或sioxny,其厚度为3-6μm。

技术总结

本发明公开了一种用于SiC功率器件的复合终端结构及其制造方法。其中,所述结构包括:形成于N型重掺杂衬底上的N‑漂移区,N‑漂移区上依次设有器件元胞区和器件终端区;器件元胞区包括间隔设置的深P阱区,以及深P阱区与N‑漂移区形成的PN结组成主结;器件终端区包括:P型结终端拓展区、钝化层;该P型结终端拓展区靠近主结一侧间隔设置有若干N+场限环;P型结终端拓展区表面淀积有钝化层,N+场限环远离N‑漂移区一侧设置有刻蚀沟槽。本发明可以增强器件的抗短路能力,在器件处于反向阻断状态时,器件元胞区的PN结和终端结构同时承受耐压,提高器件反向击穿电压,从而使器件更具有可靠性。

技术研发人员:杨伟锋,冶晓峰,王懿锋,王鑫炜

受保护的技术使用者:厦门大学

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!