显示面板及显示装置的制作方法

1.本公开涉及显示技术领域,尤其涉及一种显示面板及显示装置。

背景技术:

2.随着显示技术的发展,有机发光二极管(organic light-emitting diode,简称oled)显示面板以其自发光、视角广、对比度高、响应速度快、耗电低、超轻薄等特点,受到了广泛应用。

3.oled显示面板采用有机材料。而有机材料在有水汽和氧存在的条件下,都会发生不可逆的光氧化反应。另外,水、氧对铝、镁或银等电极材料也有很强的侵蚀作用,显示面板对水、氧的阻隔效果将直接影响显示面板的可靠性和使用寿命。如何提升显示面板的封装效果,是oled显示面板急需解决的问题。

技术实现要素:

4.本公开的实施例提供了一种显示面板及显示装置,能够提升显示面板的封装性能,降低显示装置发生封装失效的风险。

5.一方面,提供一种显示面板。所述显示面板具有显示区和围绕所述显示区的周边区。所述显示面板包括衬底、第一金属层、平坦化层和挡墙结构。第一金属层设置于所述衬底上,且所述第一金属层包括位于所述周边区的信号线图案。平坦化层设置于所述第一金属层远离所述衬底的一侧,且所述平坦化层在所述周边区设有开口。挡墙结构位于所述周边区,且围绕所述显示区。所述挡墙结构的至少部分位于所述开口内。其中,所述信号线图案设有至少一个通孔,所述至少一个通孔在所述衬底上的正投影位于所述开口在所述衬底上的正投影内,且位于所述挡墙结构在所述衬底上的正投影靠近所述显示区的一侧和/或远离所述显示区的一侧。

6.本公开实施例提供的显示面板,第一金属层包括位于周边区的通孔,且通孔位于平坦化层的开口内,这样,通孔可以增加第一金属层的侧壁面积。这样,在后续形成平坦化层(形成开口)的过程中,可以减少第一金属层的 (侧壁)单位面积上的接触的显影液的量,达到分担显影液、降低显影液负载效应的效果,进而减少显影液对第一金属层的侵蚀作用,减小第一金属层侧壁形成凹槽(undercut)的风险,并降低形成凹槽的深度。这样,有利于提升显示面板的封装性能。

7.在一些实施例中,所述信号线图案设有多个通孔,所述多个通孔排列成至少一排,一排的多个通孔沿位于所述开口内的挡墙结构的延伸方向间隔分布。

8.在一些实施例中,所述挡墙结构靠近所述显示区的一侧设置有至少一排所述通孔;和/或,所述挡墙结构远离所述显示区的一侧设置有至少一排所述通孔。

9.在一些实施例中,所述多个通孔排列成多排,沿垂直于一排通孔的排列方向的方向,任意相邻两排通孔之间间隔分布。

10.在一些实施例中,所述开口包括相对的第一边界和第二边界,所述第一边界位于

所述挡墙结构靠近所述显示区的一侧,所述第二边界位于所述挡墙结构远离所述显示区的一侧。所述挡墙结构与所述第一边界之间设置有至少一个所述通孔。所述挡墙结构与所述第二边界之间设置有至少一个所述通孔。

11.在一些实施例中,所述挡墙结构与所述第一边界之间的间距,小于所述挡墙结构与所述第二边界之间的间距。

12.在一些实施例中,所述开口包括第一边界,所述第一边界位于所述挡墙结构靠近所述显示区的一侧。所述挡墙结构与所述第一边界之间设置有至少一个所述通孔,至少一个所述通孔与所述挡墙结构之间的间距为11μm ~40μm。

13.在一些实施例中,所述开口包括第二边界,所述第二边界位于所述挡墙结构远离所述显示区的一侧。所述挡墙结构与所述第二边界之间设置有至少一个所述通孔,至少一个所述通孔与所述挡墙结构之间的间距为11μm ~75μm。

14.在一些实施例中,所述开口包括第一边界和第二边界,所述第一边界位于所述挡墙结构靠近所述显示区的一侧,所述第二边界位于所述挡墙结构远离所述显示区的一侧。所述挡墙结构与所述第一边界之间设置有至少一个所述通孔,所述通孔到所述第一边界的最小间距,大致等于所述通孔到所述挡墙结构的最小间距;和/或,所述挡墙结构与所述第二边界之间设置有至少一个所述通孔,所述通孔到所述第二边界的最小间距,大致等于所述通孔到所述挡墙结构的最小间距。

15.在一些实施例中,所述通孔在所述衬底上的正投影的形状为圆形或矩形。

16.在一些实施例中,一个所述通孔的侧壁的面积为40μm2~100μm2。

17.在一些实施例中,至少一个所述通孔的侧壁包括凹槽,所述凹槽的底壁大致为弧形,所述底壁的最低点与通孔侧壁的最大距离与所述通孔的数量负相关。

18.在一些实施例中,所述开口包括相对的第一边界和第二边界,所述第一边界位于所述挡墙结构靠近所述显示区的一侧,所述第二边界位于所述挡墙结构远离所述显示区的一侧。所述挡墙结构与所述第一边界之间设置有第一通孔,所述挡墙结构与所述第二边界之间设置有第二通孔。所述第一通孔的数量小于所述第二通孔的数量,且所述第一通孔的侧壁的凹槽的平均深度,小于所述第二通孔的侧壁的凹槽的平均深度;或者,所述第二通孔的数量小于所述第一通孔的数量,且所述第二通孔的侧壁的凹槽的平均深度,小于所述第一通孔的侧壁的凹槽的平均深度;或者,所述第一通孔的数量等于所述第二通孔的数量,且所述第一通孔的侧壁的凹槽的平均深度,大致等于所述第二通孔的侧壁的凹槽的平均深度。

19.在一些实施例中,至少一个所述通孔的侧壁包括凹槽;所述通孔数量越多,所述每个通孔的平均深度越小或凹槽凹陷的平均深度越小。

20.在一些实施例中,所述第一金属层包括至少一条电压信号线,所述至少一条电压信号线的部分设置于所述周边区,且位于所述至少一个开口内,所述通孔设置于所述至少一条信号线中位于所述周边区且位于所述至少一个开口内的部分。

21.在一些实施例中,所述周边区包括位于所述显示区一侧的扇出区,及位于所述扇出区远离所述显示区一侧的绑定区。所述至少一条电压信号线包括第一电压信号线和第二电压信号线。所述第一电压信号线包括设置于所述显示区的多条第一子线,位于所述扇出区第一总线,及由所述扇出区延伸至所述绑定区的第一连接线;所述多条第一子线靠近所

述扇出区的一端均与所述第一总线电连接,所述第一总线与所述第一连接线电连接。所述第二电压信号线包括设置于所述周边区且至少部分围绕所述显示区的第二子线,位于所述扇出区的第二总线,及由所述扇出区延伸至所述绑定区的第二连接线;所述第二子线的两端延伸至所述扇出区,并与所述第二总线电连接,所述第二总线与所述第一连接线电连接。其中,所述第一总线和所述第二总线沿第一方向延伸,所述第一方向为所述扇出区所在的显示区侧边的延伸方向;所述信号线图案包括所述第一总线和所述第二总线,所述至少一个通孔设置于所述第一总线和/或所述第二总线上。

22.在一些实施例中,所述第一总线上设有多个通孔,且所述多个通孔沿所述第一方向排列成一排。

23.在一些实施例中,所述第二电压信号线包括两条第二总线,两条第二总线分别位于所述扇出区的两侧;每条第二总线与延伸至所述扇出区同侧的第二子线的端部电连接。至少一条第二总线上设有多个通孔,且所述多个通孔沿所述第一方向排列成一排。

24.在一些实施例中,所述第一金属层包括层叠设置的金属钛层、金属铝层和金属钛层。

25.在一些实施例中,所述挡墙结构包括间隔设置的第一挡墙和第二挡墙,所述第一挡墙相较于所述第二挡墙靠近所述显示区。所述至少一个通孔设置于所述第一挡墙靠近所述显示区的一侧,和/或,所述至少一个通孔设置于所述第二挡墙远离所述显示区的一侧。

26.在一些实施例中,所述第一挡墙和所述第二挡墙均包括垫块,所述垫块位于所述平坦化层。

27.另一方面,提供一种显示装置。所述显示装置包括:如上述任一实施例所述的显示面板。

28.可以理解地,本公开的上述实施例提供的显示装置,其所能达到的有益效果可参考上文中显示面板的有益效果,此处不再赘述。

附图说明

29.为了更清楚地说明本公开中的技术方案,下面将对本公开一些实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例的附图,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。此外,以下描述中的附图可以视作示意图,并非对本公开实施例所涉及的产品的实际尺寸、方法的实际流程、信号的实际时序等的限制。

30.图1为根据一些实施例的显示面板的结构图;

31.图2a为图1中沿剖面线a-a的一种结构示意图;

32.图2b为图1中沿剖面线a-a的另一种结构示意图;

33.图3a为根据一些实施例的第一金属层的一种结构图;

34.图3b为根据一些实施例的第一金属层的另一种结构图;

35.图4为根据一些实施例的像素驱动电路的等效电路图;

36.图5a为根据一些实施例的触控功能层的平面结构图;

37.图5b为沿图5a中剖面线d-d的一种截面图;

38.图6为图3b中沿剖面线c-c的一种结构示意图;

39.图7为相关技术中信号线图案侧壁形成凹槽的一种结构图;

40.图8为根据一些实施例的阵列基板的一种结构图;

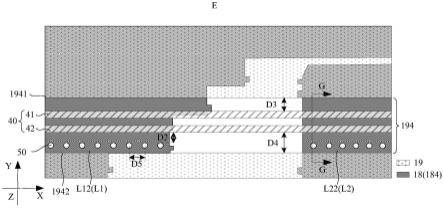

41.图9a为图8中e的一种局部放大图;

42.图9b为沿图9a中剖面线f-f的截面图;

43.图10a为图8中e的另一种局部放大图;

44.图10b为沿图10a中剖面线g-g的截面图;

45.图11a为图8中e的又一种局部放大图;

46.图11b为沿图11a中剖面线h-h的截面图;

47.图11c为图11b中i的局部放大图;

48.图12为根据一些实施例的通孔设置位置的示意图;

49.图13为根据一些实施例的通孔侧壁的凹槽的结构图;

50.图14为图1中沿剖面线b-b的一种结构示意图;

51.图15a为图8中e的又一种局部放大图;

52.图15b为图8中e的又一种局部放大图;

53.图15c为图8中e的又一种局部放大图;

54.图16a为根据一些实施例的阵列基板的另一种结构图;

55.图16b为图16a中m的一种局部放大图;

56.图17a为根据一些实施例的阵列基板的又一种结构图;

57.图17b为图17a中n的一种局部放大图;

58.图18a~18d为根据一些实施例的显示面板的制作步骤图。

具体实施方式

59.下面将结合附图,对本公开一些实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本公开一部分实施例,而不是全部的实施例。基于本公开所提供的实施例,本领域普通技术人员所获得的所有其他实施例,都属于本公开保护的范围。

60.除非上下文另有要求,否则,在整个说明书和权利要求书中,术语“包括(comprise)”及其其他形式例如第三人称单数形式“包括(comprises)”和现在分词形式“包括(comprising)”被解释为开放、包含的意思,即为“包含,但不限于”。在说明书的描述中,术语“一个实施例(one embodiment)”、“一些实施例(some embodiments)”、“示例性实施例(exemplaryembodiments)”、“示例(example)”或“一些示例(some examples)”等旨在表明与该实施例或示例相关的特定特征、结构、材料或特性包括在本公开的至少一个实施例或示例中。上述术语的示意性表示不一定是指同一实施例或示例。此外,所述的特定特征、结构、材料或特点可以以任何适当方式包括在任何一个或多个实施例或示例中。

61.以下,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本公开实施例的描述中,除非另有说明,“多个”的含义是两个或两个以上。

[0062]“a和/或b”,包括以下三种组合:仅a,仅b,及a和b的组合。

[0063]

本文中“适用于”或“被配置为”的使用意味着开放和包容性的语言,其不排除适用

于或被配置为执行额外任务或步骤的设备。

[0064]

如本文所使用的那样,“约”、“大致”或“近似”包括所阐述的值以及处于特定值的可接受偏差范围内的平均值,其中所述可接受偏差范围如由本领域普通技术人员考虑到正在讨论的测量以及与特定量的测量相关的误差 (即,测量系统的局限性)所确定。

[0065]

本文参照作为理想化示例性附图的剖视图和/或平面图描述了示例性实施方式。在附图中,为了清楚,放大了层和区域的厚度。因此,可设想到由于例如制造技术和/或公差引起的相对于附图的形状的变动。因此,示例性实施方式不应解释为局限于本文示出的区域的形状,而是包括因例如制造而引起的形状偏差。例如,示为矩形的蚀刻区域通常将具有弯曲的特征。因此,附图中所示的区域本质上是示意性的,且它们的形状并非旨在示出设备的区域的实际形状,并且并非旨在限制示例性实施方式的范围。

[0066]

本公开的一些实施例提供了一种显示装置1000,参阅图1,该显示装置 1000可以为电视机、笔记本电脑、平板电脑、手机、个人数字助理(英文: personal digital assistant;简称:pda)、导航仪、可穿戴设备、增强现实(英文:augmented reality;简称:ar)设备、虚拟现实(英文:virtual reality;简称:vr)设备等任何具有显示功能的产品或者部件。

[0067]

显示装置包括显示面板100。显示面板100具有显示区101和围绕显示区 101的周边区102。周边区102中包括位于显示区101其中一侧的扇出区1021 和绑定区1022,且绑定区1022位于扇出区1021远离显示区101的一侧。

[0068]

需要理解的是,在一些实施例中,周边区102也可以仅位于显示区101 的一侧或多侧,本公开的实施例对此不作具体限定。

[0069]

其中,显示区101包括多个子像素,每个子像素包括位于衬底11上的像素驱动电路110和与该像素驱动电路110电连接的发光器件20。周边区102 包括多条信号线和ic(integrated circuit)芯片等,其中,ic芯片设置于周边区102中的绑定区1022。

[0070]

参阅图2a和图2b,显示面板100包括层叠设置的阵列基板10、发光器件20和封装层30。其中,阵列基板10包括衬底11。

[0071]

参阅图2a,阵列基板10还包括依次设置于衬底11上的半导体层12、第一栅介质层13、第一栅极层14、第二栅介质层15、第二栅极层16、层间介质层171、第一源漏金属层181、钝化层172、第一平坦化层191、第二源漏金属层182和第二平坦化层192。

[0072]

或者,参阅图2b,阵列基板10还包括依次设置于衬底11上的半导体层 12、第一栅介质层13、第一栅极层14、第二栅介质层15、第二栅极层16、层间介质层171、第三源漏金属层183、钝化层172和第三平坦化层193。

[0073]

本公开的一种实施例中,第一金属层18包括距衬底11最远的一层源漏金属层,即图2a中的第二源漏金属层182,或图2b中的第三第一金属层183。

[0074]

本公开的另一种实施例中,第一金属层18包括衬底11上的多层金属层中的至少一层金属层。比如,第一金属层18包括图2a中第一栅极层14、第二栅极层16、第一源漏金属层181和第二源漏金属层182中的一个或多个。

[0075]

本公开的一种实施例中,平坦化层19包括距衬底11最远的一层平坦化层(第一金属层18远离衬底11一侧的平坦化层),即图2a中的第二平坦化层192,或图2b中的第三平坦化层193。

[0076]

本公开的另一种实施例中,平坦化层19包括距衬底11上的至少一层平坦化层,即图2a中的第一平坦化层191和/或第二平坦化层192;或者图2b 中的第三平坦化层193。

[0077]

本公开的实施例中,以图2a所示显示面板100为例,对申请的内容进行示例性描述。

[0078]

其中,像素驱动电路110包括多个薄膜晶体管(thin film transistor,简称 tft)和至少一个电容器cst(图中仅示例性地展示了一个tft和一个电容器 cst)。比如,像素驱动电路110可以为“7t1c”电路、“7t2c”电路、或“3t1c”电路等,本公开的实施例对像素驱动电路110的结构不做具体限定。“t”是指薄膜晶体管,“t”前面的数字是指薄膜晶体管的数量;“c”是指电容器 cst,“c”前面的数字是指电容器cst的数量。

[0079]

示例性地,参阅图4,像素驱动电路110可以为“7t1c”电路。这样,像素驱动电路110包括第一初始化晶体管t1、第二初始化晶体管t2、驱动晶体管t3、数据写入晶体管t4、补偿晶体管t5、第一发光控制晶体管t6、第二发光控制晶体管t7以及电容器cst。

[0080]

其中,第一初始化晶体管t1被配置为在第一扫描线gl1的控制下,向驱动晶体管t3的控制极提供初始化信号。第二初始化晶体管t2被配置为在第一扫描线gl1的控制下,向发光器件20的阳极(图4中发光器件20的上端)提供初始化信号。数据写入晶体管t4和补偿晶体管t5被配置为在第二扫描线gl2的控制下,向驱动晶体管t3的控制极提供数据信号。驱动晶体管t3被配置为在数据信号的控制下,控制通过发光器件20的电流大小,以调节发光器件的发光亮度。第一发光控制晶体管t6、第二发光控制晶体管t7被配置为在使能信号线em的控制下,控制发光器件 20是否发光。

[0081]

tft可以包括位于半导体层12内的半导体图案121、第一栅极层14内的栅极141、以及第一源漏导电层181内的源极18'和漏极18〞。电容器cst可以包括第一栅极层14内第一极板142以及位于第二栅极层16内的第二极板 161。

[0082]

参阅图3a,图3a为第一金属层18的部分结构图。第一金属层18包括位于周边区102的信号线图案184。参阅图6,图6为第一金属层18的截面结构图;第一金属层18包括依次层叠设置的金属钛层18a、金属铝层18b和金属钛层18c,即第一金属层18为钛-铝-钛叠层结构。金属铝层18a有利提升第一金属层18的导电性,降低第一金属层18的阻抗,金属钛层18c能够保护金属铝层18a,降低金属铝层18a被氧化或者被腐蚀的风险。其中,金属钛层18a和金属钛层18b的厚度可以相等或者不等。

[0083]

参阅图2a和图8,平坦化层19(第二平坦化层192)位于第一金属层18 (第二源漏金属层182)远离衬底11的一侧,且平坦化层19在周边区102设有开口194。平坦化层19包括有机材料,有机材料具有一定的吸水特性,开口194可以避免外界水汽沿平坦化层19入侵至显示面板100的显示区101。

[0084]

示例性地,平坦化层19在周边区102形成开口194,开口194可以为环形,且围绕显示区101设置,这样,开口194可以最大限度的切断水汽沿有机层(平坦化层19)入侵至显示面板100的显示区101的路径。

[0085]

示例性地,平坦化层19在周边区102形成开口194,开口194也可以为间断的,即,开口194围绕显示区101不连续。比如,平坦化层19包括多个开口194,多个开口194围绕显示区101设置,且任意相邻两个开口194之间具有间隔。

[0086]

示例性地,开口194在周边区102的拐角处可以为弧形结构也可以为直角结构。

[0087]

示例性地,开口194在各个位置处的宽度(沿平行于显示面板100所在平面且垂直于开口194延伸方向的尺寸)可以相同或者不同。

[0088]

本公开的实施例对开口194的结构(位置、形状和大小等)不做具体限定。

[0089]

参阅图2a,发光器件20包括沿垂直于衬底11且远离衬底11的方向,依次设置于平坦化层19上的阳极层21、像素界定层22、发光层23、隔垫物层 24以及阴极层25。

[0090]

其中,阳极层21包括多个相互分离的阳极211(图2a中仅示例性地展示出一个阳极211)。像素界定层22具有多个第一开口221,每个第一开口221 暴露一个阳极221的至少部分区域。

[0091]

发光层23包括多个发光图案231,每个发光图案231的至少部分位于一个第一开口221内。发光层23可以包括电子传输层(election transporting layer,简称etl)、电子注入层(election injection layer,简称eil)、空穴传输层(holetransporting layer,简称htl)以及空穴注入层(hole injection layer,简称hil) 中的一层或多层。

[0092]

隔垫物层24包括多个隔垫物241,隔垫物241用于支撑蒸镀工艺中的掩膜板。阴极层24可以为整层结构。阴极层25的材料可以为透明导电材料,比如氧化铟锡(indium tin oxides;简称ito)。一个发光器件20包括一个阳极221、位于该阳极221上的发光图案231、以及与发光图案231接触的阴极层25的部分。

[0093]

封装层30设置于阴极层25远离衬底10的一侧。封装层30被配置为隔绝水氧对发光器件20的侵蚀。示例性地,封装层30可以包括依次层叠的第一无机层31、有机封装层32和第二无机层33。第一无机层31和第二无机层 33被配置为阻隔外界的水氧,有机封装层32被配置为进行膜层内的应力释放和平坦化。

[0094]

在一些实施例中,显示面板100还可以包括设置于封装层30上的触控功能层40,也就是显示面板100采用了柔性多层结构(flexible multiple layer oncell,简称fmloc)工艺。

[0095]

参阅图5a和图5b,图5a为触控功能层40的一种平面结构,图5b为触控功能层40的一种截面结构。触控功能层40可以包括沿垂直于显示面板 100且远离显示面板100的方向(第三方向z)依次设置的隔离层41、第一电极层42、第二绝缘层43、第二电极层44和绝缘覆盖层45。

[0096]

其中,隔离层41的材料可以为氮化硅(sinx)。第二绝缘层43用于阻隔第一电极层42和第二电极层44,防止两者在预期位置之外的位置发生电接触,示例性地,第二绝缘层43采用的材料也可以为氮化硅(sinx)。绝缘覆盖层 45用于保护第二电极层44,比如绝缘覆盖层45的材料可以包括聚酰亚胺树脂(polyimide,简称pi)。

[0097]

第一电极层42中包括多条桥接线421,一般采用依次层叠设置的金属钛、金属铝和金属钛,或者层叠设置的氧化铟锡(indium tin oxide,简称ito)、银和氧化铟锡制作形成,即桥接线421采用钛-铝-钛的叠层结构,或者采用 ito-银-ito叠层结构。

[0098]

第二电极层44内包括多个触控电极441和多条触控走线442,沿第二方向x(图5a中的水平方向)相邻两个触控电极441之间直接电连接,沿第三方向y(图5a中的竖直方向)相邻的两个触控电极441通过一条位于第一电极层42的一条桥接线421电连接。第二电极层44采用的材料可以与第一电极层42的材料相同。

[0099]

可以理解的是,第一电极层42和第二电极层44的位置也可以进行互换,即第一电

极层42可以包括多个触控电极441和多条触控走线442,第二电极层44包括多条桥接走线。

[0100]

相关技术中,形成平坦化层19(环形开口194)的过程,包括显影工艺。显影过程中,部分显影液会与位于开口194内的第一金属层18的侧壁接触,并且与第一金属层18中的金属铝层18b发生化学反应(2al+2oh-+2h2o=2alo

2-+3h2

↑

),进而在第一金属层18的侧壁形成凹槽 (undercut)185(如图7所示)。且在后续形成阳极层21的过程中,刻蚀液会进一步刻蚀第一金属层18中的金属铝层,进而加深凹槽185的深度h。这样,在后续通过化学气相沉积(chemical vapor deposition;简称:cvd)形成封装层30(第一无机层31和第二无机层33)的过程中,封装层30的部分材料嵌入至凹槽185内,进而导致封装层30在凹槽185的附近产生微裂纹,影响显示面板100的封装效果,增加水汽进入显示区101的风险,并容易导致发光材料发生失效,形成暗斑(该暗斑称为“bdsx不良”)。其中,如图3a 所示,在周边区102,沿第一方向x,第一电压信号线l1和第二电压信号线 l2之间的区域d成为gdsx区域。

[0101]

为了解决上述问题,本公开的一些实施例提供了一种显示面板100。参阅图8、图9a和图9b,显示面板100还包括挡墙结构40,挡墙结构40位于周边区102,且挡墙结构40的至少部分位于开口194内。开口194内的挡墙结构40在衬底11上的正投影与信号线图案184在衬底11上的正投影部分交叠,即信号线图案184的至少部分位于开口194内的挡墙结构40的下方。

[0102]

信号线图案184中设有至少一个通孔50。至少一个通孔50在衬底11上的正投影位于开口194在衬底11的正投影内,且位于挡墙结构40在衬底11 上的正投影的靠近显示区101的一侧和/或远离显示区101的一侧。

[0103]

即信号线图案184中位于开口194内的部分设有通孔50,且通孔50位于挡墙结构40靠近显示区101的一侧(如图9a和图9b所示),或者,通孔50 位于挡墙结构40远离显示区101的一侧(如图10a和图10b所示),或者,通孔50包括位于挡墙结构40靠近显示区101的一侧的部分,以及位于挡墙结构40远离显示区101的一侧的部分(如图11a和图11b所示)。

[0104]

本公开的一些实施例提供的显示面板100,第一金属层18包括位于周边区102的通孔50,且通孔50位于平坦化层19的开口194内,这样,通孔50 可以增加第一金属层18的侧壁面积。在后续形成平坦化层19(形成开口194) 的过程中,可以减少第一金属层18的(侧壁)单位面积上的接触的显影液的量,达到分担显影液、降低显影液负载效应的效果,进而减少显影液对第一金属层18的侵蚀作用,减小第一金属层18侧壁形成凹槽185(undercut)的风险,并降低形成凹槽185(如图13所示)的深度。这样,有利于降低封装层30嵌入上述凹槽185内的风险,并且降低封装层30嵌入凹槽185内材料的量,降低封装层30在凹槽185处产生微裂纹的风险,降低水汽沿上述微裂纹入侵至显示区101的风险,进而提升显示面板100的封装性能。

[0105]

参阅图12和下表1:

[0106]

表1:在不同位置处设置通孔时凹槽的深度

[0107][0108]

其中,表1中,a01和a02是指在相同位置处进行的两次对比测试。“—”是指:数字0。各个数值的单位为即10

×‑

10次方米。“内侧”是指靠近显示区101的一侧,“外侧”是指远离显示区101的一侧。

[0109]

图12中,数字1~6分别对应表1中“split1~split6”中的通孔50设置的位置。以split1为例,split1是指将通孔50设置于挡墙结构40(第二挡墙42 的中心位置)内,即图12中1的位置,信号线图案184的各个位置处的凹槽 185的深度。

[0110]

需要理解的是,上表1中,在split1处,通孔50被挡墙结构40中的平坦化层19覆盖,刻蚀形成开口194的过程中,显影液不会与通孔50的侧壁接触,因此可以将其作为空表对照组。即不设置通孔50时,源漏导电层18不同位置处的凹槽185(sd undercut)深度。可以看到,在不设置通孔50或将通孔50设置于挡墙结构40的下方时(挡墙结构40在衬底11上的正投影与通孔50在衬底11上的正投影交叠),源漏导电层18不同位置处的凹槽185 的平均深度为即0.927mm。

[0111]

由split2~split4可知,在通孔50设置在挡墙结构40远离显示区101的一侧时,源漏导电层18不同位置处的凹槽185的平均深度分别为:0.560mm、 0.434mm和0.359mm,均小于0.927mm。即,通孔50设置在挡墙结构40远离显示区101的一侧时,可以显著降低信号线图案184不同位置处的凹槽185 的平均深度。

[0112]

由split5和split6可知,孔50设置在挡墙结构40靠近显示区101的一侧时,源漏导电层18不同位置处的凹槽185的平均深度分别为:0.467mm和 0.392mm,均小于0.927mm。即,通孔50设置在挡墙结构40靠近显示区101 的一侧时,可以显著降低源漏导电层18不同位置处的凹槽185的平均深度。

[0113]

由上述内容可知,在信号线图案184上设置通孔50(通孔50在衬底11 上的正投影位于开口194在衬底11的正投影内,且位于挡墙结构40在衬底 11的正投影靠近显示区101的一侧和/或远离显示区101的一侧),能够降低信号线图案184不同位置处的凹槽185的平均深度,进而降低封装层30嵌入凹槽185内材料的量,降低封装层30在凹槽185处产生微裂纹的风险,降低水汽沿上述微裂纹入侵至显示区101的风险,进而提升显示面板100的封装

性能。

[0114]

需要理解的是,参阅表1和图13,在形成像素界定层22(pdl层)的过程中,会在上述凹槽185内残留部分pi,pi填充于凹槽185内,能够降低凹槽185的深度。即形成的凹槽185的最终的深度为侵蚀金属铝层的深度(sdundercut)减凹槽185内残留的pi的深度。

[0115]

在一些实施例中,参阅图9a和图10a,挡墙结构40包括间隔设置的第一挡墙41(dam1)和第二挡墙42(dam2)。其中,第一挡墙41相较于第二挡墙42靠近显示区101。至少一个通孔50设置与第一挡墙41靠近显示区101的一侧(如图9a所示),或者设置于第二挡墙42远离显示区101的一侧(如图10a所示)。挡墙结构40能够提升显示面板100的封装性能,降低水汽侵入显示区101的风险。

[0116]

通孔50设置于挡墙结构40靠近显示区101的一侧是指:至少一个通孔50设置于第一挡墙41靠近显示区101的一侧。通孔50设置于挡墙结构40远离显示区101的一侧是指:至少一个通孔50设置于第二挡墙42远离显示区101的一侧。也就是说,至少一个通孔50设置于第一挡墙41靠近显示区101的一侧,和/或,设置于第二挡墙42远离显示区101的一侧。

[0117]

在一些实施例中,参阅图14,挡墙结构40(第一挡墙41和/或第二挡墙42)包括层叠设置的第一垫块401、第二垫块402和第三垫块(图中未示出)中的一个或多个。其中,第一垫块401与平坦化层19材料相同且同层设置;第二垫块402与像素界定层22材料相同且同层设置;第三垫块可以与隔垫物层24材料相同且同层设置。在显示面板100包括第一平坦化层191的情况下,挡墙结构40还可以包括第四垫块404,第四垫块404与第一平坦化层191材料相同且同层设置。示例性地,参阅图14,第一挡墙41和第二挡墙42均包括第一垫块401、第二垫块402和第三垫块。且第二挡墙结构42包括第四垫块404。

[0118]

可以理解的是,在挡墙结构40包括与平坦化层19材料相同且同层设置的第一垫块401的情况下,第一垫块401将开口194分隔形成多个子开口194a。比如,参阅图9b,在第一挡墙41和第二挡墙42均包括第一垫块401的情况下,第一垫块401将开口194分隔形成三个子开口194a。三个子开口194a分别为第一边界1941与第一挡墙41之间一个子开口194a,第一挡墙41与第二挡墙42之间的一个子开口194a,以及第二挡墙42与第二边界1942之间的一个子开口194a。这样,“通孔50在衬底11上的正投影位于开口194在衬底11的正投影内”是指:通孔50在衬底11上的正投影位于子开口194a在衬底11的正投影内;即通孔50设置于第一金属层18位于开口194内且未被平坦化层19覆盖的区域。

[0119]

在一些实施例中,第一金属层18包括至少一条电压信号线,至少一条电压信号线的部分设置于周边区102,且位于至少一个开口194内,通孔50设置于至少一条信号线中位于周边区102且位于至少一个开口194内的部分(以下简称为第一部分)。这样,可以降低刻蚀液和显影液对信号线第一部分的侧壁的侵蚀,降低信号线侧壁形成的凹槽185的深度。

[0120]

示例性地,至少一条电压信号线l包括第一电压信号线(比如vdd电压信号线)和第二电压信号线(比如vss电压信号线)。示例性地,第一电压信号线l1被配置为向像素驱动电路提供vdd电压信号,第二电压信号线l2被配置为向发光器件提供vss电压信号。

[0121]

参阅图3b,图3b为第一电压信号线和第二电压信号线位于第一金属层18的部分结构。第一电压信号线l1和第二电压信号线l2的至少部分位于第一金属层18。

[0122]

示例性地,参阅图3a和图3b,第一电压信号线l1可以包括位于源漏导电层18上的多条第一子线l11、第一总线l12和第一连接线l13。多条第一子线l11位于显示区101,且沿

第一方向x并排设置,每条第一子线l11沿第二方向y延伸。第一总线l12位于扇出区1021且沿第一方向x延伸。每条第一子线l11靠近扇出区1021的一端均与第一总线l12电连接。第一连接线l13与第一总线l12电连接,且由扇出区1021延伸至绑定区1022。

[0123]

其中,第一方向x为显示区101与扇出区1021分界线的延伸方向,即图 3b中的水平方向;第二方向y与第一方向x垂直,即图3b中的竖直方向。

[0124]

示例性地,参阅图3a和图3b,第二电压信号线l2可以包括位于源漏导电层18上的第二子线l21、第二总线l22和第二连接线l23。第二子线l21 位于除绑定区1022外的周边区102,至少部分围绕显示区101。第二子线l21 的两端延伸至扇出区1021。第二总线l22位于扇出区1021,且与第二子线 l21延伸至扇出区1021端部电连接。第二连接线l23与第二总线l22电连接,且由扇出区1021延伸至绑定区1022。

[0125]

其中,第一总线l12和第二总线l22沿第一方向x延伸。

[0126]

第二电压信号线l2包括两条第二总线l22,沿第一方向x,两条第二总线l22分别位于扇出区1021的两侧;每条第二总线l22与延伸至扇出区1021 同侧的第二子线l21的端部电连接。

[0127]

示例性地,参阅图3a,第一总线l12两端部分的宽度,小于中间部分的宽度,这样,在第一总线l12的端部形成有台阶形状。第二总线l22设置于台阶处,且沿第一方向x,第二总线l22靠近台阶处的一端与第一总线l12 的部分相对设置。其中,第二总线l22与第一总线l12之间的区域称d为 gdsx区域。

[0128]

参阅图8和图9a,开口194在衬底11上的正投影,与第一总线l12和第二总线l22在衬底11上的正投影的部分重叠。信号线图案184可以包括第一电压信号线l1和第二电压信号线l2中位于扇出区1021的部分。比如,信号线图案184包括第一总线l12和第二总线l22。

[0129]

在一些实施例中,参阅图9a、图10a和图11a,信号线图案184上设置有多个通孔50。多个通孔50排列成至少一排,一排的多个通孔50沿位于开口194内的挡墙结构40的延伸方向(即第一方向x)间隔分布。多个通孔50 可以进一步增加信号线图案184(未被平坦化层19覆盖的部分)的侧壁面积,增加通孔50分担显影液负载效应的效果,降低信号线图案184上产生凹槽185 的风险和深度。多个通孔50沿第一方向x分布,有利于简化信号线图案184 的图案,降低多个通孔50的加工难度。

[0130]

在一些实施例中,在挡墙结构40靠近显示区101的一侧设置有至少一排通孔。比如,可以设置一排通孔50(如图9a所示),或者两排通孔50(如图 15a所示)。

[0131]

在一些实施例中,在挡墙结构40远离显示区101的一侧设置有至少一排通孔50。比如,可以设置一排通孔50(如图10a所示),或者两排通孔50(如图15b所示)。

[0132]

在一些实施例中,在挡墙结构40靠近显示区101的一侧设置有至少一排通孔,且在挡墙结构40远离显示区101的一侧设置有至少一排通孔50。其中,挡墙结构40两侧的通孔50的排数和每排通孔50的数量可以相等或者不等。比如,可以在挡墙结构40靠近显示区101的一侧设置一排通孔50,且在挡墙结构40远离显示区101的一侧设置两排通孔50(如图15c所示);或者,可以在挡墙结构40的两侧均设置一排通孔50(如图11a所示)。

[0133]

在一些实施例中,参阅图15c,多个通孔50排列成多排。沿垂直于一排通孔50的排列方向(第一方向x)的方向(第二方形y),任意相邻两排通孔50之间间隔分布。通过设置多排通孔50,可以增加通孔50的数量,进而增加通孔50分担显影液负载效应的效果,降低信号

线图案184上产生凹槽185 的风险和深度。其中,多排通孔50可以位于挡墙结构40的同侧,或者,位于挡墙结构40的异侧。

[0134]

示例性地,多排通孔50位于挡墙结构40的同侧,比如,多排通孔50均位于挡墙结构40远离显示区101的一侧(如图15b所示),或者,位于挡墙结构40靠近显示区101的一侧(如图15a所示)。

[0135]

示例性地,多排通孔50位于挡墙结构40的异侧。比如,多排通孔50包括两排通孔50,两排通孔50分别位于挡墙结构40的两侧(如图11a所示),或者,挡墙结构40的至少一侧(靠近或者远离显示区101的一侧)包括至少一排通孔50(如图15c所示)。

[0136]

在一些实施例中,参阅图11c,图11c为一个通孔50的剖视图。至少一个通孔50的侧壁51包括凹槽185,凹槽185的底壁1851大致为弧形。且底壁1851靠近衬底11的一端(图11c中的下端)相较于远离衬底11的一端(图 11c中的上端)靠近通孔50的中心线l0。

[0137]

底壁1851的最低点(通常为底壁1851远离衬底11的一端)与通孔50 的侧壁51(金属钛层18a的侧壁)的最大距离h2与通孔50的数量负相关。即通孔50的数量越多,通孔50分担显影液和刻蚀液的效果越好,对显影液和刻蚀液通孔50侧壁的侵蚀越小,这样,底壁1851的最低点与通孔50的侧壁51的最大距离h2之间的距离越小。反之,通孔50的数量越少,底壁1851 的最低点与通孔50的侧壁51的最大距离h2之间的距离越大。

[0138]

在一些实施例中,至少一个通孔50的侧壁51包括凹槽185。通孔50的数量越多,每个通孔50的平均深度越小或凹槽185凹陷的平均深度越小。即通孔50的数量越多,通孔50分担显影液和刻蚀液的效果越好,对显影液和刻蚀液通孔50侧壁的侵蚀越小,通孔50的平均深度越小或凹槽185凹陷的平均深度也就越小。

[0139]

示例性地,如图15c所示,开口194包括相对的第一边界1941和第二边界1942,第一边界1941位于挡墙结构40靠近显示区aa的一侧,第二边界 1942位于挡墙结构40远离显示区aa的一侧。挡墙结构40与第一边界1941 之间设置有第一通孔501,挡墙结构40与第二边界1942之间设置有第二通孔 502。

[0140]

比如,第一通孔501的数量小于第二通孔502的数量,且第一通孔501 的侧壁51的凹槽185的平均深度(深度h),小于第二通孔5 2的侧壁51的凹槽185的平均深度。

[0141]

其中,可以理解的是,第一通孔501的数量小于第二通孔502的数量,是单位面积上,第一通孔501的数量小于第二通孔502的数量;因此,也可以理解为第一通孔501的分布密度小于第二通孔502分布密度。

[0142]

凹槽185的底壁1851可能不是平整或者光滑的,因此,凹槽185的平均深度h可以理解为凹槽185的最大深度h2和最小深度h1的平均值。比如,参阅图11c,凹槽185的平均深度h可以为凹槽185的最大深度h2和最小深度h1的平均值。

[0143]

比如,第二通孔502的数量小于第一通孔501的数量,且第二通孔502 的侧壁51的凹槽185的平均深度,小于第一通孔501的侧壁51的凹槽185 的平均深度。

[0144]

比如,第一通孔501的数量等于第二通孔502的数量,且第一通孔501 的侧壁51的凹槽185的平均深度,大致等于第二通孔502的侧壁51的凹槽 185的平均深度。

[0145]

在一些实施例中,参阅图9a,开口194包括相对的第一边界1941和第二边界1942,第一边界1941位于挡墙结构40靠近显示区101的一侧,第二边界1942位于挡墙结构40远离显示区101的一侧。

[0146]

挡墙结构40(第一挡墙41)与第一边界1941之间的间距为第三间距d3,挡墙结构40(第二挡墙42)与第二边界1942之间的间距为第四间距d4,第三间距d3小于第四间距d4,这样,有利于提升显示面板100的封装性能。

[0147]

示例性地,挡墙结构40与第一边界1941之间的间距d3可以为50μm~60 μm,比如,间距d3为50μm、55μm或者60μm等。挡墙结构40与第二边界1942之间的间距d4可以为85μm~110μm,比如,间距d4为85μm、 95μm或110μm等。

[0148]

挡墙结构40与第一边界1941之间设置有至少一个通孔50,至少一个通孔50与挡墙结构40之间的最小间距为第一间距d1。挡墙结构40与第二边界1942之间设置有至少一个通孔50,至少一个通孔50与挡墙结构40之间的最小间距为第二间距d2。与第三间距d3小于第四间距d4适应的,第一间距d1小于第二间距d2,这样,有利于优化多个通孔50的空间布置。

[0149]

在一些实施例中,挡墙结构40与第一边界191之间设置有至少一个通孔 50,至少一个通孔50与挡墙结构40之间的最小间距d1为11μm~40μm,此时通孔50分担显影液负载效应的效果更好。示例性地,挡墙结构40与第一边界191之间设置的通孔50与挡墙结构40之间的最小间距d1为11μm、 16μm、21μm、36μm或者40μm等,在此不再一一列举。

[0150]

在一个特定示例中,经多次试验验证,在挡墙结构40(第一挡墙41)与第一边界191之间设置的通孔50与挡墙结构40之间的最小间距d1为16μm 时,降低凹槽185的深度的效果最优,且最终形成的凹槽185的深度大约为 0.35μm。

[0151]

示例性地,参阅上表1中split5,在第一间距d1为16μm时,最终形成的凹槽185的平均深度约为0.467μm-0.120μm=0.347μm。split6,在通孔 50与挡墙结构40之间的第一间距d1为36μm时,最终形成的凹槽185的平均深度约为0.392μm-0.000μm=0.392μm。

[0152]

在一些实施例中,挡墙结构40(第二挡墙42)与第二边界192之间设置有至少一个通孔50,至少一个通孔50与挡墙结构40之间的最小间距为第二间距d2,第二间距d2为11μm~75μm。此时通孔50分担显影液负载效应的效果更好。示例性地,挡墙结构40与第二边界192之间设置的通孔50与挡墙结构40之间的第二间距d2为11μm、16μm、36μm、51μm、56μm 或61μm等,在此不再一一列举。

[0153]

在一个特定示例中,经多次试验验证,在挡墙结构40与第二边界192之间设置的通孔50与挡墙结构40之间的第二间距d2为56μm时,降低凹槽 185的深度的效果最优,且最终形成的凹槽185的深度大约为0.35μm。

[0154]

示例性地,参阅上表1中的split3,在通孔50与挡墙结构40之间的第二间距d2为36μm时,最终形成的凹槽185的平均深度约为0.434μm-0.000 μm=0.434μm。参阅上表1中的split4,在通孔50与挡墙结构40之间的第二间距d2为56μm时,最终形成的凹槽185的深度约为0.359μm-0.000 μm=0.359μm。

[0155]

在一些实施例中,挡墙结构40与第一边界191之间设置有至少一个通孔 50,通孔50到第一边界191的最小间距,大致等于通孔50到挡墙结构40的间距(第一间隔d1)。和/或,挡墙结构40与第二边界192之间设置有至少一个通孔50,通孔50到第二边界192的间距,大致等于通孔50到挡墙结构40 的间距(第二间隔)。即通孔50和挡墙结构40之间的间隔,与通孔50和开口194的边界之间的间隔大致相等,沿第二方向y,通孔50大致位于挡墙结构40与开口194的边界之间的中部区域。

[0156]

示例性地,挡墙结构40与第一边界191之间的第三间隔d3可以为52 μm,且挡墙结

构40与第一边界191之间设置有至少一个通孔50,该通孔50 与挡墙结构40之间的第一间隔d1为16μm,通孔50沿第二方向y的尺寸可以为20μm,该通孔50与第一边界191之间的间隔为16μm。

[0157]

示例性地,挡墙结构40与第二边界192之间的第四间隔d4可以为110 μm,且挡墙结构40与第二边界192之间设置有至少一个通孔50,该通孔50 与挡墙结构40之间的第二间隔d2为56μm,通孔50沿第二方向y的尺寸可以为15μm,该通孔50与第二边界192之间的间隔为39μm。

[0158]

在一些实施例中,参阅图15a和图15c,通孔50在衬底11上的正投影的形状可以为圆形或者矩形(长方形或者正方形),这样,有利于简化通孔50 的图案,降低通孔50的制作难度。信号线图案184设置有多个通孔50时,多个通孔50在衬底11上的正投影的形状可以相同或者不同,本公开的实施例对此不作具体限定。

[0159]

示例性地,在通孔50在衬底11上的正投影的形状为圆形,且圆形的直径可以为3μm~25μm。

[0160]

示例性地,在通孔50在衬底11上的正投影的形状为矩形时,通孔50的最大边长可以为3μm~25μm。

[0161]

在一些实施例中,每个通孔50的侧壁的面积为40μm2~100μm2。通孔 50的侧壁面积太小(比如小于40μm2),此时通孔50较小,可能不利于通孔 50的图案化制作,而且不利于提升通孔50分担显影液负载的效果。通孔50 的侧壁面积太大(比如大于100μm2),此时通孔50较大,可能会影响信号线图案184的阻抗,并且降低信号线图案184的结构强度。

[0162]

示例性地,沿垂直于显示面板100的方向,源漏导电层18的厚度通常为 0.7μm~1.0μm。比如,源漏导电层18的厚度可以为0.7μm、0.8μm和1.0μm。

[0163]

比如,当通孔50在衬底11上的正投影的形状为圆形时,圆形的直径可以为20μm或者25μm等。当通孔50在衬底11上的正投影的形状为矩形时,矩形的长(沿第一方向x的尺寸)可以为20μm,宽(沿第二方向y的尺寸) 可以为15μm。通孔50的形状和大小可以根据实际需求进行选择,在此不再一一列举。

[0164]

在信号线图案184上设置有多个通孔50时,相邻两个通孔50之间的间距d5可以为1μm~20μm。比如,一排通孔50中相邻两个通孔50之间的间隔可以为1μm、10μm或20μm等。或者相邻两排通孔50之间的间隔d5 可以为1μm、10μm或20μm等。

[0165]

在一些实施例中,开口194在衬底11上的正投影,与第一总线l12和第二总线l22在衬底11上的正投影部分交叠,即第一总线l12和第二总线l22 的至少部分位于开口194内。这样,可以将通孔50设置于第一总线l12和/ 或第二总线l22上。

[0166]

示例性地,可以将至少一个通孔50设置于第一总线l12上(如图16a和图16b所示)。或者,可以将至少一个通孔50设置于第二总线l22上(如图 17a和图17b所示)。或者,可以在第一总线l12上设置至少一个通孔50,同时在第二总线l22上设置至少一个通孔50(如图8和图9a所示)。

[0167]

在一些实施例中,显示面板100为柔性显示面板,绑定区1022至少部分弯折显示区101的背侧。绑定区1022弯折过程中,沿第一方向x,绑定区1022 两侧受到的应力大于中部的应力。

[0168]

这样,参阅图16a和图16b,可以在第一总线l12上设有多个通孔50,且多个通孔50

沿第一方向x排列成一排;即仅在第一总线l12上设置通孔 50。这样,可以降低第二总线l22发生断裂或者变形的风险。

[0169]

在一些实施例中,显示面板100可以为刚性显示面板,沿第一方向x,绑定区1022各个位置受力均匀。

[0170]

这样,参阅图16a和图16b,可以在至少一条第二总线l21上设有多个通孔50,且多个通孔50沿第一方向x排列成一排。示例性地,两条第二总线l21上均设有多个通孔50,这样,可以增加通孔50的数量,进而增加通孔 50分担显影液负载效应的效果,降低信号线图案184上产生凹槽185的风险和深度。

[0171]

或者,参阅图8和图9a,可以在第一总线l12上设有多个通孔50,且多个通孔50沿第一方向x排列成一排。且同时在至少一条第二总线l21上设有多个通孔50,且多个通孔50沿第一方向x排列成一排。

[0172]

在一些实施例中,本公开的一些实施例还提供了一种显示面板100的制备方法。其中,以图2a所示显示面板100为例,显示面板100包括第一平坦化层191和第二平坦化层192(19)。参阅图18a~图18d,上述制备方法包括 s100~s400。

[0173]

s100,形成第一平坦化层191。

[0174]

第一平坦化层191包括第二开口1911。在挡墙结构40包括位于第一平坦化层191内的第四垫块404的情况下,第四垫块404将第二开口1911分隔为两个第二子开口1911a。

[0175]

s200,在第一平坦化层191远离衬底11的一侧形成第一金属层18。

[0176]

第一金属层18上包括至少一个通孔50(图18b中示例出多个通孔50),通孔50在第一平坦化层191上的正投影位于第二开口1911内。

[0177]

s300,在第一金属层18远离第一平坦化层191的一侧形成第二平坦化层 192。

[0178]

第二平坦化层192包括开口194。在第一挡墙41和第二挡墙42均包括与第二平坦化层192材料相同且同层设置的第一垫块401的情况下,第一垫块 401将开口194分隔形成多个子开口194a。子开口194a中的至少一个子开口194a暴露至少一个通孔50。即子开口194a在第一平坦化层191所在平面内的正投影,覆盖至少一个通孔50在第一平坦化层191所在平面内的正投影。

[0179]

s400,在第二平坦化层192远离第一金属层18的一侧形成像素界定层 22。

[0180]

像素界定层22包括第三开口222。在第一挡墙41和第二挡墙42均包括与像素界定层22材料相同且同层设置的第二垫块402的情况下,第二垫块402 将第三开口222分隔形成多个第三子开口222a。

[0181]

以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1