一种适用于堆栈式图像传感器芯片的金属结构的制作方法

1.本发明涉及图像传感器技术领域,具体涉及一种适用于堆栈式图像传感器芯片的金属结构。

背景技术:

2.堆栈式的cmos图像传感器,就是在背照式的cmos固体摄像器件中,将布置有像素阵列的半导体芯片(上层芯片)与用于进行信号处理的电路的半导体芯片(下层芯片)连接起来,固定配置成一个器件,如图1所示。与传统的结构相比,堆栈式的图像传感器在尺寸小、信号处理速度快、功能多样等方面均有较好的表现,因此堆栈式cmos图像传感器逐渐成为应用市场的主流。

3.堆栈式图像传感器的下层芯片具有用来供电和信号传输的金属结构,如图2所示,该金属结构由若干层金属层组成。目前,顶层金属一般采用金属铝来实现电源走线,而由于上、下两层芯片相隔很近,使得一部分铝的反射光能够到达上层芯片,最终导致拍摄的画面出现和金属铝布置相似的条纹痕迹现象。因此,需要对图像传感器的下层芯片的金属结构进行改进尽可能消除反射光对成像的影响。

技术实现要素:

4.本实用新型所要解决的技术问题是现有堆栈式图像传感器的顶层金属由于反射作用,使得部分反射光到达上层芯片,导致图像出现条纹痕迹的问题。

5.为解决上述问题,本实用新型提供一种适用于堆栈式图像传感器芯片的金属结构,该结构包括模拟模块的金属结构和数字模块的金属结构;

6.所述模拟模块的金属结构分为内部模块和top走线两个部分,其配置方式如下:

7.所述内部模块,顶层金属的宽度为a,相邻顶层金属的间距为a;次顶层金属的宽度为b,相邻次顶层金属的间距为b;其中,a+a=b+b,顶层金属层与次顶层金属层交叠配置;

8.所述top走线,顶层金属的宽度为a,相邻顶层金属的间距为a;次顶层金属的宽度为b,相邻次顶层金属的间距为b。

9.优选地,所述顶层金属的宽度0<a≤15

µ

m,所述相邻顶层金属的间距0<a≤5

µ

m,所述次顶层金属的宽度0<b≤15

µ

m,所述相邻次顶层金属的间距0<b≤5

µ

m。

10.进一步地,

11.所述顶层金属层,内部模块的边缘空隙为a/2,top走线的边缘距离为a/2;

12.所述次顶层金属层,内部模块之间不设边缘空隙,相邻模块拼接处的次顶层金属的宽度为b/2;所述top走线、内部模块相邻部分的边缘空隙均设为b/2。

13.这样的能够保证模块拼接处与模块内部的配置一致,同时保证top走线拼接处与模块内部的配置一致。

14.进一步地,所述数字模块金属结构的配置方式如下:

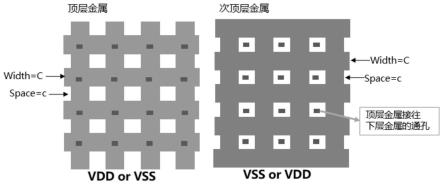

15.顶层金属与次顶层金属的宽度为c,金属带之间的间隙均为c,顶层金属呈网状配

置,次顶层金属也呈网状配置。

16.优选地,所述顶层金属与次顶层金属的宽度0<c≤15

µ

m,所述金属带之间的间隙0<c≤10

µ

m。

17.本实用新型的有益效果为:

18.1、改善图像质量。改进后的金属结构能够有效减小顶层金属反射光对成像的影响,消除条纹光影,且该结构的改进几乎不会影响芯片的特性。

19.2、本技术细密均匀的布线方式能够有效降低芯片应力分布不均的影响,提高芯片良品率。

20.3、适用性广,本技术的金属改进结构没有特定工艺要求,能广泛适用于目前市面上大部分主流工艺的设计规则。

附图说明

21.此处所说明的附图用来提供对本实用新型实施例的进一步理解,构成本技术的一部分,并不构成对本实用新型实施例的限定。在附图中:

22.图1现有堆栈式与非堆栈式图像传感器的结构示意图;

23.图2现有的图像传感器下层芯片的金属结构剖面图;

24.图3本实用新型模拟模块的顶层金属和次顶层金属的结构示意图;

25.图4本实用新型模拟模块的金属结构在改进前后的比较示意图;

26.图5本实用新型数字模块的顶层金属和次顶层金属的结构示意图。

具体实施方式

27.以下结合各个附图对实用新型提出的内容进行详细的实施说明。

28.由于顶层金属与次顶层金属之间存在一定的高度差,导致顶层金属会比次顶层金属反射更多的光。当这个高度差较大,且金属带的间距也较大时,其反射光便容易在成像中形成与顶层金属布线大致相同的明暗相间条纹,影响成像质量。

29.本实用新型提供一种新的下层芯片的金属结构,通过对金属结构中的顶层金属层和次顶层金属层的结构进行改进,从而减小由于金属的光反射作用导致的成像出现条纹的问题,具体实施方式如下。

30.堆栈式图像传感器芯片的金属结构包括模拟模块的金属结构和数字模块的金属结构,如图3、图5所示。

31.所述模拟模块的金属结构分为内部模块和top走线两个部分,其配置方式如下:

32.所述内部模块,顶层金属的宽度为a,相邻顶层金属的间距为a;次顶层金属的宽度为b,相邻次顶层金属的间距为b;其中,a+a=b+b,顶层金属层与次顶层金属层交叠配置;

33.所述top走线,顶层金属的宽度为a,相邻顶层金属的间距为a;次顶层金属的宽度为b,相邻次顶层金属的间距为b。

34.所述顶层金属的宽度0<a≤15

µ

m,所述相邻顶层金属的间距0<a≤5

µ

m,所述次顶层金属的宽度0<b≤15

µ

m,所述相邻次顶层金属的间距0<b≤5

µ

m。

35.所述顶层金属层,内部模块的边缘空隙为a/2,如模块i与模块ii的边缘空隙均为 a/2;top走线的边缘距离为a/2。这样的配置使得相邻模块的顶层金属的间距保持为a,top

走线与相邻内部模块的顶层金属的间距也保持为a。

36.所述次顶层金属层,内部模块之间不设边缘空隙,相邻模块拼接处的次顶层金属的宽度为b/2,使得模块拼接后的金属宽度与内部模块的金属宽度一致,均为b。top走线、内部模块相邻部分的边缘空隙均设为b/2,使得内部模块与top走线拼接后的空隙与金属间的空隙保持一致,均为b。

37.上述模拟模块的顶层金属和次顶层金属的结构改进,使得模块内部的金属结构细密,且保证模块拼接处与模块内部的配置保持一致,还保证了模块与top走线拼接处与模块内部的配置保持一致,改进前后的效果比较如图4所示。

38.改进后的金属结构能够有效减小顶层金属反射光对成像的影响,同时还能防止因顶层金属配置不均匀带来的应力分布不均的现象。

39.所述数字模块的金属结构的布置如图5所示,顶层金属与次顶层金属的宽度为c,金属带之间的间隙均为c,顶层金属呈网状配置,次顶层金属也呈网状配置;

40.顶层金属与次顶层金属分别为vdd/vss的电源配线。

41.所述顶层金属与次顶层金属的宽度0<c≤15

µ

m,所述金属带之间的间隙0<c≤10

µ

m。

42.这样的结构改进使得整个芯片中顶层金属和次顶层金属的配线更加均匀,能够进一步减小金属反射光对成像的影响。

43.与现有的下层芯片的金属结构相比,本技术改进后的金属结构,尤其是对下层芯片中的顶层金属结构和次顶层金属结构进行改进,使金属配线细密化,其效果是使得反射光更均匀,即使有条纹现象对成像的影响也可以忽略。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1