半导体封装装置的制作方法

1.本技术涉及半导体封装技术领域,具体涉及一种半导体封装装置。

背景技术:

2.混合键合互连(hbi,hybrid bond interconnection)技术可用于实现封装结构之间的直接键合,例如晶圆与晶圆、或芯片与芯片、或晶圆与芯片之间的直接键合。目前hbi制程中,将上、下封装结构的氧化硅(siox)先结合后,再加温进行铜垫(cu pad)之间的扩散(diffusion)结合。siox结合前,会先通过化学机械抛光(chemical mechanical polishing,cmp)来平坦化siox的对接表面,以利于分子间作用力(范德瓦尔斯力)结合。

3.参考图1,是通过cmp平坦化后封装结构40的局部截面结构示意图。如图1所示,cmp之后,封装结构40中siox 41的表面为外凸的曲面,铜垫42的表面则向内凹陷。

4.实践发现,目前cmp制程具有以下问题:

5.(1)cmp后需要满足siox 41对接表面的ra(粗糙度)小于0.5nm,条件严苛导致制程成本较高;

6.(2)cmp后,siox 41表面的曲率半径过小,结合后可能会有空洞(void)产生导致良率下降,为此需要通过多次cmp使siox 41的对接表面更平坦,曲率半径更大;

7.(3)cmp制程会导致铜垫42表面向下凹陷,产生碟形(dish)缺陷,从而不利于键合,会导致键合后铜的总电阻增大甚至连接中断。

技术实现要素:

8.本技术提出了一种半导体封装装置,以有助于解决hbi制程中cmp平坦化所导致的制程成本高,siox的对接表面会产生空洞,铜垫会产生碟形缺陷不利于结合等问题。

9.第一方面,本技术提供一种半导体封装装置,包括:第一电子元件,具有第一对接面,所述第一对接面包括第一导电垫;第二电子元件,具有第二对接面,所述第二对接面包括第二导电垫;其中,所述第一对接面与所述第二对接面结合,所述第一导电垫直接键合至所述第二导电垫,所述第一导电垫的宽度往所述第二导电垫方向渐缩,所述第二导电垫的宽度往所述第一导电垫的方向渐增。

10.在一些可选的实施方式中,所述第一对接面进一步包括粘着层,所述粘着层粘合于所述第二对接面。

11.在一些可选的实施方式中,所述粘着层不包括氧化层。

12.在一些可选的实施方式中,所述粘着层与所述第二对接面的结合介面与所述第一导电垫的上表面平齐。

13.在一些可选的实施方式中,所述粘着层包覆所述第一导电垫,所述第一导电垫的上表面露出于所述粘着层。

14.在一些可选的实施方式中,所述第一导电垫的侧壁直接接触所述粘着层。

15.在一些可选的实施方式中,所述第一电子元件包括重布线层和强化层,所述第一

导电垫位于所述重布线层上,所述重布线层位于所述强化层上。

16.在一些可选的实施方式中,所述第一电子元件包括重布线层和埋孔,所述第一导电垫位于所述重布线层上,所述埋孔连接于所述第一导电垫和所述重布线层之间,所述埋孔的孔径往所述第一导电垫的方向渐缩。

17.在一些可选的实施方式中,所述第一电子元件进一步包括种子层,所述种子层位于所述第一导电垫的下表面和所述埋孔的上表面之间。

18.在一些可选的实施方式中,所述第一电子元件进一步包括粘着层,所述粘着层粘合于所述第二对接面,所述第一导电垫和所述埋孔位于所述粘着层内。

19.在一些可选的实施方式中,所述第二对接面进一步包括氧化层,所述第二导电垫位于所述氧化层中,所述第二导电垫的下表面露出于所述氧化层。

20.在一些可选的实施方式中,所述氧化层包括氧化硅。

21.第二方面,本技术提供一种半导体封装装置的制造方法,包括:提供一载板,并形成第一导电垫于所述载板上;形成一粘着层于所述载板上,所述粘着层包覆所述第一导电垫;去除所述载板,以暴露出所述第一导电垫的上表面;将所述粘着层粘合于一电子元件,以及将所述第一导电垫的上表面直接键合至所述电子元件。

22.在一些可选的实施方式中,在形成第一导电垫于所述载板上之前,所述方法进一步包括:形成一种子层于所述载板上;在去除所述载板之后,所述方法进一步包括:将所述种子层蚀刻去除。

23.在一些可选的实施方式中,将所述第一导电垫的上表面直接键合至一电子元件包括:利用第一温度将所述粘着层附着于所述电子元件上,利用第二温度将所述第一导电垫的上表面直接键合至所述电子元件,其中,所述第一温度小于所述第二温度。

24.在一些可选的实施方式中,所述第一温度使所述粘着层软化,所述第二温度使所述第一导电垫扩散结合至所述电子元件。

25.在一些可选的实施方式中,所述形成一粘着层于所述载板上包括:通过旋转镀膜制程在所述载板上形成一粘着层。

26.为了解决hbi制程中cmp平坦化所导致的制程成本高,siox的对接表面会产生空洞,铜垫会产生碟形缺陷不利于结合等问题,本技术提出了一种半导体封装装置。本技术的半导体封装装置,将第一电子元件的第一对接面与第二电子元件的第二对接面结合,并将第一对接面的第一导电垫与第二对接面的第二导电垫直接键合,这里第一导电垫具有宽度往第二导电垫方向渐缩的特征,意味着第一电子元件的第一对接面是在一载板上形成的,不具有研磨表面。通过使用具有较为平坦表面的载板(例如玻璃载板),可以使第一对接面相对较为平坦,从而不需要cmp平坦化制程。通过在hmi制程中省掉cmp,可以解决因cmp所导致的诸多问题,有利于降低制程成本,避免对接表面产生空洞,避免导电垫产生碟形缺陷,提高导电垫之间的结合力,从而提高hbi制程的良率和产品的可靠性。

附图说明

27.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本技术的其它特征、目的和优点将会变得更明显:

28.图1是目前的一种封装结构通过cmp平坦化后的局部纵向截面结构示意图;

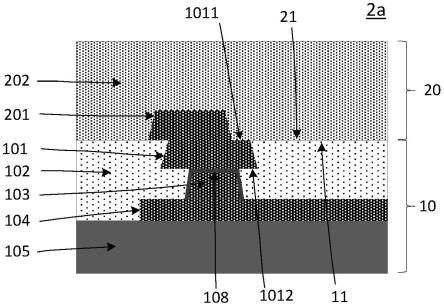

29.图2是根据本技术的半导体封装装置的一个实施例2a的纵向截面结构示意图;

30.图3a-3i是本技术的半导体封装装置的一个实施例的制造步骤的示意图;

31.图4a-4l是本技术的半导体封装装置的另一个实施例的制造步骤的示意图。

32.附图标记/符号说明:

33.10-第一电子元件;11-第一对接面;101-第一导电垫;1011-上表面;1012-下表面;102-粘着层;103-埋孔;104-重布线层;105-强化层;106-导电柱;107-胶粘层;108-第一种子层;110-第二种子层;20-第二电子元件;21-第二对接面;201-第二导电垫;202-氧化层;203-模封层;31-第一载板;32-第二载板;40-封装结构;41-siox;42-铜垫。

具体实施方式

34.下面结合附图和实施例对说明本技术的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本技术所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外,为了便于描述,附图中仅示出了与有关发明相关的部分。

35.应容易理解,本技术中的“在...上”、“在...之上”和“在...上面”的含义应该以最广义的方式解释,使得“在...上”不仅意味着“直接在某物上”,而且还意味着包括存在两者之间的中间部件或层的“在某物上”。

36.此外,为了便于描述,本文中可能使用诸如“在...下面”、“在...之下”、“下部”、“在...之上”、“上部”等空间相对术语来描述一个元件或部件与附图中所示的另一元件或部件的关系。除了在图中描述的方位之外,空间相对术语还意图涵盖装置在使用或操作中的不同方位。设备可以以其他方式定向(旋转90

°

或以其他定向),并且在本文中使用的空间相对描述语可以被同样地相应地解释。

37.本文中所使用的术语“层”是指包括具有一定厚度的区域的材料部分。层可以在整个下层或上层结构上延伸,或者可以具有小于下层或上层结构的范围的程度。此外,层可以是均质或不均质连续结构的区域,其厚度小于连续结构的厚度。例如,层可以位于连续结构的顶表面和底表面之间或在其之间的任何一对水平平面之间。层可以水平地、垂直地和/或沿着锥形表面延伸。基板(substrate)可以是一层,可以在其中包括一个或多个层,和/或可以在其上、之上和/或之下具有一个或多个层。一层可以包括多层。例如,半导体层可以包括一个或多个掺杂或未掺杂的半导体层,并且可以具有相同或不同的材料。

38.本文中使用的术语“基板(substrate)”是指在其上添加后续材料层的材料。基板本身可以被图案化。添加到基板顶部的材料可以被图案化或可以保持未图案化。此外,基板可以包括各种各样的半导体材料,诸如硅、碳化硅、氮化镓、锗、砷化镓、磷化铟等。可替选地,基板可以由非导电材料制成,诸如玻璃、塑料或蓝宝石晶片等。进一步可替选地,基板可以具有在其中形成的半导体装置或电路。

39.需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本技术可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本技术所能产生的功效及所能达成的目的下,均应仍落在本技术所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述

的明了,而非用以限定本技术可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本技术可实施的范畴。

40.还需要说明的是,本技术的实施例对应的纵向截面可以为对应前视图方向截面,横向截面可以为对应右视图方向截面,水平截面可以为对应上视图方向截面。

41.另外,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。

42.参考图2,图2是根据本技术的半导体封装装置的一个实施例2a的纵向截面结构示意图。如图2所示,本技术的半导体封装装置2a包括:

43.第一电子元件10,具有第一对接面11,第一对接面11包括第一导电垫101;

44.第二电子元件20,具有第二对接面21,第二对接面21包括第二导电垫201;

45.其中,第一对接面11与第二对接面21结合,第一导电垫101直接键合至第二导电垫201,第一导电垫101的宽度往第二导电垫201方向渐缩,第二导电垫201的宽度往第一导电垫101的方向渐增。

46.这里,第一电子元件10例如为晶圆(wafer)或者芯片(chip、die)或基板(substrate)。第二电子元件20例如为晶圆或者芯片或基板。第一电子元件10和第二电子元件20通过混合键合互连(hbi)技术直接键合,其中,第一对接面11与第二对接面21直接结合,第一导电垫101与第二导电垫201直接键合。

47.目前的hbi技术中,电子元件的对接表面,例如第二电子元件20的第二对接面21,通常包括两种材料,一种是导电材料,例如金属材质的第二导电垫201,另一种是不导电材料例如氧化层202,氧化层202具体可以是siox。在制程上,一般是通过在氧化层202上开孔再电镀形成第二导电垫201,因此,第二导电垫201在宽度上具有下窄上宽的特征,即,第二导电垫201的宽度往第一导电垫101的方向渐增。

48.考虑到hbi制程对电子元件的对接表面的平坦化的要求,本技术实施例中,可以在一具有平坦表面的载板上形成第一电子元件10的第一对接面11。参考图3d和3e,可以先在第一载板31的平坦表面上形成第一导电垫101,然后再形成第一电子元件10的其它材料层,从而在第一载板31表面形成第一电子元件10的第一对接面11,然后再去除第一载板31使第一对接面11露出。其中,第一载板31例如可以是具有较为平坦表面的玻璃载板。参考图2、图3d和3e,这里,第一对接面11由于是在具有平坦表面的第一载板31上形成,因此具有较为平坦的表面,可以直接用于对接第二电子元件20的第二对接面21,而不需要cmp(化学机械抛光)。这里,第一对接面11的第一导电垫101由于是在第一载板31上形成,因而在宽度上具有越靠近第一载板31越宽的特征,即,在第一导电垫101与第二导电垫201键合后,第一导电垫101的宽度往第二导电垫201方向渐缩。为便于描述,本技术定义第一导电垫101的面向第二导电垫201的一面为上表面1011,与上表面1011相对的一面为下表面1012,上表面1011的宽度小于下表面1012的宽度。

49.在一些可选的实施方式中,第一对接面11进一步包括粘着层102,粘着层102粘合于第二对接面21。参考图3d和3e,第一电子元件10在制程上,可以是先在第一载板31表面形成第一导电垫101后,再在载板表面设置粘着层102,然后继续形成第一电子元件10的其它材料层。这里,粘着层102是具有粘着特性的材料层,例如可以采用pi(聚酰亚胺)或类似材料,只要温度高于粘着层102的玻璃化温度(tg),粘着层102就会软化而具有粘着效果。可选

的,粘着层102不包括氧化层,例如不包括siox。siox与siox的结合,要求结合平面必须具有较高的平坦度。参考图2,本技术实施例中,第一电子元件10的第一对接面11利用粘着层102替代siox,利用粘着层的粘着特性可直接粘合于第二电子元件20的第二对接面21,以此可以降低对平坦度的要求,省掉cmp平坦化制程。

50.参考图2,在一些可选的实施方式中,粘着层102与第二对接面21的结合介面与第一导电垫101的上表面1011平齐。参考图3d和3e,在制程上,第一电子元件10的粘着层102和导电垫101共同形成于第一载板31表面,去除第一载板31后具有表面平齐的特征,以有利于键合。

51.在一些可选的实施方式中,粘着层102包覆第一导电垫101,第一导电垫101的上表面1011露出于粘着层102。参考图3d和3e,在制程上,是在第一载板31表面形成第一导电垫101后,设置粘着层102,设置的粘着层102包覆第一导电垫101,后续去除第一载板31后第一导电垫101的上表面1011即露出于粘着层102。

52.在一些可选的实施方式中,第一导电垫101的侧壁直接接触粘着层102。参考图3d和3e,在制程上,可以是在第一载板31表面形成第一导电垫101后,即设置粘着层102,不需要提前在第一导电垫101侧壁形成种子层或者其他金属层,因而,第一导电垫101的侧壁直接接触粘着层102。

53.在一些可选的实施方式中,第一电子元件10还包括重布线层(rdl,redistributed layer)104,第一导电垫101位于重布线层104上并与重布线层104电连接。

54.在一些可选的实施方式中,第一电子元件10还包括埋孔103,埋孔103连接于第一导电垫101和重布线层104之间。参考图3c至3e,在制程上,是先在第一载板31表面形成第一导电垫101后,再在第一载板31表面设置粘着层102,然后在粘着层102上制作开孔以显露出第一导电垫101的下表面1012,然后对开孔进行金属化形成埋孔103。基于制程的特点,埋孔103的孔径往第一导电垫101的方向渐缩。这里,第一导电垫101和埋孔103都位于粘着层102内。

55.参考图2,在一些可选的实施方式中,第一电子元件10还进一步包括第一种子层108,第一种子层108位于第一导电垫101的下表面1012和埋孔103的上表面之间。在制程上,在粘着层102上制作开孔之后,对开孔进行金属化之前,先形成第一种子层108,以便于后续金属化形成埋孔103。

56.参考图2,在一些可选的实施方式中,第一电子元件10还进一步包括强化层105,重布线层104位于强化层105上。强化层105相较于粘着层102具有更高的硬度和强度,对粘着层102可以起到支撑作用。参考图3d和3e,在制程上,是在重布线层104上方形成强化层105,然后再去除第一载板31,基于强化层105的支撑作用,可以防止去除第一载板31后粘着层102收缩变形。这里,强化层105的材质可以采用各种模封材(molding compound)。示例性的,模封材可包括环氧树脂(epoxy resin)、填充物(filler)、催化剂(catalyst)、颜料(pigment)、脱模剂(release agent)、阻燃剂(flame retardant)、耦合剂(coupling agent)、硬化剂(hardener)、低应力吸收剂(low stress absorber)、粘合促进剂(adhesion promoter)、离子捕获剂(ion trapping agent)等。

57.参考图3a-3i,图3a-3i是本技术的半导体封装装置的一个实施例的制造步骤的示意图。

58.参考图3a,提供一第一载板31,并形成第一导电垫101于载板31表面。这里,第一载板31可以是具有平坦表面的玻璃载板或者其它材质的载板。这里,为便于制作第一导电垫101,可以先在第一载板31的表面形成一第二种子层(seed layer)110,然后便可以以电镀制程形成第一导电垫101。这里,制作出的第一导电垫101具有宽度往第一载板31方向渐缩的特征。

59.参考图3b,形成一粘着层102于第一载板31上,粘着层102包覆第一导电垫101。这里,粘着层102例如可以采用pi(聚酰亚胺)。可选的,可以通过旋转镀膜(spin-coating)制程在第一载板31上形成粘着层102。

60.参考图3c,在粘着层102上进行fo(fan-out,扇出)制程,制作出至少一层重布线层(rdl,redistribution layer)104。可选的,该制程中可以制作出至少一个埋孔103,用于实现第一导电垫101与重布线层104的电连接。

61.参考图3d,在重布线层104上设置强化层105。这里,强化层105可以采用模封材。至此,初步形成第一电子元件10,第一电子元件10包括第一导电垫101、粘着层102、埋孔103、重布线层104和强化层105。

62.参考图3e,去除第一载板31,以及,蚀刻去除第二种子层110(见图3a)。使得第一电子元件10露出第一对接面11,即接触第一载板31的表面。由于第一对接面11是在第一载板31的平坦表面形成的,具有相对平坦的表面,可直接用于后续的hbi制程,而不需要提前进行cmp平坦化。这里,第一导电垫101位于第一对接面11,去除第一载板31后,第一导电垫101的第一表面11露出。

63.参考图3f,提供第二电子元件20,第二电子元件20具有第二对接面21。这里,使用混合键合互连(hbi)技术将第一电子元件10与第二电子元件20进行直接键合,其中,第一对接面11与第二对接面21结合,第一导电垫101直接键合至第二导电垫201,粘着层102粘合于第二电子元件20。可选的,将第一电子元件10与第二电子元件20进行直接键合的过程包括:利用第一温度将粘着层102附着于第二电子元件20上,利用第二温度将第一导电垫101的上表面1011(见图3e)直接键合至第二电子元件20的第二导电垫201,其中,第一温度小于第二温度。第一温度用于使粘着层102软化,第二温度用于使第一导电垫101扩散结合至第二导电垫201。

64.参考图3g,设置模封层203对第二电子元件20进行封装(molding)。模封层203可以采用各种模封材料(molding compound)。

65.参考图3h,对经上述步骤制得的电子装置的底表面进行研磨(grinding)。这里,所说的底表面是指强化层105所在的一面。

66.参考图3i,在电子装置的底表面制作形成导电柱(cu pillar)106,导电柱106电连接于重布线层104。这里,导电柱106可用作焊接触点,用于与其它装置结合。

67.本实施例的制程,可以实现细间距(fine-pitch)键合,第一导电垫101的间距可以控制在30μm以下;可以使第一电子元件10的第一对接面11具有较高的共平面性,即第一导电垫101和粘着层102具有较好的共平面性;可以使第一对接面11的第一导电垫101和粘着层102的表面具有较低的粗糙度(ra),例如ra低于10nm乃至于低于5nm;可以实现较低的键合温度,例如低于250摄氏度。本实施例的制程有助于减少制程难度和降低成本并提高良率。

68.参考图4a-4l,图4a-4l是本技术的半导体封装装置的另一个实施例的制造步骤的示意图。

69.参考图4a-4d,提供一第一载板31,并依次形成第一导电垫101、粘着层102、重布线层104、强化层105,从而初步形成第一电子元件10。图4a-4d所示步骤类似于图3a-3d,这里不再详细赘述。

70.参考图4e,对第一电子元件10的强化层105进行研磨。

71.参考图4f,在第一电子元件10的表面制作形成导电柱106,导电柱106电连接于重布线层104。

72.参考图4g,在第一电子元件10的表面设置胶粘层107,胶粘层107包覆导电柱106。示例性的,胶粘层107可以采用tok(tokyo ohka kogyo,东京应化工业)胶。

73.参考图4h,在胶粘层107上方设置第二载板32。

74.参考图4i-4k,去除第一载板31,露出于第一电子元件10的第一对接面11。将第一电子元件10的第一对接面11与第二电子元件20的第二对接面21直接键合,并设置模封层203对第二电子元件20进行封装。图4i-4k所示的步骤类似于图3e-3g,这里不再详细赘述。

75.参考图4l,去除第二载板32以及去除胶粘层107(见图4k),使导电柱106露出。

76.以上步骤中未详细说明的部分,可参考前文对图3a-3i的说明。

77.与图3a-3i所示的制造步骤的主要不同在于,图4a-4l所示的制造步骤中,将制造导电柱106的步骤提前了,以此可以提高制程良率。这是因为,在半导体制程中,层数越多,误差越大,如3a-3i所示的制造步骤中是将制作导电柱106的步骤放在键合步骤之后,而图4a-4l所示的制造步骤中是将制作导电柱106的步骤放在键合步骤之前,键合步骤之前层数较少,以此,可以减少误差,提高制程良率。另外,制作导电柱106的制程属于一般的2.5d结构量产制程,制程良率把握度比较高,但需要利用tok胶(胶粘层107)保护导电柱106,故相较于图3a-3i所示的制造步骤而言,增加了上tok胶(见图4g)及移除tok胶(见图4k和4l)的步骤。

78.尽管已参考本技术的特定实施例描述并说明本技术,但这些描述和说明并不限制本技术。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效元件而不脱离如由所附权利要求书限定的本技术的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本技术中的技术再现与实际实施之间可能存在区别。可存在未特定说明的本技术的其它实施例。应将说明书和图示视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本技术的目标、精神以及范围。所有此些修改都落入在此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本文中所公开的方法,但应理解,可在不脱离本技术的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本文中特别指示,否则操作的次序和分组并不限制本技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1