一种功率模块的制作方法

1.本实用新型涉及一种功率模块,特别是一种并联芯片电气参数完全对称且杂散电感极低的功率模块。

背景技术:

2.现有技术并联芯片的功率回路的杂散参数不同,并联芯片的控制回路的杂散参数也不同,导致在开关瞬间,各并联芯片的电压应力,电流应力,热应力并不相同,综合应力最大的芯片成为整个模块的短板,其可靠性和寿命决定了整个模块的可靠性和寿命。现有大电流mosfet(metal-oxide-semiconductor field-effect transistor,金属-氧化物半导体场效应晶体管,简称金氧半场效晶体管)功率模块的电气互联结构,主要存在如下问题:

3.1)功率回路的杂散电感太大,开关瞬间杂散电感的储能急剧变化,导致与之串联的开关器件电压vds产生震荡性尖峰;由于mosfet的开关频率一般较高,此重复性的电压应力会逐渐损坏开关器件本体,导致整个变流器失效;

4.2)此震荡性电压vds导致主电流id同样震荡,对周围空间形成强烈的电磁发射,造成控制失效、通讯失败等故障;

5.3)对控制回路产生串扰耦合,在vgs电压波形上产生毛刺,严重时甚至造成vgs电平翻转,产生过流短路等故障,瞬间损坏功率mosfet。

技术实现要素:

6.本实用新型所要解决的技术问题是针对现有技术的上述缺陷,提供一种并联芯片电气参数完全对称且杂散电感极低的功率模块。

7.为了实现上述目的,本实用新型提供了一种功率模块,其中,所述功率模块为双芯片并联结构的硅基mosfet功率模块或sic-fet功率模块,包括:

8.散热板;

9.多个dbc组件,安装在所述散热板上,每个所述dbc组件包括基板和设置在所述基板上的功率回路、控制回路和感应电阻,所述功率回路包括以中轴线对称且左右并联的两对芯片,两对所述芯片的规格相同,中间的两个所述芯片并联后分别与交流端子和负极端子连接为下桥主回路,两端的两个所述芯片并联后分别与正极端子和所述交流端子连接为上桥主回路,所述下桥主回路和上桥主回路的路径长度相等;所述控制回路为并联电路,且所述控制回路的阻抗参数相同。

10.上述的功率模块,其中,所述散热板上设置有用于固定信号端子的引线支架,所述控制回路的控制信号来源于所述引线支架的同一个信号端子。

11.上述的功率模块,其中,所述基板为覆铜陶瓷基板,所述覆铜陶瓷基板的正面覆多块铜箔,所述覆铜陶瓷基板的背面覆一整块铜箔,所述覆铜陶瓷基板的正面和背面之间设置有用于绝缘和导热的中间层。

12.上述的功率模块,其中,所述多块铜箔包括功率回路区铜箔、控制回路区铜箔和

温度感应区铜箔,所述功率回路的两对芯片附着在所述功率回路区铜箔上;所述控制回路的驱动电阻附着在所述控制回路区铜箔上;所述感应电阻附着在所述温度感应区铜箔上。

13.上述的功率模块,其中,所述中间层为三氧化二铝层或氧化锆层。

14.上述的功率模块,其中,所述功率回路的两对所述芯片包括第一上桥芯片、第二上桥芯片、第一下桥芯片和第二下桥芯片,所述第一上桥芯片、第二上桥芯片、第一下桥芯片和第二下桥芯片的铜连接端子通过超声压接与所述功率回路区铜箔直接连接,或通过键合线与所述功率回路区铜箔连接。

15.上述的功率模块,其中,所述控制回路包括第一驱动电阻、第二驱动电阻和缓冲电路,所述缓冲电路为吸收电阻和吸收电容串联电路。

16.上述的功率模块,其中,所述控制回路的第一驱动电阻、第二驱动电阻和缓冲电路的铜连接端子通过超声压接与所述控制回路区铜箔直接连接,或通过键合线与所述控制回路区铜箔连接。

17.上述的功率模块,其中,所述第一驱动电阻和第二驱动电阻均为栅极驱动电阻。

18.上述的功率模块,其中,所述感应电阻为ntc热敏电阻。

19.本实用新型的技术效果在于:

20.本实用新型并联芯片的静态均流能力完全相同,即均流性能100%;并联芯片的动态均流能力完全相同,即动态均流性能达到100%;并联芯片的开关暂态电压过冲幅值完全相同,即动态电压应力完全相同;并联芯片的损耗完全相同,在具体应用中如果散热条件相同,则两者受到的热应力也完全相同。实现了针对并联芯片的完全相同的电气互联参数,包括主功率回路参数和控制回路参数;无论在开关瞬态工况还是稳态工况下,实现了电压应力、电流应力和功率损耗完全相同,避免了常见模块中并联芯片的物理应力不均形成的木桶短板效应;同时,功率回路的换流电感实现了最小化设计,极大降低了关断过程中器件两端的电压应力;并联芯片的电气应力完全一致性和最小化的电压应力极大地提高了功率模块的可靠性和寿命。

21.以下结合附图和具体实施例对本实用新型进行详细描述,但不作为对本实用新型的限定。

附图说明

22.图1为本实用新型一实施例的功率模块爆炸图;

23.图2为本实用新型一实施例的引线支架结构示意图;

24.图3为本实用新型一实施例的散热板结构示意图;

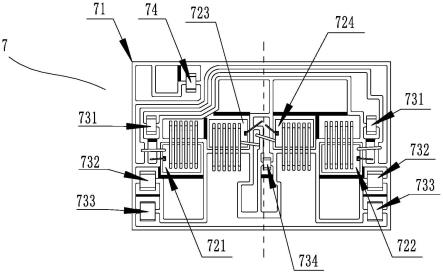

25.图4为本实用新型一实施例的功率模块结构示意图;

26.图5为本实用新型一实施例的dbc结构示意图;

27.图6a为本实用新型一实施例的dbc组件结构示意图;

28.图6b为图6a的侧视图;

29.图7为本实用新型一实施例的功率回路示意图;

30.图8为本实用新型一实施例的控制回路示意图。

31.其中,附图标记

32.1 散热板

33.11 冷却板

34.2 交流端子

35.3 引线支架

36.4 直流负极接线柱

37.5 直流正极接线柱

38.6 电容组件

39.7 dbc组件

40.71 基板

41.711 阻焊带

42.712 功率回路区铜箔

43.713 控制回路区铜箔

44.714 温度感应区铜箔

45.72 功率回路

46.721 第一上桥芯片

47.722 第二上桥芯片

48.723 第一下桥芯片

49.724 第二下桥芯片

50.725 键合线

51.73 控制回路

52.731 第一驱动电阻

53.732 吸收电阻

54.733 吸收电容

55.734 第二驱动电阻

56.74 感应电阻

57.75 正极端子

58.76 负极端子

59.77 信号端子

具体实施方式

60.下面结合附图对本实用新型的结构原理和工作原理作具体的描述:

61.参见图1-图4,图1为本实用新型一实施例的功率模块爆炸图,图2为本实用新型一实施例的引线塑料支架结构示意图,图3为本实用新型一实施例的散热板1结构示意图,图4为本实用新型一实施例的功率模块结构示意图。本实用新型的功率模块,为双芯片并联结构的硅基mosfet功率模块或sic-fet 功率模块,其中双芯片并联的半桥拓扑的mosfet功率模块,并联芯片的电压、电流和热应力的均衡是关键。该功率模块包括:散热板1,优选为铝材质,并在dbc组件7下方布置有冷却板11,下设冷却水道,用于冷却dbc上的芯片;多个dbc组件7,安装在所述散热板1上,每个所述dbc组件7包括基板71和设置在所述基板71上的功率回路72、控制回路73和感应电阻74,所述感应电阻74优选为ntc热敏电阻;所述功率回路

72包括以中轴线对称且左右并联的两对芯片,两对所述芯片的规格相同,均优选为mos芯片,中间的两个所述芯片并联后分别与交流端子2和负极端子76连接为下桥主回路,两端的两个所述芯片并联后分别与正极端子75和所述交流端子2连接为上桥主回路,所述下桥主回路和上桥主回路的路径长度相等;所述控制回路73为并联电路,且所述控制回路73的阻抗参数相同。

62.其中,所述散热板1上设置有用于固定信号端子77的引线支架3,所述控制回路73的控制信号来源于所述引线支架3的同一个信号端子77;交流端子2,与定子相端用螺栓导电连接;直流负极接线柱4,与负极端子76连接;直流正极接线柱5,与正极端子75连接。还可设置电容组件6,连接于正极端子75和负极端子76之间,用于滤波。

63.参见图5,图5为本实用新型一实施例的dbc结构示意图。本实施例的所述基板71优选为覆铜陶瓷基板,所述覆铜陶瓷基板的正面覆多块铜箔及多处阻焊带711(见图8所示),用于电子元件的附着,所述覆铜陶瓷基板71 的背面覆一整块铜箔,用于与冷却板11附着,所述覆铜陶瓷基板71的正面和背面之间设置有用于绝缘和导热的中间层。其中,所述多块铜箔包括功率回路区铜箔712、控制回路区铜箔713和温度感应区铜箔714,功率回路区铜箔712 用于后续附着功率回路72的mos,及用于导通大电流的键合线725;控制回路区铜箔713用于后续附着控制回路73的驱动电阻、驱动电容及用于导通信号的键合线725;温度感应区铜箔714用于后续附着温度感应的感应电阻74,优选ntc热敏电阻,其电阻值随温度升高而降低。本实施例中,所述功率回路72的两对芯片附着在所述功率回路区铜箔712上;所述控制回路73的驱动电阻附着在所述控制回路区铜箔713上;所述感应电阻74附着在所述温度感应区铜箔714上。所述中间层优选为三氧化二铝层或氧化锆层。mos芯片产生的热量通过dbc正面的铜箔传导至中间层,再传导至背面的铜箔,再传导至冷却板11,径冷却板11内的冷却水把热量带走。

64.参见图6a、6b,图6a为本实用新型一实施例的dbc组件7结构示意图,图6b为图6a的侧视图。本实施例所述功率回路72的两对所述芯片包括第一上桥芯片721、第二上桥芯片722、第一下桥芯片723和第二下桥芯片724,所述第一上桥芯片721、第二上桥芯片722、第一下桥芯片723和第二下桥芯片724的铜连接端子通过超声压接与所述功率回路区铜箔712直接连接,或通过键合线725与所述功率回路区铜箔712连接。所述控制回路73包括第一驱动电阻731、第二驱动电阻734和缓冲电路,所述缓冲电路为吸收电阻732和吸收电容733串联电路。所述控制回路73的第一驱动电阻731、第二驱动电阻734和缓冲电路的铜连接端子通过超声压接与所述控制回路区铜箔713直接连接,或通过键合线725与所述控制回路区铜箔713连接。所述第一驱动电阻 731和第二驱动电阻734均优选为栅极驱动电阻。

65.参见图7,图7为本实用新型一实施例的功率回路72示意图。如图中箭头线所示,从结构上看,功率回路72路径很短,使得功率回路72的电感达到最小,左边两个芯片组成一个完整的功率回路72,右边两个芯片并联进来起分流作用,四个mos芯片的规格完全相同,中间的两个芯片并联,两端的两个芯片并联。功率回路72中的电流同一时刻走中间的两个芯片,如图中部箭头线所示,即下桥主回路:交流端子2—铜箔—mos漏极—mos—mos源极—键合线725—铜箔—负极端子,功率回路72在并联的下桥所经历的路径长度接近相等;下一个时刻电流走两端的两个芯片,如图两边箭头线所示,即上桥主回路:正极端子—铜箔—mos漏极—mos—mos源极—键合线725—铜箔—交流端子2,功率回路72在并联的上桥所经历的

路径长度接近相等。这样可以使功率回路72的杂散参数接近相同。所以左右并联的两对芯片在结构上完全对称,使得芯片的电气应力完全一致。电流路线短使得功率回路72的电感几乎最小,极大降低了电流在关断过程中芯片两端产生的电压,极大提高了芯片的安全性、可靠性和寿命。

66.参见图8,图8为本实用新型一实施例的控制回路73示意图。控制回路 73中,通过几何结构的优化和电磁场有限元的校核分析,实现了控制回路73 的阻抗参数完全相同,保证了并联芯片触发的时间一致性;所有功率芯片的控制回路73采用并联电路,确保了控制回路73自阻抗的最小化。如图8所示,第一上桥芯片721的控制回路73为最左侧虚线箭头线,第二上桥芯片722的控制回路73为最右侧虚线箭头线,控制信号来源于引线支架3的同一个信号端子77(本实施例为图中右上角的信号端子77)。这两个控制回路73采用并联电路,并联电路能使控制回路73中的阻抗最小化。控制信号来源同一端子,有利于并联芯片触发时间相同。中间两个mos芯片即第一下桥芯片723和第二下桥芯片724的控制回路73为中间虚线箭头线回路,控制信号来源于引线支架3的同一个信号端子77,且回路长度相同,有利于这两个并联的芯片触发控制信号时间相同,整个控制回路73比较长,控制信号从控制板发出,经过引线支架3上的信号端子77另一端传递到端子正面,进入功率模块的控制回路73上。

67.本实用新型综合运用电气、电磁、机械和热的多物理场设计分析,并考虑实际加工工艺的具体需求,采用基于直接键合铜衬底(dbc,direct bondingcopper,覆铜陶瓷基板71,是一种陶瓷表面金属化技术)的结构。有限元分析表明,该结构实现了针对并联芯片的完全相同的电气互联参数,包括主功率回路72参数和控制回路73参数。采用全波电气模型仿真表明,该功率模块中对上管和下管的并联芯片,无论在开关瞬态工况还是稳态工况下,实现了电压应力、电流应力和功率损耗完全相同,避免了常见模块中并联芯片的物理应力不均形成的木桶短板效应;同时,功率回路72的换流电感实现了最小化设计,极大降低了关断过程中器件两端的电压应力。并联芯片的电气应力完全一致性和最小化的电压应力,两种因素的综合极大地提高了功率模块的可靠性和寿命。

68.本实用新型并联的功率芯片在几何结构上,按照中轴线完全对称,图6a 的中心线即为中轴线;功率回路72中的功率芯片,确保功率回路72中的杂散电感最小化;控制回路73中,通过几何结构的优化和电磁场有限元的校核分析,实现了控制回路73的阻抗参数完全相同,保证了并联芯片触发的时间一致性;所有功率芯片的控制回路73采用并联电路,确保了控制回路73自阻抗的最小化,同时确保了强电电磁场对控制回路73影响的最小化;本实用新型不仅适合于硅基(si-based)mosfet功率模块,也适合基于sic-fet的功率模块。并联芯片的静态均流能力完全相同,即均流性能100%;并联芯片的动态均流能力完全相同,即动态均流性能达到100%;并联芯片的开关暂态电压过冲幅值完全相同,即动态电压应力完全相同;并联芯片的损耗完全相同,在具体应用中如果散热条件相同,则两者受到的热应力也完全相同。

69.当然,本实用新型还可有其它多种实施例,在不背离本实用新型精神及其实质的情况下,熟悉本领域的技术人员当可根据本实用新型作出各种相应的改变和变形,但这些相应的改变和变形都应属于本实用新型所附的权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1