一种反向导通压降的SiCMOSFET器件的制作方法

一种反向导通压降的sic mosfet器件

技术领域

1.本实用新型涉及一种反向导通压降的sic mosfet器件。

背景技术:

2.半导体功率器件是电子电力技术的核心元器件,通常电子电力系统要求功率器件具有导通电阻、高耐压、反向导通压降、高开关速度和易于驱动等特性。sic材料由于其材料的固有优势,诸如其临界击穿电场强度约是硅10倍,热导率是约是硅的3,因而sic mosfet 在功率密度、损耗以及散热等方面相较于硅基器件有显著优势。然而,由于高的临界击穿电场强度(约3e6 v/cm)导致关态耐压时槽栅氧化层电场强度过高,带来一系列可靠性问题。所以在sic mosfet 元胞设计中必须考虑对氧化层中电场抑制。如公开号为 cn111697077a的一种sic沟槽栅功率mosfet器件,目前,最常见有效的方法是在槽栅底部设置一个接地的p型电场屏蔽区。该电场屏蔽区一般通过结终端接地。随着芯片电流增大,元胞区到结终端区域距离增加,导致长距离的p型电场屏蔽区的分布电阻增加,从而接地效果变差,最终将导致sic mosfet动态电阻增加,动态损耗增加。所以,该方案会限制单芯片的电流大小。

3.如公开号为cn109427869a的一种半导体,其在n型基底设置了槽单元,并在槽内设置p型电场屏蔽区,但其p型电场屏蔽区并未与其源极金属层形成电气连接,所以其同样导致长距离的p型电场屏蔽区的分布电阻增加,从而接地效果变差。

4.此外,sic材料大的禁带宽度特性决定了其自身集成的反并联pin 二极管反向导通压降约为3v,导致其反向导通损耗过高。所以,如公开号为cn103441148b的一种集成肖特基二极管的槽栅vdmos器件,在同一芯片内集成低导通压降的反并联肖特基二极管schottkybarrier diode:sbd成为sic mosfet的一个重要发展方向。但是,引入的肖特基二极管的泄露电流会在关态强电场下急剧增加,增加关态损耗、降低击穿电压。因而,需要在肖特基结周围设置p型电场屏蔽区来抑制肖特基势垒降低效应,降低关态泄漏电流,避免击穿电压下降。

技术实现要素:

5.为解决上述技术问题,本实用新型提供了一种反向导通压降的 sic mosfet器件。

6.本实用新型通过以下技术方案得以实现。

7.本实用新型提供的一种反向导通压降的sic mosfet器件,包括其元胞;元胞包括n型耐压层、与n型耐压层的背面接触的n型缓冲、与n型缓冲的背面接触的衬底、与衬底的背面接触的漏极金属层,所述n型耐压层的正面与基区接触;所述元胞的正面还加工有n个深槽将基区分割,在元胞边缘的基区上端设置有第一掺杂区,在相邻深槽之间的基区上设置有第一掺杂区和第二掺杂区,深槽的下端设置有屏蔽区,深槽内填充有多晶硅栅或源极金属,所述多晶硅栅和深槽之间设置有栅介质层,栅介质层底部设置有屏蔽区,所述屏蔽区通过栅介质层侧面的连通区与源极金属层电气连接,所述深槽内的源极金属与源极金属层接触。

8.所述多晶硅栅上端覆盖有钝化层。

9.所述n个深槽的数量大于2。

10.以元胞任一边缘的第一个深槽为第1深槽,则1至第n-1个深槽中填充有多晶硅栅,第n个深槽内填充有源极金属。

11.所述衬底、第二掺杂区均为n型重掺杂半导体,第一掺杂区为p 型重掺杂半导体。

12.所述第一掺杂区和基区的一端与连通区接触,相邻第一掺杂区和第二掺杂区之间接触,第二掺杂区的一端与栅介质层接触。

13.所述屏蔽区为p型电场屏蔽区。

14.所述连通区为p型电场连通区。

15.进一步,所述p型基区下方设置有掺杂浓度高于耐压层的n型电流通路区。所述n型电流通路区的浓度至少是耐压区的两倍。

16.本实用新型的有益效果在于:屏蔽区与连通区连接形成接地的电气接触,从而避免了需要采用终端区接地带来的问题;并且可以调节沟槽数目来调节沟道密度,灵活地调节器件的反向导通压降和比导通电阻。

附图说明

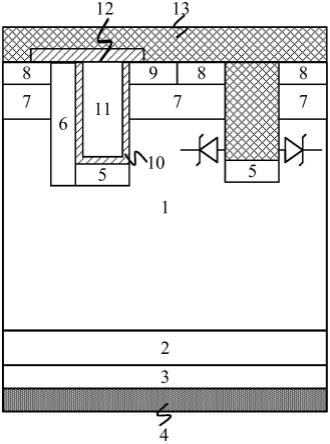

17.图1是本实用新型的单槽栅器件结构示意图;

18.图2是本实用新型的多槽栅器件结构示意图;

19.图3是本实用新型的单槽栅器件增加n型电流通路区的结构示意图;

20.图4是本实用新型的多槽栅器件增加n型电流通路区的结构示意图;

21.图中:1-n型耐压层,2-n型缓冲,3-衬底,4-漏极金属层,5-屏蔽区,6-连通区,7-基区,8-第一掺杂区,9-第二掺杂区,10-栅介质层,11-多晶硅栅,12-钝化层,13-源极金属层,14-n型电流通路区。

具体实施方式

22.下面进一步描述本实用新型的技术方案,但要求保护的范围并不局限于所述。

23.实施例1

24.本实施例提供一种反向导通压降的sic mosfe器件,其结构如图1所示,需要说明的是,为避免附图标记的冗杂,相同类型的半导体区域采用同一附图标记;具体来讲,元胞包括:

25.1.一种反向导通压降的sic mosfet器件,其元胞结构包括:

26.n型耐压层1;

27.设置在n型耐压层下表面的n型缓冲层2,设置在n型缓冲层下表面的n型重掺杂半导体衬底3,以及设置在n型重掺杂半导体下表面的漏极金属4;

28.n型耐压层1内设置有p型电场屏蔽区5,p型电场连通区6,以及p型半导体基区7;

29.元胞表面设置有第一深槽和第二深槽;所述第一深槽由位于槽壁的栅介质层10与位于槽内的多晶硅栅11构成,上表面覆盖有钝化层12;所述第二深槽内部填充与源极金属层13相同的源极金属;所述第一深槽和第二深槽底部均设置有p型电场屏蔽区5,并且第一深槽底部的p型电场屏蔽区通过p型电场连通区6与表面的源极金属层 13电气相连;

30.所述p型电场连通区6与第一深槽侧壁及第一深槽底部的p型电场屏蔽区5相接触,上表面覆盖有钝化层12;

31.所述p型电场连通区6、第一深槽和第二深槽将p型半导体基区 7分隔,从左至右依次形成第1个p型半导体基区子区、第2个p型半导体基区子区和第3个p型半导体基区子区;

32.所述第1个p型半导体基区子区上表面设置有第1个重掺杂p 型半导体区8,且第1个重掺杂p型半导体区上表面覆盖有源极金属层13;所述第1个重掺杂p型半导体区8与所述p型电场连通区6 相接触;

33.所述第2个p型半导体基区子区上表面设置有相邻接的第1个重掺杂n型半导体区9和第2个重掺杂p型半导体区8,所述第1个重掺杂n型半导体区9与所述栅介质10接触,且二者上表面均覆盖有源极金属层13;

34.所述第3个p型半导体基区子区上表面设置有第3个重掺杂p 型半导体区8,且第3个重掺杂p型半导体区上表面覆盖有源极金属层13。

35.所述第一掺杂区和第二掺杂区的掺杂浓度为1e19 cm-3

。

36.所述源极金属层13位于第二个深槽内的部分侧壁金属与n型耐压区1直接接触并且形成n型肖特基二极管。

37.本实施例中,上述反向导通压降的sic mosfet器件,在深槽内的源极金属与n型耐压区1接触形成反并联的肖特基二极管,用于降低器件的反向导通压降;所述p型电场屏蔽区5将栅氧化层和肖特基结表面的电场强度屏蔽在一个较低的值,从而将关态的泄漏电流维持在一个较低的值,同时避免器件的击穿电压降低,并且所述的p 型电场屏蔽区5通过一个电场连通区6形成接地的电气接触,避免了较长的结终端区接地带来的动态电阻增加的问题。

38.实施例2

39.本实施例提供一种反向导通压降的sic mosfe器件,其结构如图2所示,具体来讲,元胞包括:

40.n型耐压层1;

41.设置在n型耐压层下表面的n型缓冲层2,设置在n型缓冲层下表面的n型重掺杂半导体衬底3,以及设置在n型重掺杂半导体下表面的漏极金属4;

42.n型耐压层1内设置有p型电场屏蔽区5,p型电场连通区6,以及p型半导体基区7;

43.元胞表面设置有n个深槽,n≥2,从左至右依次为第1个深槽、第2个深槽

……

第n个深槽;所述第1~n-1个深槽采用相同结构,由位于槽壁的栅介质层10与位于槽内的多晶硅栅11构成,上表面覆盖有钝化层12;所述第n个深槽内部填充与源极金属层13相同的源极金属;所述n个深槽底部均设置有p型电场屏蔽区5,并且第i(i=1,2,

……

n-1)个深槽底部的p型电场屏蔽区通过第i个p型电场连通区6与表面的源极金属层13电气相连;

44.所述第i个p型电场连通区与第i个深槽及第i个深槽底部的p 型电场屏蔽区5相接触,上表面覆盖有钝化层12;

45.所述n-1个p型电场连通区和n个深槽将p型半导体基区7分隔,依次形成第1个p型半导体基区子区,第2个p型半导体基区子区

……

第n个p型半导体基区子区和第n+1个p型半导体子区;

46.第1个p型半导体基区子区上表面设置有第1个重掺杂p型半导体区8,且第1个重掺

杂p型半导体区上表面覆盖有源极金属层13;

47.第2~n个p型半导体基区子区上表面分别设置有相邻接的第 1~n-1个重掺杂n型半导体区9和第2~n个重掺杂p型半导体区8,且二者上表面均覆盖有源极金属层13,所述第1~n-1个重掺杂n型半导体区9与所述1~n个槽的栅介质10接触分别接触;

48.第1~n-1个重掺杂p型半导体区8分别与所述1~n-1个p型电场连通区6相接触;

49.第n+1个p型半导体基区子区上表面设置有第n+1个重掺杂p 型半导体区8,且第n+1个重掺杂p型半导体区上表面覆盖有源极金属层13。

50.源极金属层13位于第n个深槽内的部分侧壁金属与n型耐压区1 直接接触并且形成n型肖特基二极管。

51.本实施例中,上述反向导通压降的sic mosfet器件,所述源极金属13与n型耐压区1接触形成反并联的肖特基二极管,用于降低器件的反向导通压降;所述p型电场屏蔽区5将栅氧化层和肖特基结表面的电场强度屏蔽在一个较低的值,从而将关态的泄漏电流维持在一个较低的值,同时避免器件的击穿电压降低,并且所述的p型电场屏蔽区5通过一个电场连通区6形成接地的电气接触,避免了较长的结终端区接地带来的动态电阻增加的问题;此外,还可以通过调节沟槽数目灵活调节沟道密度,进一步灵活调节器件的反向导通压降和比导通电阻。

52.实施例3

53.如图3,本实施例和实施例1相同,除了p型基区7下方设置有n型电流通路区14,所述n型电流通路区14的掺杂浓度比n型耐压区1高至少两倍以上。

54.本实施例除了实施例1的益处外,通过增加掺杂较重的n型半导体层14可以在减小两个槽之间由于p型电场屏蔽区以及连通区存在而引入的jfet电阻的同时,有利于进一步缩小槽与槽的间距,提高沟道密度,减低沟道电阻。

55.实施例4

56.如图4,本实施例和实施例1相同,除了p型基区7下方设置有n型电流通路区14,所述n型电流通路区14的掺杂浓度比n型耐压区1高至少两倍以上。

57.本实施例除了实施例1的益处外,通过增加掺杂较重的n型半导体层14可以在减小两个槽之间由于p型电场屏蔽区以及连通区存在而引入的jfet电阻的同时,有利于进一步缩小槽与槽的间距,提高沟道密度,减低沟道电阻。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1