一种瞬态电压抑制保护器件及电子产品的制作方法

1.本技术实施例涉及集成电路技术领域,具体涉及一种瞬态电压抑制保护器件及电子产品。

背景技术:

2.随着电子产品信号传输速率不断增加,半导体器件工艺制程越来越先进,电子产品对esd(静电释放)和eos(电气过应力)的承受能力越来越弱,这就需要增加瞬态电压抑制保护器件(tvs)对电子产品中半导体器件进行防护,所以对tvs器件提出更高的要求,需要更低的触发电压和钳位电压、更小的电容,现有tvs产品存在工艺复杂,触发电压和钳位电压较高问题,对半导体器件保护存在很大问题。

技术实现要素:

3.本技术提供的实施例一个目的在于克服上述问题或者至少部分地解决或缓减上述问题。

4.本技术提供的实施例另一目的解决了现有产品工艺上存在的低容tvs触发电压和钳位电压较高、动态阻抗大的问题,制作出一种低成本工艺简单的高性能瞬态电压抑制保护器件,可以在较低电压开启工作并具有钳位电压低、动态阻抗小、低电容等优点。

5.第一方面,本技术实施例提供了一种瞬态电压抑制保护器件,包括衬底,第一阱,第二阱和第三阱,第一注入区,第二注入区,第三注入区和第四注入区;

6.所述第一阱,第二阱,第三注入区和第三阱依次从左到右相互间隔设置在衬底上,所述第一阱,第二阱,第三阱和第三注入区的掺杂类型相同,所述衬底,第一注入区、第二注入区和第四注入区的掺杂类型相同,所述第一注入区设置在与其掺杂类型不同的第一阱中,所述第二注入区设置在与其掺杂类型不同的第二阱中,所述第四注入区设置在其掺杂类型不同的第三阱中;

7.所述第一注入区通过金属引出的第一电极及第四注入区通过金属引出的第二电极都作为器件的阴极,第二注入区通过金属引出的第三电极及第三注入区通过金属引出的第四电极作为器件的阳极。

8.作为本技术一优选实施例,所述第一阱,第二阱,第三阱和第三注入区均为p型掺杂,所述衬底,第一注入区、第二注入区和第四注入区均为n型掺杂。

9.作为本技术一优选实施例,所述保护器件还包括第四阱,所述第三注入区设置在所述第四阱中,所述第四阱的掺杂类型均与所述第一阱,第二阱,第三阱和第三注入区相同。

10.作为本技术一优选实施例,所述保护器件还包括第五注入区和第六注入区,所述第五注入区和第六注入区设置在所述第四阱中,且所述第五注入区和所述第六注入区的掺杂类型与所述第四阱相同。

11.作为本技术一优选实施例,所述第五注入区和第六注入区分布在第三注入区的两

侧。

12.作为本技术一优选实施例,所述第一阱,第二阱,第三注入区和第三阱相互间隔距离为5-20um。

13.作为本技术一优选实施例,所述衬底的电阻率为30-2000ω

·

cm。

14.与现有技术相比,本技术实施例提供了一种瞬态电压抑制保护器件,本技术通过采用高阻衬底,通过共用集电极串联两个基区开路三极管再并联一个超低触发电压pnpn结构,利用半导体穿通特性,解决了高阻衬底三极管单向截止特性导致器件无法正常单独应用的问题。同时通过串联可以使器件电容减半,获得更小的电容。再通过并联低电容超低触发电压pnpn结构做成新型单向低容tvs,解决实际应用中对防护器件的特殊需求。

15.第二方面,本技术实施例提供了一种电子产品,包括上述任一项所述瞬态电压抑制保护器件。

16.与现有技术相比,第二方面,本技术实施例提供的电子产品的有益效果与上述第一方面任一技术方案所述的瞬态电压抑制保护器件的有益效果相同,在此不做赘述。

附图说明

17.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

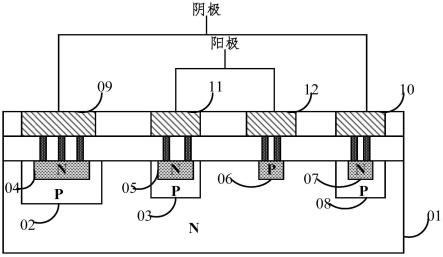

18.图1为本技术一实施例提供的一种瞬态电压抑制保护器件的剖面图;

19.图2为本技术一实施例公开的瞬态电压抑制保护器件的等效电路图;

20.图3为本技术另一实施例公开的一种瞬态电压抑制保护器件的剖面图;

21.图4为本技术一个实施例提供的一种瞬态电压抑制保护器件的剖面图。

具体实施方式

22.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

23.下面结合附图,详细说明本技术的各种非限制性实施方式。

24.第一方面,本技术实施例提供的瞬态电压抑制保护器件,其是一种电流控制型器件,由输入电流控制输出电流,其本身具有电流放大作用,它工作时有电子和空穴两种载流子参与导电过程。

25.半导体三极管有三个电极,分别是发射极,基极和集电极,半导体三极管在工作时要加工作电压,于是就产生了各极电流,半导体三极管在工作时发射极电流等于基极和集电极电流之和,其中基极电流最小,发射极电流最大,在基极加一很小的电流,在集电极就能输出很大的电流,因此三极管有放大作用。

26.实施例1

27.如图1所示,本技术实施例提供了一种瞬态电压抑制保护器件,包括衬底01,第一

阱02,第二阱03和第三阱08,第一注入区04,第二注入区05,第三注入区06和第四注入区07;

28.所述第一阱02,第二阱03,第三注入区06和第三阱08依次从左到右相互间隔设置在衬底01上,所述第一阱02,第二阱03,第三阱08和第三注入区06的掺杂类型相同,所述衬底01,第一注入区04、第二注入区05和第四注入区07的掺杂类型相同,所述第一注入区04设置在与其掺杂类型不同的第一阱02中,所述第二注入区05设置在与其掺杂类型不同的第二阱03中,所述第四注入区07设置在其掺杂类型不同的第三阱08中;

29.所述第一注入区04通过金属09引出的第一电极及第四注入区07通过金属10引出的第二电极都作为器件的阴极,第二注入区05通过金属11引出的第三电极及第三注入区06通过金属12引出的第四电极作为器件的阳极。

30.所述第一阱02,第二阱03,第三阱08和第三注入区06均为p型掺杂,所述衬底01,第一注入区04、第二注入区05和第四注入区07均为n型掺杂。

31.在本技术实施例中,所述第一阱02,第二阱03,第三注入区06和第三阱08相互间隔距离为5-20um。

32.在本技术实施例中,所述衬底01的电阻率为30-2000ω

·

cm。

33.如图2所示,通过本技术实施例瞬态电压抑制保护器件通过两个横向基极开路三极管npn串联后再并联低电容超低触发电压pnpn结构,在n型衬底01电阻率30-2000ohm

·

cm上注入形成p型掺杂区第一阱02,第二阱03和第三阱08,在衬底01注入形成p型高掺杂区第三注入区06,在p型掺杂区第一阱02注入形成n型高掺杂区第一注入区04,在第二阱03注入形成n型高掺杂区第二注入区05,在第三阱08注入形成n型高掺杂区第四注入区07,通过调整第二阱03和第三注入区06面积形成低电容低触发tvs。

34.实施例2

35.如图3所示,实施例2在实施例1的基础上,所述保护器件还包括第四阱13,所述第三注入区06设置在所述第四阱13中,所述第四阱13的掺杂类型均与所述第一阱02,第二阱03,第三阱13和第三注入区06相同。所述第四阱13的掺杂类型为p型掺杂,本技术实施例通过并联低电容超低触发电压pnpn结构,获得更小的电容。

36.实施例3

37.如图4所示,实施例3在实施例2的基础上,所述保护器件还包括第五注入区14和第六注入区15,所述第五注入区14和第六注入区15设置在所述第四阱13中,且所述第五注入区14和第六注入区15的掺杂类型与所述第四阱13同。所述第五注入区14和第六注入区15分布在第三注入区06的两侧。第六注入区15掺杂类型为p型掺杂,通过寄生npnpn结构可以增加浪涌和esd防护能力。

38.第三方面,本技术实施例还提供了一种电子产品。该电子产品包括本技术提供单向瞬态电压抑制保护器件。

39.其中,上述电子产品可以为显示终端、通讯设备、工程设备等,在此不一一列出。

40.与现有技术相比,第三方面本技术实施例提供的电子产品的有益效果与上述第一方面任一技术方案所述的单向瞬态电压抑制保护器件的有益效果相同,在此不做赘述。

41.在上述实施方式的描述中,具体特征、结构或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

42.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽

管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1