一种嵌入式多制层封装芯片的制作方法

1.本实用新型涉及芯片封装技术领域,具体涉及一种嵌入式多制层封装芯片。

背景技术:

2.emcp(embedded multi-chip package)嵌入式多制层封装芯片与传统的mcp相较之下,emcp因为有内建的nand flash控制晶片,可以减少主晶片运算的负担,并且管理更大容量的快闪记忆体。

3.然而嵌入式多制层封装芯片产品要求产品容量足够大,堆叠层数多,由于单颗产品尺寸大小及空间的限制,若底层芯片尺寸过小,会导致高层大尺寸芯片在打线过程中芯片存在裂片和翘边高风险。

技术实现要素:

4.为了解决上述技术问题,本实用新型提供的一种嵌入式多制层封装芯片,其结构简单,操作方便,解决了现有技术中底层芯片尺寸过小导致顶层芯片在打线过程中芯片存在裂片和翘边的技术问题,提高了芯片的封装良率。

5.为了达到上述目的,本实用新型的技术方案如下:

6.本实用新型提供一种嵌入式多制层封装芯片,包括:基板,所述基板上设有底层芯片,所述底层芯片上设有多层顶层芯片,所述基板与所述顶层芯片之间形成悬空区域,所述悬空区域内设有减少悬空假片,且所述减少悬空假片与所述底层芯片呈相对设置。

7.本实用新型提供的一种嵌入式多制层封装芯片,其结构简单,操作方便,解决了现有技术中底层芯片尺寸过小导致顶层芯片在打线过程中存在裂片和芯片翘边的技术问题,提高了芯片的封装良率。

8.作为优选技术方案,所述减少悬空假片通过第一贴片胶膜与所述基板连接。

9.作为优选技术方案,所述顶层芯片的尺寸大于所述底层芯片的尺寸,所述减少悬空假片的高尺寸等于所述底层芯片的高尺寸。

10.作为优选技术方案,所述悬空区域布满打线焊盘。

11.作为优选技术方案,所述底层芯片通过第二贴片胶膜与所述基板连接。

12.作为优选技术方案,所述顶层芯片与底层芯片和减少悬空假片之间设有导线包裹胶膜。

13.作为优选技术方案,所述顶层芯片设置于所述导线包裹胶膜上,所述顶层芯片包括:第一顶层芯片和第二顶层芯片,所述第一顶层芯片与所述第二顶层芯片错开式堆叠,所述第一顶层芯片通过第三贴片胶膜与所述第二顶层芯片连接。

14.作为优选技术方案,所述顶层芯片上至少连接有一根金线,所述底层芯片至少连接有两根金线。

15.作为优选技术方案,所述基板上设有主控芯片,所述主控芯片与所述底层芯片呈相对设置,所述主控芯片通过第四贴片胶膜与所述基板连接。

16.作为优选技术方案,所述主控芯片上至少连接有一根金线。

17.本实用新型提供的一种嵌入式多制层封装芯片,其结构简单,操作方便,解决了现有技术中底层芯片尺寸过小导致顶层芯片在打线过程中存在裂片和芯片翘边的技术问题,提高了芯片的封装良率。

附图说明

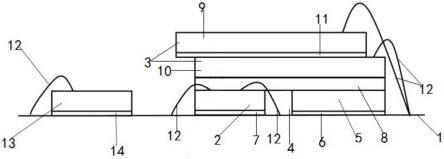

18.图1为本实用新型提供的嵌入式多制层封装芯片的打线图;

19.图2为本实用新型提供的嵌入式多制层封装芯片的堆叠图;

20.其中,1-基板;2-底层芯片;3-顶层芯片;4-悬空区域;5-减少悬空假片;6-第一贴片胶膜;7-第二贴片胶膜;8-导线包裹胶膜;9-第一顶层芯片;10-第二顶层芯片;11-第三贴片胶膜;12-金线;13-主控芯片;14-第四贴片胶膜。

具体实施方式

21.下面结合附图详细说明本实用新型的优选实施方式。

22.可以理解,本实用新型是通过一些实施例达到本实用新型的目的,如图1-2所示,本实用新型提供的嵌入式多制层封装芯片,包括:基板1,所述基板1上设有底层芯片2,所述底层芯片2上设有多层顶层芯片3,所述基板1与所述顶层芯片3之间形成悬空区域4,所述悬空区域4内设有减少悬空假片5,且所述减少悬空假片5与所述底层芯片2呈相对设置;所述减少悬空假片5通过第一贴片胶膜6与所述基板1连接;所述顶层芯片3的尺寸大于所述底层芯片2的尺寸,所述减少悬空假片5的高尺寸等于所述底层芯片2的高尺寸;所述悬空区域4布满打线焊盘;所述底层芯片2通过第二贴片胶膜7与所述基板1连接;所述顶层芯片3与所述底层芯片2和减少悬空假片5之间设有导线包裹胶膜8;所述顶层芯片3设置于所述导线包裹胶膜8上,所述顶层芯片3包括:第一顶层芯片9和第二顶层芯片10,所述第一顶层芯片9与所述第二顶层芯片10错开式堆叠,所述第一顶层芯片9通过第三贴片胶膜11与所述第二顶层芯片10连接;所述顶层芯片3上至少连接有一根金线12,所述底层芯片2至少连接有两根金线12;所述基板1上设有主控芯片13,所述主控芯片13与所述底层芯片2呈相对设置,所述主控芯片13通过第四贴片胶膜14与所述基板1连接;所述主控芯片13上至少连接有一根金线12;其结构简单,操作方便,解决了现有技术中底层芯片2尺寸过小导致顶层芯片3在打线过程中芯片存在裂片和翘边的技术问题,提高了芯片的封装良率。

23.在一些实施例中,包括:基板1,所述基板1上设有底层芯片2,所述底层芯片2上设有多层顶层芯片3,所述基板1与所述顶层芯片3之间形成悬空区域4,所述悬空区域4内设有减少悬空假片5,且所述减少悬空假片5与所述底层芯片2呈相对设置。

24.采用上述实施例,其结构简单,操作方便,在悬空区域4内设有减少悬空假片5,减少悬空假片5设置能够减小或去除悬空区域的面积,减小或去除悬空区域的面积能够有效避免了打线键合过程中因为受力程度不同导致芯片翘边和裂片的技术问题出现。

25.在一些实施例中,所述减少悬空假片5通过第一贴片胶膜6与所述基板1连接。

26.采用上述实施例,其结构简单,操作方便,保证了芯片封装的稳定性。

27.在一些实施例中,所述顶层芯片3的尺寸大于所述底层芯片2的尺寸,所述减少悬空假片的高尺寸等于所述底层芯片的高尺寸。

28.采用上述实施例,其结构简单,操作方便,顶层芯片3的长度尺寸比所述底层芯片2的长度尺寸过大会导致悬空区域4的面积过大,减少悬空假片的高尺寸等于所述底层芯片的高尺寸保证了芯片封装结构的稳定性。

29.在一些实施例中,所述悬空区域布满打线焊盘。

30.采用上述实施例,其结构简单,操作方便,便于对芯片打线键合。

31.在一些实施例中,所述底层芯片2通过第二贴片胶膜7与所述基板1连接。

32.采用上述实施例,其结构简单,操作方便,保证了芯片封装的稳定性。

33.在一些实施例中,所述顶层芯片3与所述底层芯片2和减少悬空假片5之间设有导线包裹胶膜8。

34.采用上述实施例,其结构简单,操作方便,保证了芯片封装的稳定性。

35.在一些实施例中,所述顶层芯片3设置于所述导线包裹胶膜8上,所述顶层芯片3包括:第一顶层芯片9和第二顶层芯片10,所述第一顶层芯片9与所述第二顶层芯片10错开式堆叠,所述第一顶层芯片9通过第三贴片胶膜11与所述第二顶层芯片10连接。

36.采用上述实施例,其结构简单,操作方便,这样能够同步满足顶层芯片3更多层数堆叠,从而可以增加产品的容量。

37.在一些实施例中,所述顶层芯片3上至少连接有一根金线12,所述底层芯片2至少连接有两根金线12。

38.采用上述实施例,其结构简单,操作方便,便于对芯片打线键合。

39.在一些实施例中,所述基板1上设有主控芯片13,所述主控芯片13与所述底层芯片2呈相对设置,所述主控芯片13通过第四贴片胶膜14与所述基板1连接。

40.采用上述实施例,其结构简单,操作方便,保证了芯片封装的稳定性。

41.在一些实施例中,所述主控芯片13上至少连接有一根金线12。

42.采用上述实施例,其结构简单,操作方便,便于对芯片打线键合。

43.底层芯片2旁边设有减少悬空假片5,减少悬空假片5的设置使得顶层芯片3打线键合区域有足够的受力点,避免打线键合过程中因顶层芯片3无支撑从而导致芯片裂片和翘边的异常问题出现,有效提升封装良率,在此基础上能同步满足顶层芯片更多层数堆叠,从而可以增加产品的容量。

44.基板1上方堆叠有多层顶层芯片3,底层芯片2的尺寸比顶层芯片3的尺寸差距过大使得悬空区域4的悬空面积较大,由于悬空区域4布满打线焊盘,打线过程中,悬空区域4会因为受力程度不同导致芯片翘边和裂片;本技术在顶层芯片3和基板1之间添加设有减少悬空假片5,减少悬空假片5设置于悬空区域4中,从而减小或去除悬空区域4的悬空面积,有效避免打线键合过程中因顶层芯片3无支撑从而导致芯片裂片和翘边的异常问题出现。

45.所述底层芯片2优选闪存芯片,所述顶层芯片3优选闪存芯片,所述减少悬空假片5优选硅片或铝片。

46.本实用新型提供的一种嵌入式多制层封装芯片,其结构简单,操作方便,解决了现有技术中底层芯片尺寸过小导致顶层芯片在打线过程中芯片存在裂片和翘边的技术问题,提高了芯片的封装良率。

47.可以理解,本实用新型是通过一些实施例进行描述的,本领域技术人员知悉的,在不脱离本实用新型的精神和范围的情况下,可以对这些特征和实施例进行各种改变或等效

替换。另外,在本实用新型的教导下,可以对这些特征和实施例进行修改以适应具体的情况及材料而不会脱离本实用新型的精神和范围。因此,本实用新型不受此处所公开的具体实施例的限制,所有落入本技术的权利要求范围各种改变或等效替换。另外,在本实用新型的教导下,可以对这些特征和实施例进行修改以适应具体的情况及材料而不会脱离本实用新型的精神和范围。因此,本实用新型不受此处所公开的具体实施例的限制,所有落入本技术的权利要求范围内的实施例都属于本实用新型所保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1