一种集成化的多引脚过压保护结构的制作方法

本技术涉及半导体集成电路,更具体的说是涉及一种集成化的多引脚过压保护结构。

背景技术:

1、集成电路的多个引脚通常会有各自允许的绝对最高额定电压值,当电压超过了该引脚的绝对最高额定电压值一定时间,就有可能会对内部电路造成永久性的功能或者可靠性损伤,但是在实际系统应用中,尤其应用在接口的集成电路,接口上的引脚不可避免的会遭遇到一些意外不可控的,超出该引脚最高电压额定值的瞬态高压,例如开关过冲,静电放电(esd)、系统浪涌残压等,这些都可能会对电路产生突然袭击造成电路损伤。这时为保护集成电路正常工作,就必须将瞬态电压钳位到一个安全的电压水平。目前常用的方式就是在引脚外部加入瞬态电压抑制器,它能在遭遇瞬态过压时以极快的速度把自身两端间的阻抗值由高阻抗变为低阻抗,吸收瞬间大电流,而且把它的两端电压箝制在一个预定的数值上,保护引脚里面的内部电路不受瞬态高压尖峰脉冲的冲击。而当芯片多个引脚需要保护时,就需要增加多个外置的瞬态电压抑制器。增加多个保护器件增加了系统的面积、成本和可靠性风险,不利于设备轻薄化的发展趋势。而将多个保护器件集成到芯片内部,实现最大程度集成化一直是接口类芯片需要解决的问题,一个现有技术的思路就是占用芯片自身有效面积增加平面保护器件构成的过压保护模块,例如在电路中额外增加浪涌检测电路模块以及一个浪涌钳位泄放高压mos管,利用浪涌检测电路模块在过压钳位值附近控制浪涌保护mos功率管的开启,实现电压钳位并泄放掉瞬态过压的能量,实现对内部电路的保护功能。但由于需要保护的瞬态过压泄放能量等级通常较大,就会需要非常大的芯片面积来实现过压保护模块,当需要保护多个不同电压管脚时,这种解决方案的面积效率更是捉襟见肘,保护器件会占用绝大部分芯片面积,而真正有效的集成电路的电路功能模块反而占用很小的一块面积,面积效率急剧降低,同时芯片成本也大大增加。

2、因此,如何经济有效地实现高面积效率的集成化的过压保护,是本领域技术人员亟需解决的问题。

技术实现思路

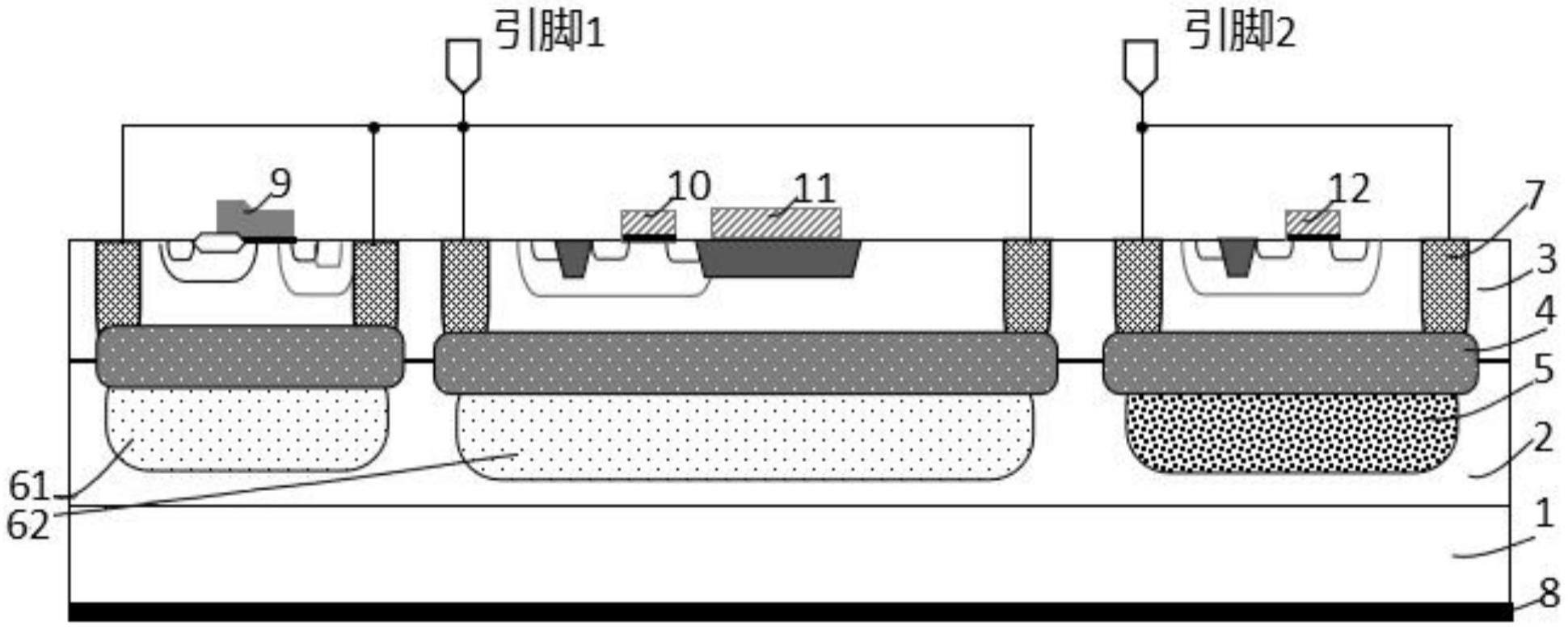

1、有鉴于此,本实用新型提出了一种解决集成电路的多个不同电压引脚的集成化的过压钳位保护的结构,不同于现有技术的增加芯片面积的表面器件实现钳位保护的方案,本实用新型的核心内容通过三维立体的形式,在集成电路的表面下方的n型埋层的下方,通过分次的光刻工艺和光刻后不同的p型掺杂注入条件,以及扩散工艺,形成不同钳位电压的过压钳位二极管,各个二极管的阳极公共接地端,通过浓掺杂的p型衬底从背面引出,不同的过压钳位二极管的阴极通过顶层的n阱或者浓掺杂的n-sinker接触到n型埋层并从表面引出。

2、具体的,为实现上述目的,本实用新型提供如下技术方案:

3、一种集成化的多引脚过压保护结构,在p型浓掺杂衬底上依次由下至上设置有缓冲p型外延层和顶层p型外延层;p型埋层位于缓冲p型外延层中,不同掺杂浓度的p型埋层使用publn表示,n为1~5的整数,代表不同的p型埋层形成的过压钳位二极管序号;n型埋层位于缓冲p型外延层和顶层p型外延层的交界处,使用nbl表示,n型埋层一部分在缓冲p型外延层,一部分反扩延伸至顶层p型外延层中;p型埋层位于n型埋层正下方。

4、可选的,nbl与不同掺杂浓度的publn形成具有不同雪崩击穿电压的过压钳位二极管,对不同额定最高电压的引脚进行过压钳位保护。

5、可选的,对同一引脚进行保护时可选用一个或多个相同雪崩击穿电压的过压钳位二极管;当选取多个相同雪崩击穿电压的过压钳位二极管对同一引脚进行保护时,多个相同雪崩击穿电压的过压钳位二极管之间需使用并联连接方式。

6、可选的,p型埋层publn与n型埋层nbl的交界处为各个过压钳位二极管的不同的pn结界面。

7、可选的,深n阱或浓掺杂的n-sinker层位于顶层p型外延层中,并与顶层p型外延层中的n型埋层接触,将构成过压钳位二极管阴极的n型埋层引出到顶层p型外延层表面,继而由表面的n+有源区引出。

8、可选的,构成过压钳位二极管阳极的各p型埋层publn均由减薄后的p型浓掺杂衬底背面淀积形成的背金层引出,背金材料为ti/ni/ag,减薄后的衬底的厚度为120um~300um,电位接在芯片的公共衬底地端。

9、可选的,所述p型浓掺杂衬底的电阻率范围为0.01ohm*cm~0.2ohm*cm,缓冲p型外延层的厚度范围为3um~20um,顶层p型外延层的电阻率范围为5ohm*cm~20ohm*cm,顶层p型外延层厚度范围为3um~10um。

10、可选的,publn的掺杂浓度由不同的注入剂量和能量条件来控制,注入剂量范围为1e13/cm2~5e15/cm2,热扩散工艺的范围为900℃~1100℃,高温热扩散时间为30~120分钟,最终publn与nbl交界处的掺杂浓度范围为2e16/cm3~5e18/cm3。

11、经由上述的技术方案可知,本实用新型公开提供了一种集成化的多引脚过压保护结构,与现有技术相比,具有以下有益效果:

12、本实用新型提出的对单芯片中的多个不同电压等级管脚钳位保护方案,不需要额外增加芯片面积,仅通过增加针对于每个电压等级的注入层次,实现可观的系统esd和过压,浪涌保护功能。本实用新型通过针对不同电压的管脚钳位保护需求,对于每个电压等级增加一个工艺层次和相应的注入条件,形成了内置于芯片n型埋层下方的体内钳位保护二极管,既节省了芯片外部的瞬态电压抑制二极管,节省了系统板面积,又不增加芯片自身面积,是一种高效率、低成本的解决esd、浪涌等过压电应力的集成化保护的创新方案,适合应用于目前的接口类集成电路产品。而且本实用新型结构自身的面积也可以方便调节,易于实现高等级的esd保护能力。

技术特征:

1.一种集成化的多引脚过压保护结构,其特征在于,在p型浓掺杂衬底上依次设置有缓冲p型外延层和顶层p型外延层;p型埋层位于缓冲p型外延层中,不同掺杂浓度的p型埋层使用publn表示;n型埋层位于缓冲p型外延层和顶层p型外延层的交界处,使用nbl表示;p型埋层位于n型埋层正下方。

2.根据权利要求1所述的一种集成化的多引脚过压保护结构,其特征在于,publn中的n为1~5的整数。

3.根据权利要求1所述的一种集成化的多引脚过压保护结构,其特征在于,nbl与不同掺杂浓度的publn形成具有不同雪崩击穿电压的过压钳位二极管,对不同额定最高电压的引脚进行过压钳位保护。

4.根据权利要求3所述的一种集成化的多引脚过压保护结构,其特征在于,多个相同雪崩击穿电压的过压钳位二极管对同一引脚进行保护时,多个相同雪崩击穿电压的过压钳位二极管之间使用并联连接方式。

5.根据权利要求1所述的一种集成化的多引脚过压保护结构,其特征在于,p型埋层与n型埋层的交界处为过压钳位二极管的pn结界面。

6.根据权利要求3所述的一种集成化的多引脚过压保护结构,其特征在于,深n阱或浓掺杂的n-sinker层位于顶层p型外延层中,并与顶层p型外延层中的n型埋层接触,将构成过压钳位二极管阴极的n型埋层引出到顶层p型外延层表面,继而由表面的n+有源区引出。

7.根据权利要求3所述的一种集成化的多引脚过压保护结构,其特征在于,构成过压钳位二极管阳极的各p型埋层publn均由减薄后的p型浓掺杂衬底背面淀积形成的背金层引出,背金材料为ti/ni/ag,减薄后的衬底的厚度为120um~300um,电位接在芯片的公共衬底地端。

8.根据权利要求1所述的一种集成化的多引脚过压保护结构,其特征在于,所述p型浓掺杂衬底的电阻率范围为0.01ohm*cm~0.2ohm*cm,缓冲p型外延层的厚度范围为3um~20um,顶层p型外延层的电阻率范围为5ohm*cm~20ohm*cm,顶层p型外延层厚度范围为3um~10um。

技术总结

本技术公开了一种集成化的多引脚过压保护结构,涉及半导体集成电路技术领域,该结构在P型浓掺杂衬底上依次向上设置有缓冲P型外延层和顶层P型外延层;P型埋层位于缓冲P型外延层中,不同掺杂浓度的P型埋层使用PUBLn表示;N型埋层位于缓冲P型外延层和顶层P型外延层的交界处,使用NBL表示;P型埋层位于N型埋层正下方;NBL与不同掺杂浓度的PUBLn形成具有不同雪崩击穿电压的过压钳位二极管,对不同额定最高电压的引脚进行过压钳位保护。本技术不需要额外增加芯片面积,仅通过增加针对于每个电压等级的注入层次,即可实现可观的系统ESD和过压,浪涌保护功能,节省了系统板面积,又不增加芯片自身面积。

技术研发人员:吕宇强,鞠建宏

受保护的技术使用者:上海帝迪集成电路设计有限公司

技术研发日:20221122

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!