一种芯片塑封体双面电镀结构的制作方法

本技术涉及半导体,具体涉及一种芯片塑封体双面电镀结构。

背景技术:

1、随着半导体领域的发展,微电子封装技术的高密度化已在新一代电子产品上逐渐成为主流。而不同的封装技术在制造工序和工艺方面差异很大,封装后对芯片自身性能的发挥也起到至关重要的作用。随着封装工艺和技术的发展,芯片向密度更高、速度更快、尺寸更小、成本更低等方向发展。而芯片塑封体的两面电镀则是现在封装工艺的一个关键环节,电镀效果的好坏直接影响芯片的性能和使用。

2、目前对芯片塑封体两面电镀的流程是分开的,即先对芯片塑封体一面进行电镀处理,再镀芯片塑封体的另一面进行电镀处理,该工艺流程复杂,成本高,良品率相对较低。

技术实现思路

1、本实用新型的目的在于提供一种芯片塑封体双面电镀结构,其制备方法相对简单,生产成本低,且良品率高。

2、为达此目的,本实用新型采用以下技术方案:

3、一方面,提供一种芯片塑封体双面电镀结构,包括:

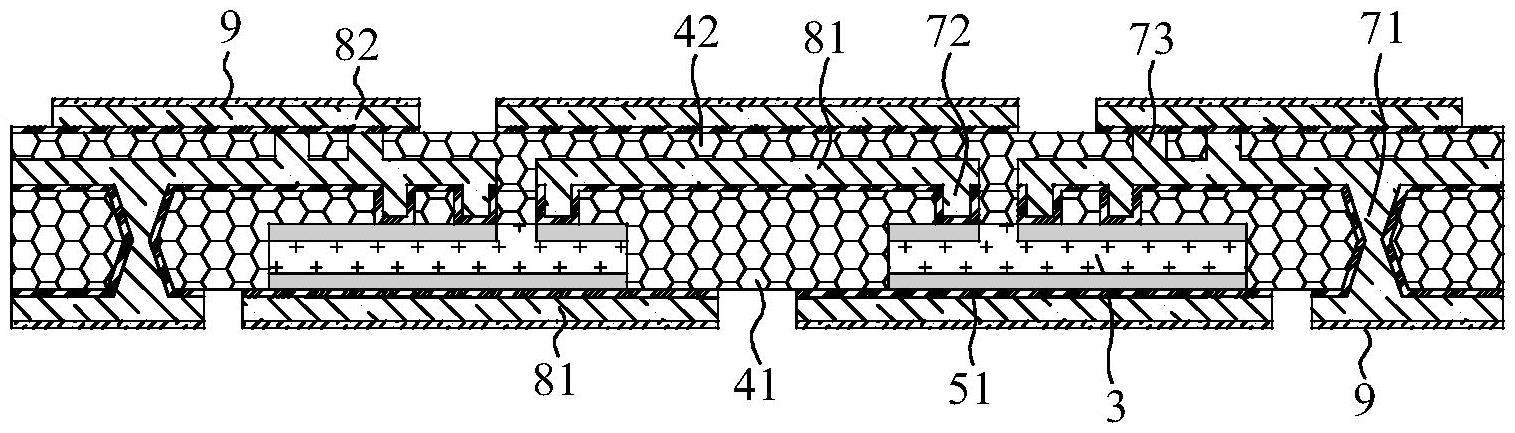

4、芯片塑封体,所述芯片塑封体包括若干芯片和包覆所述芯片的第一塑封层;所述芯片塑封体沿其厚度方向开设有贯穿所述芯片塑封体的若干通孔和使所述芯片的i/o口外露的若干盲孔;

5、位于所述通孔侧壁、所述盲孔侧壁以及所述芯片塑封体两侧的第一种子层;

6、填充于所述通孔内的第一导电柱、填充于所述盲孔内的第二导电柱以及位于所述芯片塑封体两侧的第一种子层上的第一重布线层;

7、所述芯片塑封体其中一侧的所述第一重布线层通过所述第二导电柱与所述芯片的i/o口连接,以及通过第一导电柱与另一侧的所述第一重布线层连接。

8、本实用新型中,芯片塑封体两侧的第一重布线层通过填充于芯片塑封体的通孔内的第一导电柱同步连接,从而实现功能芯片之间的信号互连和贯通。与现有技术相比,该芯片塑封体双面电镀结构的制备工艺流程简单,其生产效率高,生产成本低,且良品率也得到提高。

9、本实用新型中,芯片的数量为至少两个。

10、其中,通孔的第一导电柱、盲孔内的第二导电柱以及芯片塑封体两侧的第一重布线层为采用直流电镀或脉冲电镀方法通过双面电镀制得,从而实现芯片之间的信号互连和贯通。

11、作为芯片塑封体双面电镀结构的一种优选方案,所述通孔为x型通孔或垂直型通孔,优选为x型通孔。

12、作为芯片塑封体双面电镀结构的一种优选方案之一,还包括具有导电性的防氧化层,所述防氧化层位于所述芯片塑封体两侧的所述第一重布线层远离所述芯片塑封体的一侧。

13、作为芯片塑封体双面电镀结构的一种优选方案,所述芯片塑封体双面电镀结构还包括:

14、第三导电柱,所述第三导电柱位于芯片塑封体的其中一侧第一重布线层的一侧;

15、第二塑封层,所述第二塑封层位于该第一重布线层的一侧并包覆该第三导电柱,且第三导电柱的端面外露于第二塑封层;

16、位于所述第二塑封层一侧并与所述第三导电柱连接的第二种子层以及位于该第二种子层上的第二重布线层。

17、作为芯片塑封体双面电镀结构的一种优选方案,所述芯片塑封体双面电镀结构还包括:

18、介电层,所述第一塑封层的两侧分别具有一层所述介电层,且所述介电层位于所述第一塑封层与所述第一种子层之间。通过设置介电层可以提高产品的整体强度。

19、作为芯片塑封体双面电镀结构的一种优选方案之二,还包括具有导电性的防氧化层,所述防氧化层位于所述第二重布线层远离所述芯片塑封体的一侧以及位于远离所述第二重布线层的第一重布线层的一侧。

20、本实用新型中,上述芯片塑封体双面电镀结构的制备方法包括以下步骤:

21、s10、制备芯片塑封体,使芯片包裹于第一塑封层内;

22、s20、对芯片塑封体进行开孔处理,形成贯穿芯片塑封体的通孔和使芯片的i/o口外露的盲孔;

23、s30、通过双面电镀同步在通孔内制作第一导电柱、在盲孔内制作第二导电柱以及在芯片塑封体的双面同步制作与第一导电柱和第二导电柱连接的第一重布线层;

24、其中,所述双面电镀采用的是直流电镀或脉冲电镀。

25、本实用新型通过对芯片塑封体开通孔和盲孔,配合直流电镀或脉冲电镀,可以实现在芯片塑封体的通孔、盲孔内同步制作第一导电柱和第二导电柱,以及在芯片塑封体的两侧同步制作第一重布线层,从而实现功能芯片之间的信号互连和贯通。与现有的单面电镀相比,可缩短工艺流程,提升生产效率,降低成本,良品率也能得到相应的提高。

26、作为芯片塑封体双面电镀结构的制备方法的一种优选方案,所述通孔为x型通孔或垂直型通孔,均适用于采用直流电镀或脉冲电镀进行双面电镀。

27、优选地,通孔为x型通孔,可以进一步提高双面电镀效果,提高产品良率。

28、作为芯片塑封体双面电镀结构的制备方法的一种优选方案,步骤s10具体包括以下步骤:

29、s10a、提供载板和芯片,将所述芯片贴于所述载板上;

30、s10b、采用塑封料对所述芯片进行塑封,形成包覆所述芯片的第一塑封层;

31、s10c、拆除所述载板,制得所述芯片塑封体。

32、作为芯片塑封体双面电镀结构的制备方法的另一种优选方案,

33、步骤s10具体包括以下步骤:

34、s10a、提供载板和芯片,将所述芯片贴于所述载板上;

35、s10b、采用塑封料对所述芯片进行塑封,形成包覆所述芯片的第一塑封层;

36、s10c、拆除所述载板;

37、s10d、在第一塑封层的两侧分别制备介电层,制得所述芯片塑封体。

38、进一步地,s10a中,先将胶膜贴于载板的一侧,然后通过贴片机将芯片的正面(不限于正面,也可以为背面)固定在胶膜上;其中,载板材料可为sus、prepreg(bt)、fr4、fr5、glass、pp、emc、pi等;胶膜材料包括但不限于临时键合胶、daf膜、pi膜、干膜、abf膜以及类abf胶膜中的任一种。

39、进一步地,s10b中,塑封料材料包括但不限于emc、abf、pi、pp中的任一种。

40、进一步地,s10c中,需拆除载板,并使胶膜与芯片分离。

41、进一步地,s10d中,在第一塑封层的两侧分别制备介电层,制得所述芯片塑封体。

42、作为芯片塑封体双面电镀结构的制备方法的一种优选方案,步骤s20具体为:避开所述芯片的位置对芯片塑封体沿其厚度方向开设通孔以及在芯片塑封体对应芯片i/o口的位置开设使i/o口外露的盲孔。

43、具体地,采用钻孔工艺对塑封层开设上下贯通的通孔及延伸至芯片i/o口(输出端)的盲孔,所述钻孔工艺包括但不限于激光开孔、机械钻孔、掩膜覆盖plasma攻孔中的任一种。

44、作为芯片塑封体双面电镀结构的制备方法的一种优选方案,步骤s30具体包括以下步骤:

45、s30a、在所述通孔、盲孔的侧壁以及所述芯片塑封体沿其厚度方向的两侧制作第一种子层;

46、s30b、在位于所述芯片塑封体两侧的第一种子层上贴第一感光膜,并使该第一感光膜覆盖部分所述第一种子层;

47、s30c、采用直流电镀或脉冲电镀同步在通孔内、盲孔内以及芯片塑封体两侧的第一种子层上电镀,制得填充满通孔的第一导电柱、填充满盲孔的第二导电柱以及位于芯片塑封体两侧并与所述第一导电柱和所述第二导电柱连接的第一重布线层。

48、进一步地,在制作第一种子层之前,还需要将开孔之后的芯片塑封体在高真空状态进行加热,把芯片塑封体的水分及污染物去除,然后通过磁控溅射在双面制备具有高附着力、优良电导率及厚度均匀的ti-cu种子层。磁控溅射ti-cu种子层为本领域常规技术手段,具体不再赘述。而且,本实用新型中的第一种子层不限于ti-cu种子层,也可以为ti种子层。

49、制作第一种子层之后,在芯片塑封体两侧的第一种子层上贴第一感光膜,然后通过曝光、显影开设图形化窗口;

50、采用直流电镀或脉冲电镀同步在通孔内制备第一导电柱、在盲孔内制备第二导电柱以及图形化窗口内制备第一重布线层。

51、对于采用步骤s10-30制得的产品,还可以在该产品的两侧的第一重布线层远离芯片塑封体的一侧分别制作防氧化层,可以对第一重布线层起到防氧化作用,同时提高第一重布线层的导电性能。

52、具体地,该防氧化层采用镍钯金工艺制得,具有良好的抗氧化性和导电性。

53、作为芯片塑封体双面电镀结构的制备方法的一种优选方案,还包括步骤s40,具体包括以下步骤:

54、s40a、在芯片塑封体一侧的第一重布线层上贴第二感光膜,并使该第一重布线层部分外露于第二感光膜;具体地,通过曝光显影技术在第二感光膜上形成使第一重布线层部分外露于第二感光膜的图形化窗口;

55、s40b、通过电镀在该第一重布线层外露的位置(即图形化窗口)制作第三导电柱;

56、s40c、去除残留的第一感光膜和第二感光膜,并蚀刻掉外露的第一种子层;

57、s40d、采用塑封料对该第一重布线层和第三导电柱进行塑封处理,形成包覆该第一重布线层和第三导电柱的第二塑封层,并使第三导电柱远离第一重布线层的一端面外露于第二塑封层,具体地,采用减薄工艺对塑封料进行减薄处理,可以使第三导电柱裸露出来,该减薄工艺可以为plasma或者研磨等方法,具体不再赘述;

58、s40e、在第二塑封层上制作第二种子层,并使该第二种子层与第三导电柱连接;

59、s40f、在第二种子层上贴第三感光膜,并使部分第二种子层外露于第三感光膜;具体地,通过曝光显影技术在第三感光膜上形成使第二种子层部分外露于第三感光膜的图形化窗口;

60、s40g、在第二种子层外露于第三感光膜的一侧(即图形化窗口)通过电镀制作第二重布线层;

61、s40h、去除残留的第三感光膜并蚀刻掉第二种子层外露于第二重布线层的部分。

62、其中,第二种子层与第一种子层的制备工艺相同,可以为ti-cu种子层或者ti种子层。

63、作为芯片塑封体双面电镀结构的制备方法的另一种优选方案,还包括步骤s50、在所述第一重布线层和所述第二重布线层外露的一侧分别制作具有导电性的防氧化层,该防氧化层为通过镍钯金工艺制得的ni-pd-au膜。

64、本实用新型的有益效果:本实用新型通过对芯片塑封体开通孔和盲孔,配合直流电镀或脉冲电镀,可以实现在芯片塑封体的通孔、盲孔内同步制备第一导电柱和第二导电柱,以及在芯片塑封体的两侧同步制作第一重布线层,从而实现功能芯片之间的信号互连和贯通。与现有的单面电镀相比,缩短了工艺流程,提升了生产效率,降低了芯片塑封体双面电镀结构的生产成本,良品率也得到了相应的提高。

- 还没有人留言评论。精彩留言会获得点赞!