高压二极管的制作方法

本申请涉及半导体,具体涉及一种高压二极管。

背景技术:

1、高压二极管通常用在逆变器中,且是逆变器中不可或缺的部分,其起到电流换向后续流的重要作用,因此,高压二极管的反向恢复速度快慢直接影响到逆变器的最终效率。

2、现有的高压二极管通常是基于传统pin结构获得,并采用重金属掺杂技术控制寿命,但是,该高压二极管在高频率下工作,容易出现较严重的电磁干扰(electromagneticinterference,emi)噪声。

技术实现思路

1、鉴于此,本申请提供一种高压二极管,以降低emi噪声产生的风险的问题。

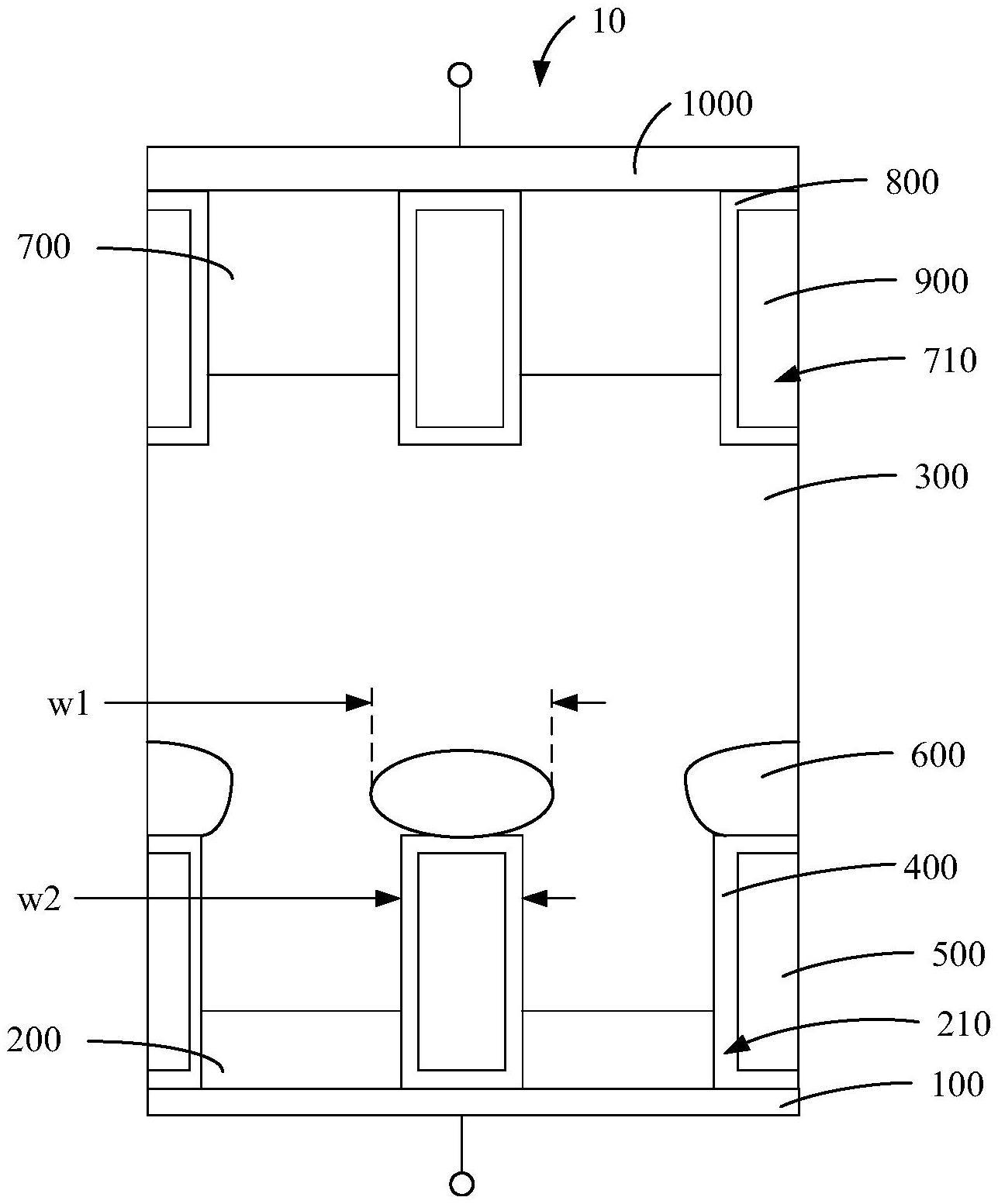

2、本申请提供的一种高压二极管,包括:

3、阴极;

4、n型半导体衬底,设置于所述阴极上;

5、n型半导体漂移层,设置于所述n型半导体衬底远离所述阴极的一侧;

6、第一氧化部,位于所述n型半导体衬底并延伸入部分所述n型半导体漂移层中;

7、第一p型掺杂部,设置于所述n型半导体漂移层中且与所述第一氧化部连接;

8、第二p型掺杂部,设置于所述n型半导体漂移层远离所述阴极的一侧;以及

9、阳极,设置于所述第二p型掺杂部远离所述阴极的一侧。

10、其中,所述第一p型掺杂部与所述第二p型掺杂部间隔设置。

11、其中,所述第一氧化部具有多个,所述第一p型掺杂部具有多个,每一所述第一p型掺杂部与一所述第一氧化部连接,每两相邻的所述第一p型掺杂部间隔设置。

12、其中,每两相邻的所述第一p型掺杂部之间的距离相等。

13、其中,所述第一p型掺杂部位于所述第一氧化部远离所述阴极的一侧。

14、其中,所述第一p型掺杂部为轻掺杂部。

15、其中,所述第一p型掺杂部的掺杂浓度为1e14cm-3~1e16cm-3。

16、其中,所述第二p型掺杂部为轻掺杂部。

17、其中,所述第二p型掺杂部的掺杂浓度为1e14cm-3~1e16cm-3。

18、其中,所述第一p型掺杂部的截面形状为椭圆形。

19、本申请公开一种高压二极管,包括阴极、n型半导体衬底、n型半导体漂移层、第一氧化部、第一p型掺杂部、第二p型掺杂部以及阳极,n型半导体衬底设置于阴极上,n型半导体漂移层设置于n型半导体衬底远离阴极的一侧,第一氧化部位于n型半导体衬底并延伸入部分n型半导体漂移层中,第一p型掺杂部设置于n型半导体漂移层中且与第一氧化部连接,第二p型掺杂部设置于n型半导体漂移层远离阴极的一侧,阳极设置于第二p型掺杂部远离阴极的一侧。在本申请中,通过在n型半导体漂移层中引入与第一氧化部连接的第一p型掺杂部,使得正向导通时,可以降低背面电子的注入效率,从而可降低正面空穴的有效注入,使得储存的载流子减少,开关速度加快;同时,在反向偏置时,在反向恢复过程中,反向恢复电流在达到反向峰值电流后的下降阶段,空穴会被不断抽取及复合导致载流子浓度降低,而第一p型掺杂部的设置,可以为该n型半导体漂移层提供持续的载流子,从而降低该反向恢复阶段内出现电流阶跃现象的风险,进一步降低电磁干扰噪声产生的风险,尤其在高电流的变化率(di/dt)反向恢复时,该结构抑制效果更优,从而保证了高压二极管的性能。

技术特征:

1.一种高压二极管,其特征在于,包括:

2.根据权利要求1所述的高压二极管,其特征在于,所述第一p型掺杂部与所述第二p型掺杂部间隔设置。

3.根据权利要求2所述的高压二极管,其特征在于,所述第一氧化部具有多个,所述第一p型掺杂部具有多个,每一所述第一p型掺杂部与一所述第一氧化部连接,每两相邻的所述第一p型掺杂部间隔设置。

4.根据权利要求3所述的高压二极管,其特征在于,每两相邻的所述第一p型掺杂部之间的距离相等。

5.根据权利要求4所述的高压二极管,其特征在于,所述第一p型掺杂部位于所述第一氧化部远离所述阴极的一侧。

6.根据权利要求5所述的高压二极管,其特征在于,所述第一p型掺杂部为轻掺杂部。

7.根据权利要求6所述的高压二极管,其特征在于,所述第一p型掺杂部的掺杂浓度为1e14cm-3~1e16cm-3。

8.根据权利要求7所述的高压二极管,其特征在于,所述第二p型掺杂部为轻掺杂部。

9.根据权利要求8所述的高压二极管,其特征在于,所述第二p型掺杂部的掺杂浓度为1e14cm-3~1e16cm-3。

10.根据权利要求1至9任一项所述的高压二极管,其特征在于,所述第一p型掺杂部的截面形状为椭圆形。

技术总结

本申请公开一种高压二极管,包括阴极、N型半导体衬底、N型半导体漂移层、第一氧化部、第一P型掺杂部、第二P型掺杂部以及阳极,N型半导体衬底设置于阴极上,N型半导体漂移层设置于N型半导体衬底远离阴极的一侧,第一氧化部位于N型半导体衬底并延伸入部分N型半导体漂移层中,第一P型掺杂部设置于N型半导体漂移层中且与第一氧化部连接,第二P型掺杂部设置于N型半导体漂移层远离阴极的一侧,阳极设置于第二P型掺杂部远离阴极的一侧。在本申请中,通过引入第一P型掺杂部,可以降低电磁干扰噪声产生的风险。

技术研发人员:李伟聪,伍济

受保护的技术使用者:深圳市威兆半导体股份有限公司

技术研发日:20221221

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!