具有优化的金属触点的锗光电二极管的制作方法

本发明的领域是包含优化的金属触点的由锗制造的钝化平面光电二极管(passivated planar photodiodes)的领域。本发明特别适用于检测近红外域中的光辐射的领域。

背景技术:

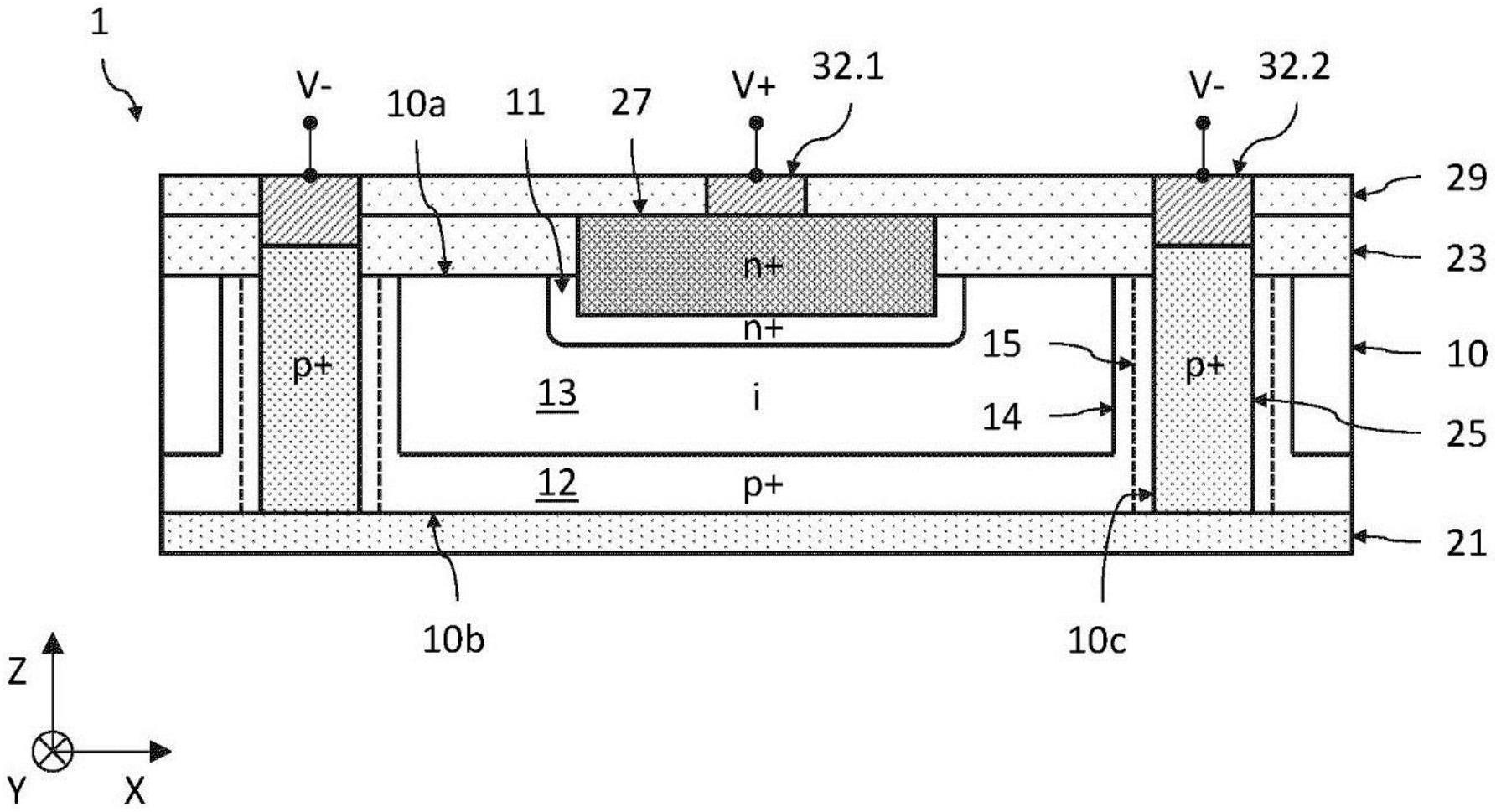

1、光电检测器件能够包括钝化平面光电二极管的矩阵。然后光电二极管沿着同一主平面在彼此相对且平行的第一表面和第二表面之间延伸。然后,它们各自包括检测部分,该检测部分由例如第一区域、第二区域和中间区域形成,第一区域由n掺杂锗制成并与第一表面齐平,第二区域由p掺杂锗制成并与第二表面齐平,中间区域由本征锗(intrinsicgermanium)或非常低的p掺杂锗制成并位于第一掺杂区域和第二掺杂区域之间。由介电材料制成的钝化层能够覆盖第一表面,以限制暗电流对每个光电二极管所测量的电流的贡献。

2、在钝化平面光电二极管的情况下,第一n掺杂区域和第二p掺杂区域的电偏置能够在第一表面的一侧进行。因此,外围半导体部分(例如由p掺杂的多晶硅制成)在光电二极管的主平面中围绕检测部分并与第二p掺杂区域接触。此外,设置在第一表面的一侧的金属触点与第一n掺杂区域和p掺杂外围半导体部分接触。

3、然而,由于在金属/锗界面处的费米能级钉扎,n掺杂锗上的金属触点似乎是整流型而不是欧姆型。然而,存在各种解决方案使金属/n掺杂锗触点为欧姆型。

4、因此,paramahans等人的题为“contacts on n-type germanium using variablydoped zinc oxide and highly doped indium tin oxide interfacial layers”,appl.phys.express 8,051302(2015)的文献中描述了在金属和n掺杂锗之间插入非常薄的介电层,例如,至少2nm厚的zno或者或至少2.4nm厚的ito。此外,wu等人的题为“contact ton-type ge with compositional ti nitride”appl.surf.sc.284,877-880(2013)的文献中描述了涉及制造tinx/n-ge型触点的另一种解决方案,其中x至少等于0.8以实现欧姆触点。然而,这些欧姆触点会是高阻性的,这降低了光电二极管的性能。

5、此外,文献ep 3657556 a1描述了一种由锗制成的钝化平面光电二极管,其中n掺杂多晶硅的插入半导体部分形成在检测部分上并与检测部分接触。插入半导体部分形成旨在扩散到锗中以产生第一n掺杂区域的n型掺杂剂的储存库。在插入半导体部分上生成金属触点,并且金属触点与插入半导体部分接触并允许对第一n掺杂区域进行电偏置。

6、然而,需要提供这种具有改进性能的钝化平面光电二极管。

技术实现思路

1、本发明的目的在于至少部分地克服现有技术的缺点,更具体地说,在于提出一种具有改进性能的钝化平面光电二极管。

2、为此,本发明的主题是一种光电二极管,包括:

3、-检测部分,其具有彼此相对且平行于主平面的第一表面和第二表面,由第一锗基晶体半导体材料制成,该检测部分包括:

4、o与第一表面齐平的第一n型掺杂区域;

5、o与第二表面齐平的第二p型掺杂区域;

6、o中间区域,其位于第一区域和第二区域之间并且在主平面中围绕第一区域;

7、-外围半导体部分,其由第二p型掺杂半导体材料制成,在主平面中围绕检测部分并与第二区域接触;

8、-插入半导体部分,其设置在检测部分的第一区域上并与第一区域接触;

9、-金属触点,其设置在第一表面的一侧,并适于一方面借助于插入半导体部分对第一区域进行电偏置,另一方面借助于外围半导体部分对第二区域进行电偏置。

10、根据本发明,该插入半导体部分由第三晶体半导体材料制成,第三晶体半导体材料制成具有与第一锗基半导体材料的天然晶格参数相等的天然晶格参数,误差在1%以内;以及比第一锗基半导体材料的带隙能量高至少0.5ev的带隙能量。

11、该光电二极管的一些优选但非限制性方面如下。

12、该插入半导体部分能够包含与第一区域中存在的那些n型掺杂剂相同的n型掺杂剂。

13、该插入半导体部分能够由iii-v族晶体半导体化合物制成,并且优选由alas或gaas制成。

14、该插入半导体部分能够位于检测部分的第一表面的凹口中,使得该插入半导体部分在主平面中被第一区域围绕。

15、金属触点中被称为中心金属触点的一个金属触点能够位于中间半导体部分上并与中间半导体部分接触。

16、该光电二极管能够包括位于插入半导体部分上并与插入半导体部分接触的上半导体部分,该上半导体部分由n型掺杂半导体材料制成,该n型掺杂半导体材料具有与插入半导体部分和第一区域的掺杂剂相同的掺杂剂。

17、金属触点中被称为中心金属触点的一个金属触点则能够位于上半导体部分上并与上半导体部分接触。

18、该上半导体部分能够由与外围半导体部分的材料相同的材料制成。

19、该上半导体部分和外围半导体部分能够由硅基半导体材料制成。然后,该光电二极管能包括与金属触点接触的硅化上部区域。

20、本发明还涉及一种制造根据上述任一特征所述的光电二极管的方法,包括以下步骤:

21、-生成包括第一子层和第二子层的堆叠,第一子层旨在形成第二区域,第二子层旨在形成中间区域;

22、-生成覆盖该堆叠的上绝缘层;

23、-生成穿过该堆叠和上绝缘层以出现在第一子层上的外围半导体部分;

24、-经由上绝缘层的开口通过从该堆叠的第二子层外延生长来生成插入半导体部分。

25、该方法能够包括在生成插入半导体部分的步骤之前,通过该开口在堆叠的第二子层中生成凹口的步骤,随后在该凹口中外延生长插入半导体部分。

26、当插入半导体部分在其外延生长过程中进行非故意掺杂时,该方法则能够包括以下步骤:

27、-生成n型掺杂上半导体部分;

28、-退火,其适于使上半导体部分中包含的掺杂剂扩散穿过插入半导体部分,以在检测部分中形成第一区域。

29、上半导体部分和外围半导体部分能够由相同的硅基材料制成。则该方法能够包括同时生成金属触点的步骤,一个金属触点与上半导体部分接触,并且另一个金属触点与外围半导体部分接触。

30、该插入半导体部分在其外延生长期间进行n型掺杂。则该方法能够包括以下步骤:生成金属触点,一个金属触点与该插入半导体部分接触,并且另一个金属触点与外围半导体部分接触。

技术特征:

1.一种光电二极管(1),包括:

2.如权利要求1所述的光电二极管(1),其中,所述插入半导体部分(27)包含与存在于第一区域(11)中的n型掺杂剂相同的n型掺杂剂。

3.如权利要求1或2所述的光电二极管(1),其中,所述插入半导体部分(27)由iii-v族晶体半导体化合物制成。

4.如权利要求3所述的光电二极管(1),其中,所述插入半导体部分(27)由alas或gaas制成。

5.如权利要求1至4中任一项所述的光电二极管(1),其中,所述插入半导体部分(27)位于所述检测部分(10)的第一表面(10a)的凹口中,使得所述插入半导体部分(27)在所述主平面中被第一区域(11)围绕。

6.如权利要求1至5中任一项所述的光电二极管(1),其中,所述金属触点中被称为中心金属触点的一个金属触点(32.1)位于所述中间半导体部分(27)上并与所述中间半导体部分(27)接触。

7.如权利要求1至5中任一项所述的光电二极管(1),包括位于所述插入半导体部分(27)上并与所述插入半导体部分(27)接触的上半导体部分(28),所述上半导体部分(28)由n型掺杂半导体材料制成,所述n型掺杂半导体材料具有与所述插入半导体部分(27)和第一区域(11)的掺杂剂相同的掺杂剂。

8.如权利要求7所述的光电二极管(1),其中,所述金属触点中被称为中心金属触点的一个金属触点(32.1)位于所述上半导体部分(28)上并与所述上半导体部分(28)接触。

9.如权利要求7或8所述的光电二极管(1),其中,所述上半导体部分(28)由与所述外围半导体部分(25)的材料相同的材料制成。

10.如权利要求7至9中任一项所述的光电二极管(1),其中,所述上半导体部分(28)和所述外围半导体部分(25)由硅基半导体材料制成,并且包括与所述金属触点(32.1、32.2)接触的硅化上部区域(31)。

11.一种用于制造如前述权利要求中任一项所述的光电二极管的方法,包括以下步骤:

12.如权利要求11所述的制造方法,包括:在生成所述插入半导体部分(27)的步骤之前,通过所述开口(26.1)在所述堆叠的第二子层(22.2)中生成凹口(26.2)的步骤,随后在所述凹口(26.2)中外延生长所述插入半导体部分(27)。

13.如权利要求11或12所述的制造方法,其中所述插入半导体部分(27)在其外延生长过程中进行非故意掺杂,所述方法包括以下步骤:

14.如权利要求13所述的制造方法,其中所述上半导体部分(28)和所述外围半导体部分(25)由相同的硅基材料制成,所述方法还包括以下步骤:

15.如权利要求11或12所述的制造方法,其中,所述插入半导体部分(27)在其外延生长过程中进行n型掺杂,所述方法包括以下步骤:

技术总结

本发明涉及一种光电二极管,包括:由第一锗基晶体半导体材料制成的检测部分10,检测部分10包括第一掺杂区域11、第二掺杂区域12和中间区域13;与第一掺杂区域11接触的间隙部分27,间隙部分27由晶体半导体材料制成,该晶体半导体材料具有等于第一半导体材料的天然晶格参数的天然晶格参数(误差在1%以内),并且具有比第一半导体材料的带隙能量高至少0.5eV的带隙能量。

技术研发人员:阿卜杜卡迪尔·阿利亚内,哈奇莱·卡亚

受保护的技术使用者:原子能和替代能源委员会

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!