填埋式三维扇出封装结构及其制备方法

本公开涉及半导体封装。更具体地,本公开总体上涉及一种填埋式三维扇出封装结构及其制备方法。

背景技术:

1、本部分提供了与本公开有关的背景信息,但是这些信息并不必然构成现有技术。

2、随着5g时代的到来,系统处理的数据急剧增多,这就要求电子器件具有更快的处理速度和更高的计算密度。而与之相反,随着芯片工艺走向7纳米、5纳米、3纳米甚至更超前,量子隧穿效应使得晶体管微缩变得十分困难。整个半导体产业都感到物理极限的逼近。在单片集成电路上容纳更多芯片变得越来越困难和昂贵。为此半导体行业寻求各种技术解决方案来提高成本性能,同时通过集成增加更多功能。此时,先进封装技术成为研究者感兴趣的方向。先进封装技术被认为是进一步提高算力密度的有效方法。先进封装不采用传统的封装工艺,比如说一般情况下先进封装不会采用传统封装里最常用的键合线(bondingwire),所以先进封装的集成度非常地高、封装体积很小。另外先进封装里面的互连线非常短,系统性能会提高很多。

3、近年来,先进封装技术随着芯片与电子器件中高性能、小尺寸、高可靠性以及超低功耗的要求而不断突破发展,同时随着人工智能、自动驾驶、5g网络、物联网等新兴产业的发展而向着系统集成、高速、高频、三维方向发展,特别地,三维(3d)集成先进封装的需求越来越强烈。为此,先进封装技术本身不断创新发展,以应对更加复杂的三维集成需求。当前,高密度硅通孔(tsv)技术/扇出(fan-out)封装技术由于其灵活性、高密度、适于系统集成,而成为目前先进封装的核心技术。其中,一个颇具吸引力的方案就是基于异构集成的扇出封装技术。异构集成的基本思想是使用先进的封装技术来将单独设计和制造的多个具有不同功能的电子部件集成到更高级别的组件(例如系统级封装,sip)中,总体上提供增强的功能和改进的操作特性。更高性能、更低延迟、更小尺寸、更轻重量、更低每个功能的功耗要求和更低成本是采用异构集成技术的关键驱动因素。这种技术能够持续增加功能密度并降低每个功能所需的成本,以保持电子产品的成本和性能进步,为消费者带来优势。

4、基于异构集成的扇出封装生产需求对光刻和补充工艺提出了挑战,要求它们以更高的标准执行,以支持所需的互连和硅通孔(through silicon via,tsv)处理层要求。在这里,设备成本和由于复杂性增加而降低的生产率或产量是制造商需要解决的挑战。在产量和工艺流程的进步之前,高端应用将从异构集成中获益。

5、目前在本领域中,将具有位于多个侧面不同位置处的管脚的芯片进行表面贴装(smt)是一种典型的扇出封装。为了适应目前的倒装焊工艺,需要将不同位置的管脚引导至同一平面。最常用的做法是采用打线的方式。即采用传统的打线工艺,将其他侧面上的管脚用引线引出,使其与某侧的管脚位于同一平面,随后再进行表面封装,将其贴装到封装基板。

6、这种方法,需要在倒装焊设备的基础上,另外添置打线设备,提高了成本,同时采用传统打线辅助表面封装的方式,与高密度先进封装的发展趋势不符。

7、因此,存在对于既能够符合高密度先进封装技术的发展趋势,又能够使成本降低的用以实现多面管脚芯片与另外的芯片之间的异构集成封装的方法。

技术实现思路

1、本部分提供本公开的一般概要,而不是本公开的全部范围或全部特征的全面披露。

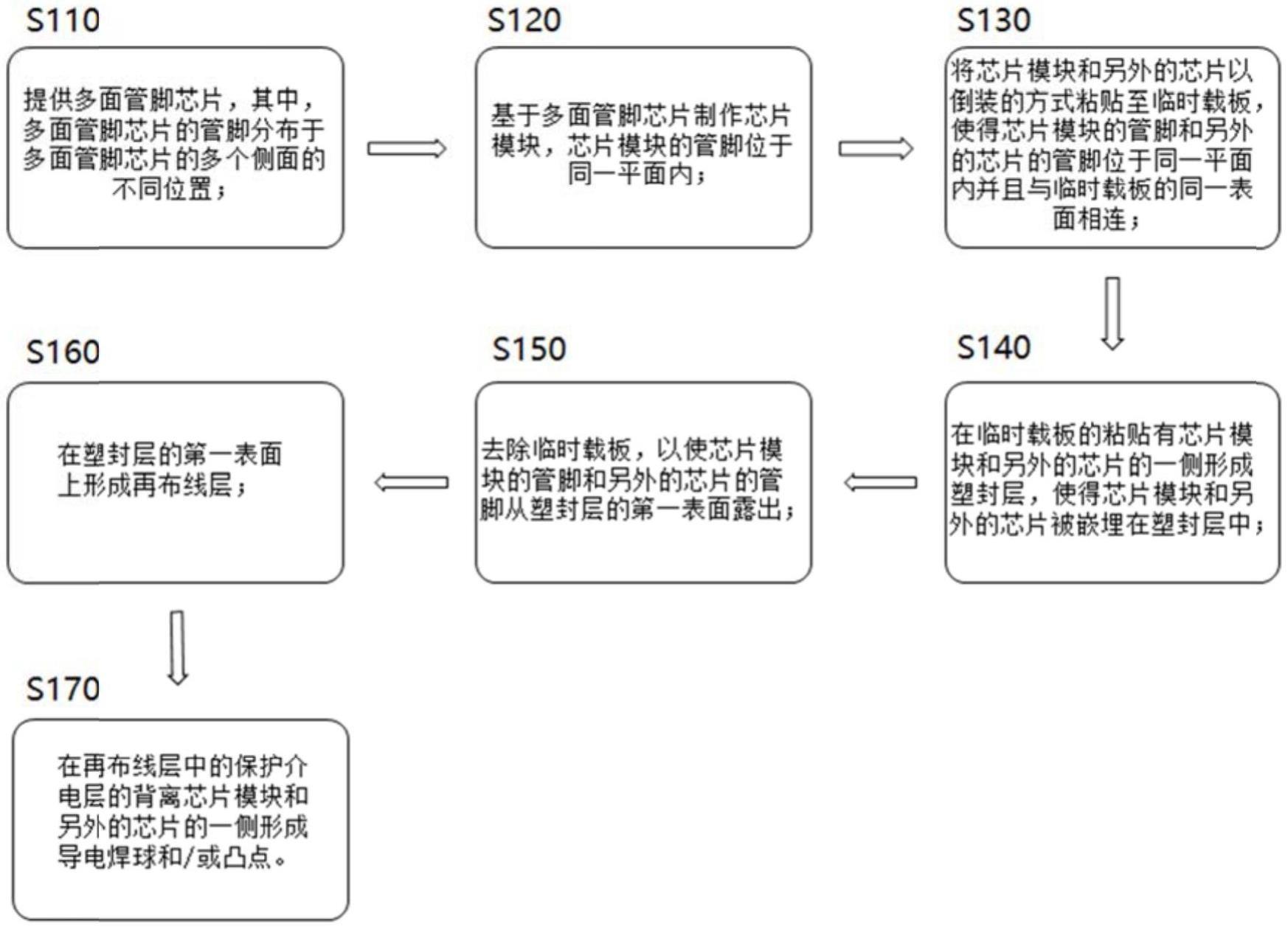

2、本公开的一方面提供了一种用于制备填埋式三维扇出封装结构的制备方法。所述用于制备填埋式三维扇出封装结构的制备方法可以包括下述步骤:提供多面管脚芯片,多面管脚芯片的管脚可以分布于多面管脚芯片的多个侧面的不同位置;基于多面管脚芯片制作芯片模块,芯片模块的管脚可以位于同一平面内;将芯片模块和另外的芯片以倒装的方式粘贴至临时载板,使得芯片模块的管脚和另外的芯片的管脚可以位于同一平面内并且与临时载板的同一表面相连;在临时载板的粘贴有芯片模块和另外的芯片的一侧形成塑封层,使得芯片模块和另外的芯片可以被嵌埋在塑封层中;去除临时载板,以使芯片模块的管脚和另外的芯片的管脚可以从塑封层的第一表面露出;在塑封层的第一表面上可以形成再布线层,再布线层可以包括与塑封层邻接的布线介电层、设置在布线介电层的背离芯片模块和另外的芯片的一侧的保护介电层、以及嵌设在布线介电层和保护介电层中并且与芯片模块和另外的芯片电连接的导电布线层,其中,导电布线层可以包括:分别与芯片模块的管脚和另外的芯片的管脚电连接的下管脚、连接芯片模块的管脚与另外的芯片的管脚的互连线、沿背离芯片模块和另外的芯片的方向分别从下管脚和互连线延伸并且与相应的下管脚和互连线电连接的第一金属柱、以及形成于第一金属柱的远离芯片模块和另外的芯片的一端并且与第一金属柱电连接的上管脚;以及,在再布线层中的保护介电层的背离芯片模块和另外的芯片的一侧可以形成导电焊球和/或凸点,其中,导电焊球和/或凸点可以穿过保护介电层而与导电布线层的上管脚电连接。

3、根据本公开所提供的用于制备填埋式三维扇出封装结构的制备方法,通过基于多面管脚芯片预先制作单独的芯片模块,并且使制成的芯片模块的管脚位于同一平面内,使得能够利用现有封装工艺实现多面管脚芯片与另外的芯片之间的异构集成封装,而不需要为多面管脚芯片的位于多个侧面不同位置处的管脚的引出而另外添置打线设备,降低了打线成本,同时也不需要采用传统打线辅助表面封装的方式,因而在满足了高密度先进封装的发展需求的同时,能够降低设备成本及生产成本。

4、在一些可选的实施方式中,基于多面管脚芯片制作芯片模块可以包括:提供绝缘框架;绝缘框架上可以形成延伸贯穿绝缘框架的第一槽和第二槽;提供底部设置有支撑基板的导电层结构;在导电层结构的与支撑基板相反的顶部可以形成第一粘结胶层;将形成有第一槽和第二槽的绝缘框架粘贴到第一粘结胶层的与导电层结构相反的一侧上;去除第一粘结胶层的经由第一槽和第二槽而暴露的部分,以露出导电层结构的与第一槽和第二槽的开口端相对的部分;在导电层结构的与第一槽的开口端相对的部分的表面上可以形成金属材料层,并且在金属材料层的与导电层结构相反的一侧上可以形成导电胶层;将多面管脚芯片通过导电胶层而粘贴在第一槽中,使得多面管脚芯片的至少一个侧面上的管脚与导电层结构电连接;以及用金属材料填充第二槽以形成与导电层结构电连接的第二金属柱,并且在第二金属柱的与导电层结构相反的端部处形成金属引脚,以用于将多面管脚芯片的管脚引导至同一平面以使得芯片模块的所有管脚位于同一平面内。

5、在一些可选的实施方式中,用于制备填埋式三维扇出封装结构的制备方法还可以包括:在基于多面管脚芯片制作芯片模块之后,提供散热框架;将芯片模块和另外的芯片固定地容置于散热框架中,使得芯片模块的管脚和另外的芯片的管脚位于同一平面内;将容置于散热框架中的芯片模块和另外的芯片以倒装的方式粘贴至临时载板,使得芯片模块的管脚和另外的芯片的管脚与临时载板的同一表面相连,而散热框架与临时载板间隔开;以及在临时载板的粘贴有芯片模块和另外的芯片的一侧形成塑封层,使得散热框架与芯片模块和另外的芯片一起被嵌埋在塑封层中。

6、在一些可选的实施方式中,将芯片模块和另外的芯片固定地容置于散热框架中可以包括:在散热框架的同一侧上形成底部封闭的芯片模块容置槽和芯片容置槽;在芯片模块容置槽的底部可以设置芯片模块粘结胶层,并且在芯片容置槽的底部可以设置芯片粘结胶层;通过芯片模块粘结胶层将芯片模块粘贴至芯片模块容置槽中,并且通过芯片粘结胶层将另外的芯片粘贴至芯片容置槽中,使得芯片模块的管脚和另外的芯片的管脚可以分别从芯片模块容置槽和芯片容置槽的开口端突出并且位于同一平面内。

7、在一些可选的实施方式中,用于制备填埋式三维扇出封装结构的制备方法中的散热框架可以是铜框架。

8、在一些可选的实施方式中,基于多面管脚芯片制作芯片模块可以包括:提供绝缘框架;在绝缘框架上可以形成延伸贯穿绝缘框架的第一槽;提供底部设置有支撑基板的导电层结构;在导电层结构的与支撑基板相反的顶部形成第一粘结胶层;将形成有第一槽的绝缘框架粘贴到第一粘结胶层的与导电层结构相反的一侧上;在第一粘结胶层的与第一槽的开口端相对的部分的表面上以及第一槽的侧壁表面上可以形成连续的金属材料层,并且在绝缘框架的围绕第一槽的开口端的表面上可以形成与金属材料层电连接的金属引脚,金属引脚用于将多面管脚芯片的管脚引导至同一平面以使得芯片模块的所有管脚位于同一平面内;在金属材料层的与第一槽的开口端相对的部分的表面上形成导电胶层;以及将多面管脚芯片通过导电胶层而粘贴在第一槽中,使得多面管脚芯片的至少一个侧面上的管脚可以与金属材料层电连接。

9、在一些可选的实施方式中,基于多面管脚芯片制作芯片模块可以包括:提供底部设置有支撑基板的导电层结构;在导电层结构的与支撑基板相反的顶部形成第一粘结胶层;在第一粘结胶层中形成延伸贯穿第一粘结胶层的导电胶容置槽,以露出导电层结构的与导电胶容置槽的开口端相对的部分;在导电胶容置槽中填充导电胶以形成导电胶层;以及将多面管脚芯片粘贴至导电胶层以形成芯片叠置件,其中,多面管脚芯片的至少一个侧面上的管脚经由导电胶层而与导电层结构电连接;并且,该制备方法可以包括:在塑封层的第一表面上形成再布线层之前,将芯片叠置件和另外的芯片以倒装的方式粘贴至临时载板,使得芯片叠置件的位于与导电层结构相反的一侧的管脚和另外的芯片的管脚位于同一平面内并且与临时载板的同一表面相连;在临时载板的粘贴有芯片叠置件和另外的芯片的一侧可以形成塑封层,使得芯片叠置件和另外的芯片可以被嵌埋在塑封层中;去除临时载板,以使芯片叠置件的位于与导电层结构相反的一侧的管脚和另外的芯片的管脚可以从塑封层的第一表面露出;围绕芯片叠置件在塑封层的第一表面上形成向内延伸穿过位于第一表面与芯片叠置件的导电层结构之间的塑封层和第一粘结胶层的连通孔;以及在该连通孔中可以填充金属材料以形成与导电层结构电连接的引导金属柱,该引导金属柱将多面管脚芯片的与导电层结构电连接的管脚引导成与芯片叠置件的从塑封层的第一表面露出的管脚位于同一平面内。

10、在一些可选的实施方式中,在塑封层的第一表面上形成再布线层可以包括:在塑封层的第一表面上的与暴露于第一表面的芯片模块的管脚和另外的芯片的管脚相对应的位置处,用金属材料可以形成下管脚和互连线;形成布线介电层,使得布线介电层可以覆盖下管脚和互连线以及第一表面;在布线介电层的与下管脚和互连线相对应的位置处形成第一通孔,使得第一通孔可以延伸穿过布线介电层直至下管脚和互连线;用金属材料填充第一通孔以形成第一金属柱,使得第一金属柱可以与下管脚和互连线电连接;用金属材料在第一金属柱的与塑封层相反的端部处形成上管脚,使得上管脚与第一金属柱电连接且部分地突出到布线介电层上方;形成保护介电层,使得保护介电层可以覆盖上管脚和布线介电层;以及在保护介电层的对应于上管脚的位置处形成开孔,使得开孔延伸穿过保护介电层并使上管脚露出。

11、在一些可选的实施方式中,用于制备填埋式三维扇出封装结构的制备方法中的布线介电层和保护介电层可以是通过旋涂或沉积而形成的。

12、在一些可选的实施方式中,用于制备填埋式三维扇出封装结构的制备方法中的导电焊球可以是采用导电焊球或模板印刷形成的,以及凸点可以是通过蒸镀、溅射形成的。

13、在一些可选的实施方式中,用于制备填埋式三维扇出封装结构的制备方法中的槽、通孔、连通孔和/或开孔可以是使用光刻和化学蚀刻中的至少一者而形成的。

14、在一些可选的实施方式中,用于制备填埋式三维扇出封装结构的制备方法中的下管脚、互连线和/或上管脚可以是用金属材料通过电镀方式形成的。

15、在一些可选的实施方式中,用于制备填埋式三维扇出封装结构的制备方法中的金属材料可以包括铜、铝、银或金中的至少一种。

16、本公开的另一方面提供了一种根据上述的制备方法制成的填埋式三维扇出封装结构。根据本公开的填埋式三维扇出封装结构可以包括:塑封层,该塑封层可以包括第一表面和与第一表面相反的第二表面;嵌埋在塑封层的第一表面中的芯片模块和另外的芯片,其中,芯片模块可以包括多面管脚芯片,多面管脚芯片可以具有分布于多个侧面的不同位置的管脚,多面管脚芯片的管脚可以经由引导金属柱而被引导至同一平面内,使得芯片模块的管脚和另外的芯片的管脚与塑封层的第一表面位于同一平面内;再布线层,该再布线层可以设置在塑封层的第一表面上,再布线层可以包括与塑封层邻接的布线介电层、设置在布线介电层的背离芯片模块和另外的芯片的一侧的保护介电层、以及嵌设在布线介电层和保护介电层中并且与芯片模块和另外的芯片电连接的导电布线层,其中,导电布线层可以包括:分别与芯片模块的管脚和另外的芯片的管脚电连接的下管脚、连接芯片模块的管脚与另外的芯片的管脚的互连线、沿背离芯片模块和另外的芯片的方向分别从下管脚和互连线延伸并且与相应的下管脚和互连线电连接的第一金属柱、以及形成于第一金属柱的远离芯片模块和另外的芯片的一端并且与第一金属柱电连接的上管脚;以及导电焊球和/或凸点,导电焊球和/或凸点可以设置在再布线层中的保护介电层的背离芯片模块和另外的芯片的一侧并且穿过保护介电层而与导电布线层的上管脚电连接。

17、在一些可选的实施方式中,芯片模块可以包括:底部设置有支撑基板的导电层结构;形成于导电层结构的与支撑基板相反的顶部的第一粘结胶层;粘贴在第一粘结胶层的与导电层结构相反的一侧上的绝缘框架,其中,绝缘框架可以形成有贯穿绝缘框架的第一槽和第二槽,并且在第一粘结胶层的与第一槽和第二槽的开口端相对的部分可以分别形成有贯穿第一粘结胶层的第一粘结胶层通孔和第二粘结胶层通孔;填充在第一粘结胶层通孔中并且与导电层结构电连接的金属材料层;形成于金属材料层的与导电层结构相反的一侧上的导电胶层;通过导电胶层而粘贴在第一槽中的多面管脚芯片,其中,多面管脚芯片的至少一个侧面上的管脚可以经由导电胶层和金属材料层而与导电层结构电连接;填充在绝缘框架的第二槽和第二粘结胶层通孔中的第二金属柱,以及形成于第二金属柱的与导电层结构相反的端部处的金属引脚,用于将多面管脚芯片的管脚引导至同一平面,以使得芯片模块的所有管脚位于同一平面内。

18、在一些可选的实施方式中,所述填埋式三维扇出封装结构还可以包括散热框架,散热框架与芯片模块和另外的芯片可以一起被嵌埋在塑封层中,其中,散热框架包括在散热框架的同一侧上形成的底部封闭的芯片模块容置槽和芯片容置槽,在芯片模块容置槽的底部可以设置有芯片模块粘结胶层,并且在芯片容置槽的底部可以设置有芯片粘结胶层,芯片模块通过芯片模块粘结胶层而被粘贴至芯片模块容置槽中,另外的芯片通过芯片粘结胶层而被粘贴至芯片容置槽中,芯片模块的管脚和另外的芯片的管脚可以分别从芯片模块容置槽和芯片容置槽的开口端突出并且位于同一平面内。

19、在一些可选的实施方式中,填埋式三维扇出封装结构中的散热框架可以是铜框架。

20、在一些可选的实施方式中,芯片模块可以包括:底部设置有支撑基板的导电层结构;形成于导电层结构的与支撑基板相反的顶部的第一粘结胶层;粘贴在第一粘结胶层上的与导电层结构相反的一侧上的绝缘框架,其中,绝缘框架可以形成有贯穿绝缘框架的第一槽;形成于第一粘结胶层的与第一槽的开口端相对的部分的表面上以及第一槽的侧壁表面上的连续的金属材料层,和在绝缘框架的围绕第一槽的开口端的表面上形成的与金属材料层电连接的金属引脚;在金属材料层的与第一槽的开口端相对的部分的表面上形成的导电胶层;以及多面管脚芯片,多面管脚芯片可以通过导电胶层而粘贴在第一槽中,使得多面管脚芯片的至少一个侧面上的管脚与金属材料层电连接。

21、在一些可选的实施方式中,芯片模块可以包括:芯片叠置件,芯片叠置件可以包括:底部设置有支撑基板的导电层结构;形成于导电层结构的与支撑基板相反的顶部的第一粘结胶层,在第一粘结胶层中可以形成有贯穿第一粘结胶层的导电胶容置槽;形成于导电胶容置槽中的导电胶层;以及多面管脚芯片,多面管脚芯片可以通过导电胶层而粘贴在导电层结构上,使得多面管脚芯片的至少一个侧面上的管脚可以与导电层结构电连接,且多面管脚芯片的位于与导电层结构相反的一侧上的管脚可以从塑封层的第一表面露出且与第一表面位于同一平面中;围绕芯片叠置件设置的引导金属柱,该引导金属柱将多面管脚芯片的与导电层结构电连接的管脚引导成与芯片叠置件的从塑封层的第一表面露出的管脚位于同一平面内,其中,引导金属柱从导电层结构延伸并穿过形成于第一粘结胶层中的第一粘结胶层通孔以及介于第一表面与导电层结构之间的塑封层。

22、在一些可选的实施方式中,填埋式三维扇出封装结构中的金属材料可以包括铜、铝、银或金中的至少一种。

23、根据本公开的实施方式所提供制备方法而制备出的填埋式三维扇出封装结构具有更高性能、更低延迟、更小尺寸、更轻重量、更低每个功能的功耗要求和更低成本。

- 还没有人留言评论。精彩留言会获得点赞!