包括具有超晶格的接地平面层的射频(RF)半导体装置及相关联的方法与流程

本公开一般而言涉及半导体装置,并且更具体地涉及射频(rf)半导体装置和相关方法。

背景技术:

1、已提出诸如通过增强电荷载流子的迁移率来增强半导体装置性能的结构和技术。例如,currie等人的美国专利申请no.2003/0057416公开了硅的应变材料层、硅-锗和弛豫硅,并还包括原本会造成性能下降的无杂质区。上部硅层中所得的双轴应变改变了载流子迁移率,从而实现较高速度和/或较低功率的装置。fitzgerald等人的公开的美国专利申请no.2003/0034529公开了一种同样基于类似应变硅技术的cmos反相器。

2、takagi的美国专利no.6,472,685b2公开了一种包括夹在硅层之间的硅和碳层使得第二硅层的导带和价带受到拉伸应变的半导体装置。具有较小的有效质量且已由施加到栅极电极的电场感应的电子被约束在第二硅层中,因此,n沟道mosfet被断言为具有较高的迁移率。

3、ishibashi等人的美国专利no.4,937,204公开了一种其中交替地外延生长多个层(少于八个单层,并包含部分或二元或二元化合物半导体层)的超晶格。主电流流动的方向垂直于超晶格的层。

4、wang等人的美国专利no.5,357,119公开了一种si-ge短周期超晶格,该si-ge短周期超晶格具有通过减少超晶格中的合金散射而实现的较高的迁移率。按照这些原则,candelaria的美国专利no.5,683,934公开了一种包括沟道层的迁移率增强的mosfet,该沟道层包括以将沟道层置于拉伸应力下的一定百分比替代地存在于硅晶格中的硅和第二材料的合金。

5、tsu的美国专利no.5,216,262公开了一种包括两个势垒区和夹在势垒之间的外延生长的薄半导体层的量子阱结构。每个势垒区由厚度通常在2至6个单层的范围内的sio2/si的交替层组成。硅的更厚部分夹在势垒之间。

6、同样tsu于2000年9月6日在applied physics and materials science&processing的第391至402页在线发表的题目为“phenomena in silicon nanostructuredevices”的文章公开了硅和氧的半导体-原子超晶格(sas)。si/o超晶格被公开为在硅量子和发光装置中是有用的。具体地,构建和测试了绿色电致发光二极管结构。二极管结构中电流流动是垂直的,即,垂直于sas的层。公开的sas可以包括由诸如氧原子和co分子之类的吸附物质分开的半导体层。超出吸附的氧单层的硅生长被描述为具有相当低缺陷密度的外延。一种sas结构包括大约为8个硅原子层的1.1nm厚的硅部分,并且另一种结构是该硅厚度的两倍。luo等人的在physical review letters的第7期,第89卷(2002年8月12日)中发表的题目为“chemical design of direct-gap light-emitting silicon”的文章进一步讨论了tsu的发光sas结构。

7、wang等人的美国专利no.7,105,895公开了薄硅和氧、碳、氮、磷、锑、砷或氢的势垒构成块,从而使垂直流过晶格的电流降低了超过四个数量级。绝缘层/势垒层允许临接绝缘层沉积低缺陷外延硅。

8、mears等人的公开的英国专利申请2,347,520公开了非周期性光子带隙(apbg)结构的原理可以适用于电子带隙工程。具体地,该申请公开了可以设定材料参数(例如,带极小值的位置、有效质量等)以产生具有期望的能带结构特性的新的非周期性材料。公开了诸如电导率、热导率和介电常数或磁导率之类的其它参数也可以被设计到材料中。

9、此外,wang等人的美国专利no.6,376,337公开了一种制作半导体装置的绝缘或势垒层的方法,该方法包括在硅衬底上沉积硅和至少一个附加元素的层,由此沉积的层基本上没有缺陷,使得可以在沉积的层上沉积基本上没有缺陷的外延硅。可替换地,一种或多种元素(优选地,包括氧)的单层被吸附在硅衬底上。夹在外延硅之间的多个绝缘层形成势垒复合物。

10、尽管存在这样的方法,但对于使用先进的半导体材料和处理技术以在半导体装置中实现改进的性能,进一步的增强会是期望的。

技术实现思路

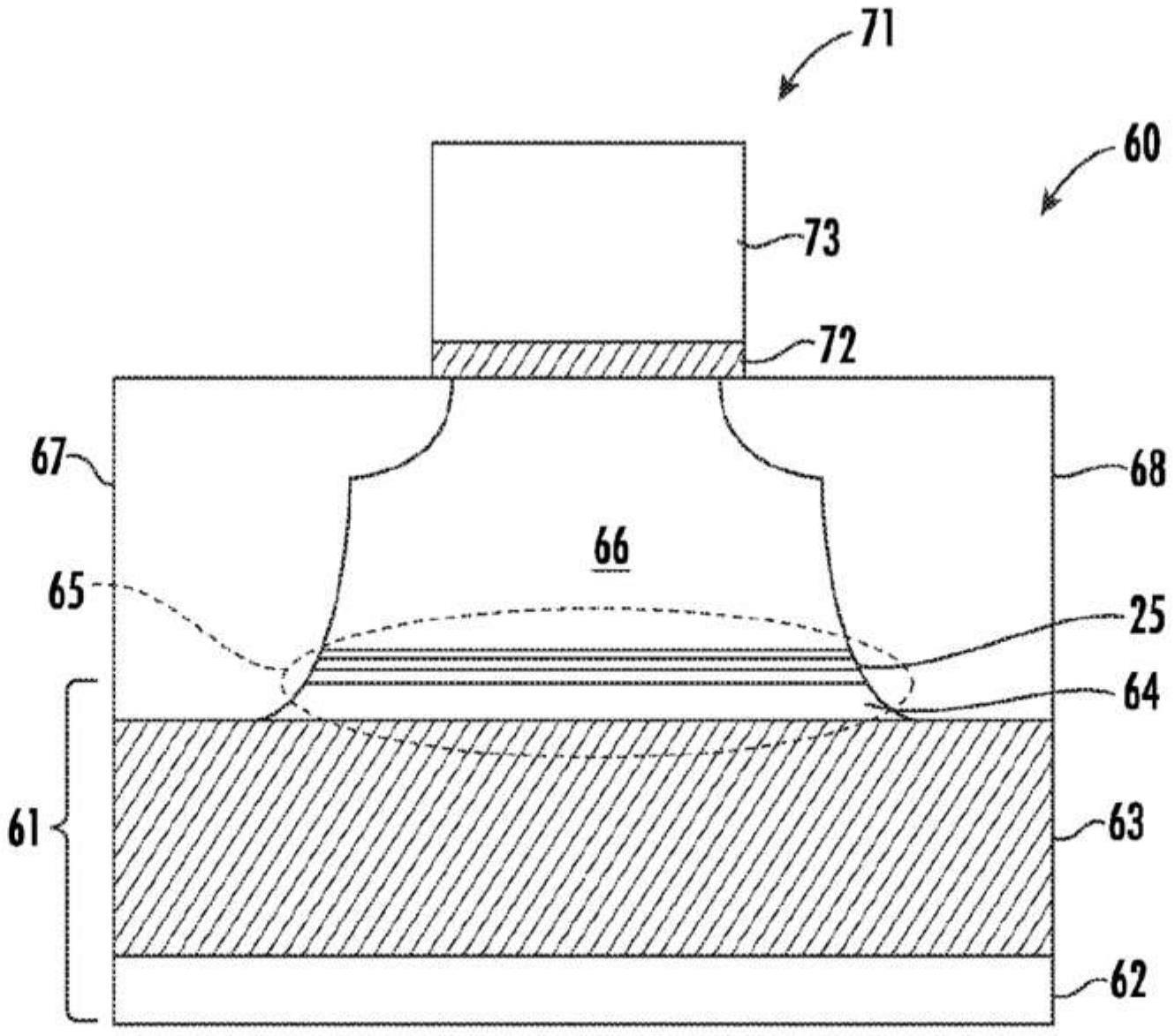

1、射频(rf)半导体装置可以包括绝缘体上半导体基板,以及在绝缘体上半导体基板上的包括导电超晶格的rf接地平面层。导电超晶格可以包括多个堆叠的层组,每个层组包括定义掺杂的基础半导体部分的多个堆叠的掺杂的基础半导体单层,以及被约束在相邻的掺杂的基础半导体部分的晶格内的至少一个非半导体单层。rf半导体装置还可以包括rf接地平面层之上的主体、与主体相邻并定义主体中的沟道区域的间隔开的源极和漏极区域,以及覆盖沟道区域的栅极。

2、在示例实施例中,rf半导体装置可以是rf开关。rf半导体装置还可以包括耦合到主体和rf接地平面层的主体触点。举例来说,主体触点可以包括与沟道区域的相对端相邻的第一和第二主体接触部分。

3、根据示例实施方式,rf接地平面可以具有在10-50nm范围内的厚度。此外,掺杂的基础半导体部分可以具有例如至少5×1017cm-3的掺杂剂浓度。栅极可以包括在沟道区域上方的栅极绝缘体和栅极绝缘体上方的栅极电极。

4、还举例来说,掺杂的基础半导体单层可以包括硅,并且非半导体单层可以包括氧。例如,绝缘体上半导体基板可以包括绝缘体上硅(soi)基板。

5、方法方面是用于制造射频(rf)半导体装置,该rf半导体装置可以包括在绝缘体上半导体基板上形成rf接地平面层,该rf接地平面层包括导电超晶格。导电超晶格可以包括多个堆叠的层组,每个层组包括定义掺杂的基础半导体部分的多个堆叠的掺杂的基础半导体单层,以及被约束在相邻的掺杂的基础半导体部分的晶格内的至少一个非半导体单层。该方法还可以包括在rf接地平面层之上形成主体,形成与主体相邻并定义主体中的沟道区域的间隔开的源极和漏极区域,以及形成覆盖沟道区域的栅极。

6、在示例实施例中,rf半导体装置可以包括rf开关。该方法还可以包括形成耦合到主体和rf接地平面层的主体触点。更具体地,主体触点可以包括与沟道区域的相对端相邻的第一和第二主体接触部分。

7、举例来说,rf接地平面可以具有在10-50nm范围内的厚度。还举例来说,掺杂的基础半导体部分可以具有至少5×1017cm-3的掺杂剂浓度。形成栅极可以包括在沟道区域上方形成栅极绝缘体,以及在栅极绝缘体上方形成栅极电极。

8、在示例实施方式中,掺杂的基础半导体单层可以包括硅,并且非半导体单层可以包括氧。而且,绝缘体上半导体基板可以包括例如绝缘体上硅(soi)基板。

技术特征:

1.一种射频rf半导体装置,包括:

2.如权利要求1所述的rf半导体装置,其中rf半导体装置包括rf开关。

3.如权利要求1所述的rf半导体装置,还包括耦合到主体和rf接地平面层的主体触点。

4.如权利要求3所述的rf半导体装置,其中主体触点包括与沟道区域的相对端相邻的第一主体接触部分和第二主体接触部分。

5.如权利要求1所述的rf半导体装置,其中rf接地平面具有在10-50nm范围内的厚度。

6.如权利要求1所述的rf半导体装置,其中掺杂的基础半导体部分具有至少5×1017cm-3的掺杂剂浓度。

7.如权利要求1所述的rf半导体装置,其中栅极包括沟道区域上方的栅极绝缘体以及栅极绝缘体上方的栅极电极。

8.如权利要求1所述的rf半导体装置,其中掺杂的基础半导体单层包括硅。

9.如权利要求1所述的rf半导体装置,其中非半导体单层包括氧。

10.如权利要求1所述的rf半导体装置,其中绝缘体上半导体基板包括绝缘体上硅soi基板。

11.一种用于制造射频rf半导体装置的方法,包括:

12.如权利要求11所述的方法,其中rf半导体装置包括rf开关。

13.如权利要求11所述的方法,包括形成耦合到主体和rf接地平面层的主体触点。

14.如权利要求13所述的方法,其中主体触点包括与沟道区域的相对端相邻的第一主体接触部分和第二主体接触部分。

15.如权利要求11所述的方法,其中rf接地平面具有在10-50nm范围内的厚度。

16.如权利要求11所述的方法,其中掺杂的基础半导体部分具有至少5×1017cm-3的掺杂剂浓度。

17.如权利要求11所述的方法,其中形成栅极包括在沟道区域上方形成栅极绝缘体,以及在栅极绝缘体上方形成栅极电极。

18.如权利要求11所述的方法,其中掺杂的基础半导体单层包括硅。

19.如权利要求11所述的方法,其中非半导体单层包括氧。

20.如权利要求11所述的方法,其中绝缘体上半导体基板包括绝缘体上硅soi基板。

技术总结

一种射频(RF)半导体装置可以包括绝缘体上半导体基板和在绝缘体上半导体基板上的包括导电超晶格的RF接地平面层。导电超晶格可以包括堆叠的层组,每个层组包括定义掺杂的基础半导体部分的堆叠的掺杂的基础半导体单层,以及约束在相邻的掺杂的基础半导体部分的晶格内的至少一个非半导体单层。RF半导体装置还可以包括RF接地平面层之上的主体、与主体相邻并定义主体中的沟道区域的间隔开的源极区域和漏极区域,以及覆盖沟道区域的栅极。

技术研发人员:武内英树,R·J·米尔斯

受保护的技术使用者:阿托梅拉公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!