接合体的制造方法、半导体器件的制造方法及树脂组合物与流程

本发明涉及一种接合体的制造方法、半导体器件的制造方法及树脂组合物。

背景技术:

1、移动电话或平板电脑型终端等电子设备逐渐小型化,另一方面其功能逐渐多样化。为了应对该需求,对组装到电子设备的电子电路要求进一步小型化·高集成化·高密度安装。作为实现多功能且维持高性能和可靠性并且小型化的技术,sip(system inpackage:封装体系)、mcm(multi chip module:多芯片模块)、pop(package on package:封装堆叠)等安装技术受到关注。根据这些技术,能够减少零件数量并简化半导体制造工序,因此从降低电子设备成本的观点考虑也可期待。

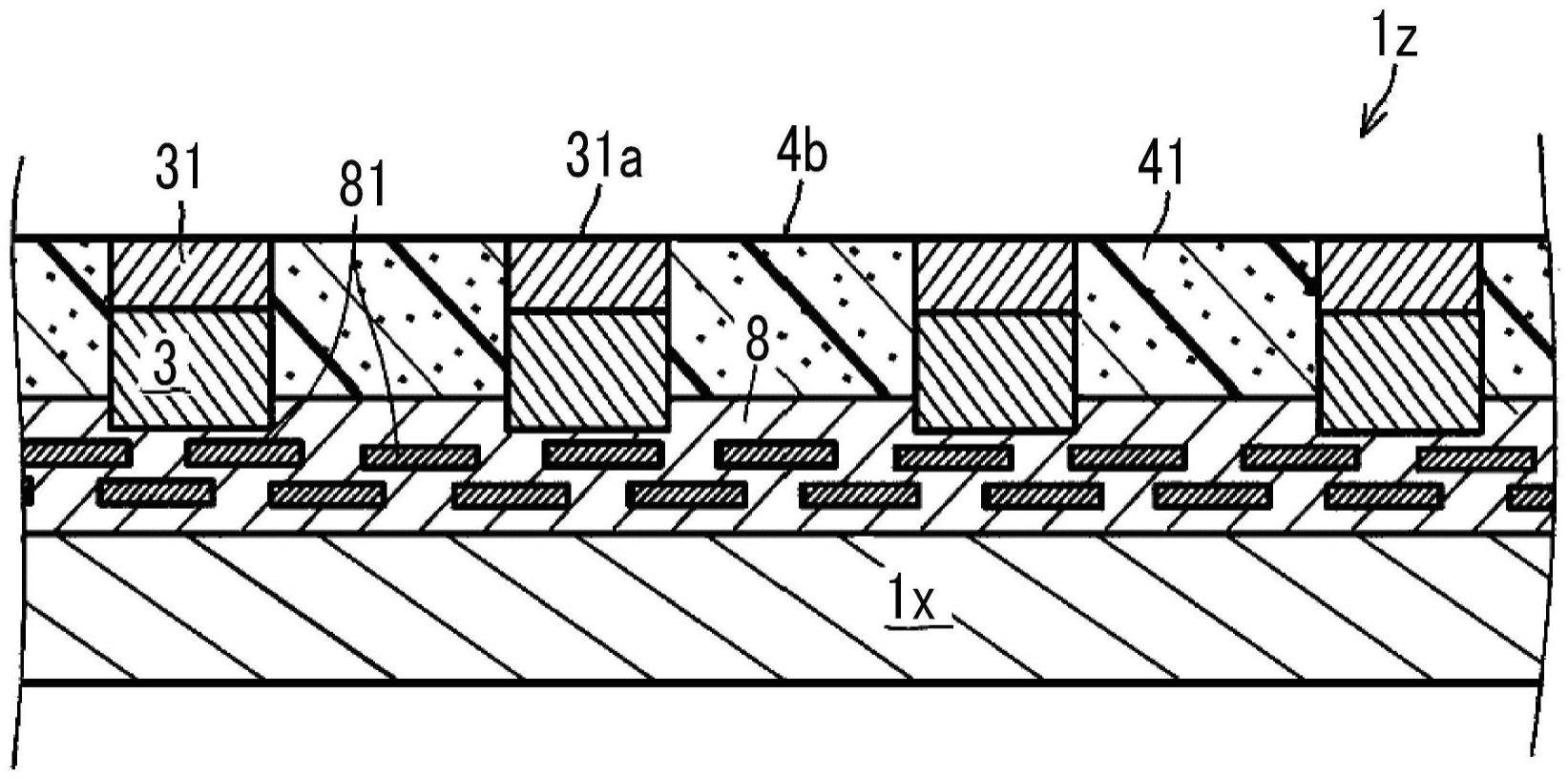

2、其中,在sip中通过焊线将各芯片之间进行连接,因此难以获得与以往的soc(system on chip:系统芯片)相同的处理速度。并且,在制造工序中通过焊线的连接也为复杂,希望也对产品成本或产品质量进行改善。作为与这种问题对应,已开发coc(chip onchip:芯片上芯片)的安装技术。在coc中,由于能够通过倒装芯片接合来连接芯片之间并缩短传输距离,因此能够获得与soc相同的高速性能。图1是表示通常的coc的结构的剖视图。该例子中的coc为通过具备子芯片(第1基板)1及母芯片(第2基板)2而成。在母芯片2上形成有电子电路(未图示)及倒装芯片电极(未图示),子芯片1经由焊锡电极(凸块)93来支承并连接。焊锡电极93的周围被底部填充剂94填充以确保绝缘性。母芯片2通过粘合膜91粘接于底板98而维持绝缘性地的同时进行搭载。该电连接经由焊线盘97b、焊线96及基板电极97a来进行。这种coc结构被密封树脂95密封而构成半导体器件90。该半导体器件90中设置有焊球99,并经由该焊球组装到电子设备中。并且,进一步应用该倒装芯片安装的技术,研究了与使用了tsv(through silicon via:硅穿孔)的三维安装相关的技术及其材料(非专利文献1)。

3、以往技术文献

4、非专利文献

5、非专利文献1:using permanent and temporary polyimide adhesives in 3d-tsv processing to avoid thin wafer handling(journal of microelectronics andelectronic packaging(2010)7,pp.214-219

技术实现思路

1、发明要解决的技术课题

2、在如上述图1所述的结构的coc结构的元件中,在用焊锡凸块93连接并固定子芯片1和母芯片2之后,在其间隙中填充底部填充剂94。因此,在构成底部填充剂的材料中采用具有流动性的树脂,在填充于焊锡凸块间之后,通过固化而成型。然而,在coc的周围具有焊线盘97b等部件,在全然不污染这些表面的状态下填充底部填充剂并不容易。另外,随着电路的高集成化,焊锡凸块逐渐窄间距化。变得难以在其间可靠地填充底部填充剂。

3、并且,这种底部填充剂仅用于减轻物理损失等以提高连接的可靠性。

4、在此,从抑制所搭载的半导体等元件的异常动作、抑制性能的降低及延长寿命等观点考虑,在电子设备中将由电子电路等产生的热量进行散热是非常重要的。即,在以往使用的底部填充剂中,关于基于底部填充剂的散热性能的提高,具有进一步研究的空间。

5、因此,本发明的目的为提供一种具备导热性优异的含填料层的接合体的制造方法、具备通过上述制造方法而获得的接合体的半导体器件的制造方法及在上述制造方法中所使用的树脂组合物。

6、用于解决技术课题的手段

7、以下,示出本发明的具体方式的例子。

8、<1>一种接合体的制造方法,其包括:

9、准备具备具有凸部的面的基板a,及具备配线端子的基板b的工序;

10、在上述基板a的具有上述凸部的面上,形成包含粘合剂及填料的含填料层的工序;

11、将上述含填料层与上述凸部一起进行平坦化来使上述凸部的至少一部分从上述含填料层露出而获得层叠体的工序;以及

12、将上述层叠体的具有含填料层的面与上述基板b所具备的上述配线端子的至少一部分接合的工序。

13、<2>根据<1>所述的接合体的制造方法,其中,

14、形成上述含填料层的工序包括如下工序:将包含选自粘合剂及粘合剂的前体中的至少一种树脂和填料的树脂组合物适用于所述基板a的具有上述凸部的面上。

15、<3>根据<2>所述的接合体的制造方法,其中,形成上述含填料层的工序包括在上述适用后以150~300℃的温度加热组合物。

16、<4>根据<2>或<3>所述的接合体的制造方法,其中,上述树脂组合物包含选自环化树脂及其前体中的至少一种树脂作为上述树脂。

17、<5>根据<1>至<4>中任一项所述的接合体的制造方法,其中,上述层叠体中的含填料层的ttv为10μm以下,上述ttv是指,将从含填料层的边缘部向1mm以上的内侧的区域分割为2mm见方的分区,测定每个分区中的一个表面与另一个表面之间的最大厚度(t1)和一个表面与另一个表面之间的最小厚度(t2),按每个分区计算膜厚差(t1-t2),在各分区按膜厚差(t1-t2)从大到小的顺序设置排序,将从最上位分区按膜厚差从大到小的顺序的相当于总分区数的10%的个数的分区组及从最下位分区按膜厚差从小到大的顺序的相当于总分区数的10%的个数的分区组除外,剩余的分区组的各膜厚差(t1-t2)的算术平均值。

18、<6>根据<1>至<5>中任一项所述的接合体的制造方法,其中,上述凸部包含金属。

19、<7>根据<6>所述的接合体的制造方法,其中,上述金属包含选自铜、锡及镍中的至少一种金属。

20、<8>根据<1>至<7>中任一项所述的接合体的制造方法,其中,上述凸部为通过至少含有包含铜的层及包含锡的层而成的凸部。

21、<9>根据<1>至<8>中任一项所述的接合体的制造方法,其中,上述含填料层中所包含的上述粘合剂为绝缘性粘合剂。

22、<10>根据<1>至<9>中任一项所述的接合体的制造方法,其中,上述含填料层中所包含的上述粘合剂包含选自乙烯基、丙烯酰基及甲基丙烯酰基中的至少一种基团。

23、<11>根据<1>至<10>中任一项所述的接合体的制造方法,其中,上述填料包含选自氮化硼、氮化铝、氮化硅、氧化铝、氧化镁、氧化锌及氧化铍中的至少一种。

24、<12>根据<1>至<11>中任一项所述的接合体的制造方法,其中,上述填料的体积电阻率为1.0×1011q·cm以上。

25、<13>根据<1>至<12>中任一项所述的接合体的制造方法,其中,上述填料的平均粒径为10μm以下,上述平均粒径为相对各粒子的表观轮廓的最小包含圆的直径的平均值。

26、<14>根据<1>至<13>中任一项所述的接合体的制造方法,其中,获得上述层叠体的工序中的上述平坦化通过切割来进行。

27、<15>根据<1>至<14>中任一项所述的接合体的制造方法,其中,上述接合工序中的接合温度为300℃以下。

28、<16>根据<1>至<15>中任一项所述的接合体的制造方法,其中,所获得的接合体中的含填料层的热扩散率为2.0×10-7m2s-1以上。

29、<17>一种半导体器件的制造方法,所述半导体器件具备通过<1>至<16>中任一项所述的接合体的制造方法而获得的接合体。

30、<18>一种树脂组合物,其用于<1>至<16>中任一项所述的接合体的制造方法中的上述含填料层的形成。

31、发明效果

32、根据本发明,提供一种具备导热性优异的含填料层的接合体的制造方法、具备通过上述制造方法而获得的接合体的半导体器件的制造方法及在上述制造方法中所使用的树脂组合物。

- 还没有人留言评论。精彩留言会获得点赞!