半导体装置的制作方法

本发明的一个方式涉及一种金属氧化物的制造方法。本发明的一个方式涉及一种晶体管、半导体装置及电子设备。另外,本发明的一个方式涉及一种半导体装置的制造方法。另外,本发明的一个方式涉及一种半导体晶片及模块。注意,在本说明书等中,半导体装置是指能够通过利用半导体特性而工作的所有装置。除了晶体管等半导体元件之外,半导体电路、运算装置或存储装置也是半导体装置的一个方式。显示装置(液晶显示装置、发光显示装置等)、投影装置、照明装置、电光装置、蓄电装置、存储装置、半导体电路、摄像装置、电子设备等有时包括半导体装置。注意,本发明的一个方式不局限于上述。本说明书等所公开的发明的一个方式涉及一种物体、方法或制造方法。另外,本发明的一个方式涉及一种工序(process)、机器(machine)、产品(manufacture)或者组合物(composition ofmatter)。

背景技术:

1、近年来,已对半导体装置进行开发,lsi、cpu及存储器主要用于半导体装置。cpu是包括将半导体晶片加工为芯片的半导体集成电路(至少包括晶体管及存储器)且形成有作为连接端子的电极的半导体元件的集合体。

2、lsi、cpu及存储器等的半导体电路(ic芯片)安装在例如印刷线路板等电路板上,并被用作各种电子设备的部件之一。

3、此外,通过使用形成在具有绝缘表面的衬底上的半导体薄膜构成晶体管的技术受到注目。该晶体管被广泛地应用于集成电路(ic)、图像显示装置(也简单地记载为显示装置)等电子设备。作为可以应用于晶体管的半导体薄膜,硅类半导体材料被广泛地周知。作为其他材料,氧化物半导体受到关注。

4、另外,已知使用氧化物半导体的晶体管的泄漏电流在非导通状态下极低。例如,专利文献1已公开了应用使用氧化物半导体的晶体管的泄漏电流低的特性的低功耗cpu等。另外,例如专利文献2已公开了利用使用氧化物半导体的晶体管的泄漏电流低的特性实现存储内容的长期保持的存储装置等。

5、近年来,随着电子设备的小型化和轻量化,对集成电路的进一步高密度化的要求提高。此外,有提高包含集成电路的半导体装置的生产率的需求。

6、[先行技术文献]

7、[专利文献]

8、[专利文献1]日本专利申请公开第2012-257187号公报

9、[专利文献2]日本专利申请公开第2011-151383号公报

技术实现思路

1、发明所要解决的技术问题

2、本发明的一个方式的目的之一是提供一种能够进行多点测量的半导体装置。此外,本发明的一个方式的目的之一是提供一种晶体管的电特性不均匀小的半导体装置。此外,本发明的一个方式的目的之一是提供一种可靠性良好的半导体装置。另外,本发明的一个方式的目的之一是提供一种具有良好的电特性的半导体装置。此外,本发明的一个方式的目的之一是提供一种通态电流高的半导体装置。此外,本发明的一个方式的目的之一是提供一种能够实现微型化或高集成化的半导体装置。此外,本发明的一个方式的目的之一是提供一种低功耗的半导体装置。

3、注意,这些目的的记载不妨碍其他目的的存在。注意,本发明的一个方式并不需要实现所有上述目的。除上述目的外的目的从说明书、附图、权利要求书等的描述中是显而易见的,并且可以从所述描述中抽出。

4、解决技术问题的手段

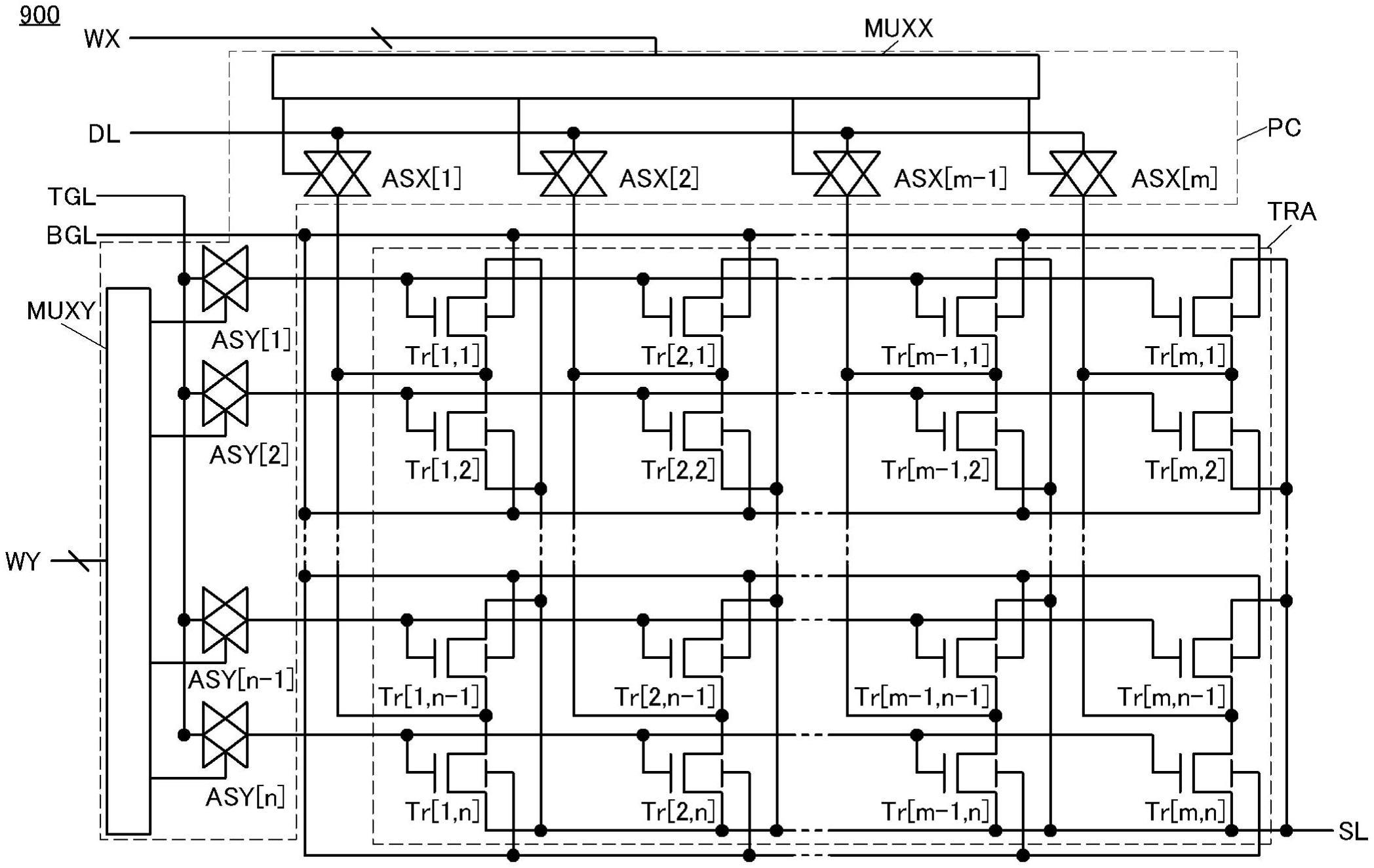

5、本发明的一个方式是一种包括第一层、第一层上的第二层、第一布线、第二布线以及第三布线的半导体装置。第一层包括第一复用器、第二复用器以及第一至第四模拟开关,第二层包括第一至第四晶体管。第一至第四晶体管各自包括源极、漏极以及第一栅极。第一布线与第一至第四晶体管各自的源极和漏极中的一个电连接。第一模拟开关及第二模拟开关各自的第一端子与第一复用器电连接,第一模拟开关及第二模拟开关各自的第二端子与第二布线电连接。第一模拟开关的第三端子与第一晶体管及第二晶体管各自的源极和漏极中的另一个电连接,第二模拟开关的第三端子与第三晶体管及第四晶体管各自的源极和漏极中的另一个电连接。第三模拟开关及第四模拟开关各自的第一端子与第二复用器电连接,第三模拟开关及第四模拟开关各自的第二端子与第三布线电连接。第三模拟开关的第三端子与第一晶体管及第三晶体管各自的第一栅极电连接,第四模拟开关的第三端子与第二晶体管及第四晶体管各自的第一栅极电连接。

6、优选的是,上述半导体装置还包括第四布线,第一至第四晶体管各自还包括第二栅极,第四布线与第一至第四晶体管各自的第二栅极电连接。

7、另外,在上述半导体装置中,优选的是,第一至第四晶体管各自在沟道形成区域中包含金属氧化物。

8、另外,在上述半导体装置中,优选的是,金属氧化物包含铟、镓及锌。

9、另外,在上述半导体装置中,优选的是,第一至第四模拟开关各自使用cmos电路构成。

10、另外,在上述半导体装置中,优选的是,cmos电路所包括的晶体管在沟道形成区域中包含硅。

11、本发明的另一个方式是一种包括第一层、第一层上的第二层、第一布线、第二布线以及第三布线的半导体装置。第一层包括第一复用器、第二复用器、第一至第三模拟开关,第二层包括第一晶体管以及第三晶体管。第一晶体管及第三晶体管各自包括源极、漏极以及第一栅极。第一布线与第一晶体管及第三晶体管各自的源极和漏极中的一个电连接。第一模拟开关及第二模拟开关各自的第一端子与第一复用器电连接,第一模拟开关及第二模拟开关各自的第二端子与第二布线电连接。第一模拟开关的第三端子与第一晶体管的源极和漏极中的另一个电连接,第二模拟开关的第三端子与第三晶体管的源极和漏极中的另一个电连接。第三模拟开关的第一端子与第二复用器电连接,第三模拟开关的第二端子与第三布线电连接,第三模拟开关的第三端子与第一晶体管及第三晶体管各自的第一栅极电连接。

12、优选的是,上述半导体装置还包括第四布线,第一晶体管及第三晶体管各自还包括第二栅极,第四布线与第一晶体管及第三晶体管各自的第二栅极电连接。

13、另外,在上述半导体装置中,优选的是,第一晶体管及第三晶体管各自在沟道形成区域中包含金属氧化物。

14、另外,在上述半导体装置中,优选的是,金属氧化物包含铟、镓及锌。

15、另外,在上述半导体装置中,优选的是,第一至第三模拟开关各自使用cmos电路构成。

16、另外,在上述半导体装置中,优选的是,cmos电路所包括的晶体管在沟道形成区域中包含硅。

17、本发明的另一个方式是一种包括第一层、第一层上的第二层、第一布线、第二布线以及第三布线的半导体装置。第一层包括第一复用器、第二复用器、第一模拟开关、第三模拟开关以及第四模拟开关,第二层包括第一晶体管、第二晶体管。第一晶体管及第二晶体管各自包括源极、漏极以及第一栅极。第一布线与第一晶体管及第二晶体管各自的源极和漏极中的一个电连接。第一模拟开关的第一端子与第一复用器电连接,第一模拟开关的第二端子与第二布线电连接,第一模拟开关的第三端子与第一晶体管及第二晶体管各自的源极和漏极中的另一个电连接。第三模拟开关及第四模拟开关各自的第一端子与第二复用器电连接,第三模拟开关及第四模拟开关各自的第二端子与第三布线电连接。第三模拟开关的第三端子与第一晶体管的第一栅极电连接,第四模拟开关的第三端子与第二晶体管的第一栅极电连接。

18、优选的是,上述半导体装置还包括第四布线,第一及第二晶体管各自还包括第二栅极,第四布线与第一及第二晶体管各自的第二栅极电连接。

19、另外,在上述半导体装置中,优选的是,第一及第二晶体管各自在沟道形成区域中包含金属氧化物。

20、另外,在上述半导体装置中,优选的是,金属氧化物包含铟、镓及锌。

21、另外,在上述半导体装置中,优选的是,第一模拟开关、第三模拟开关及第四模拟开关各自使用cmos电路构成。

22、另外,在上述半导体装置中,优选的是,cmos电路所包括的晶体管在沟道形成区域中包含硅。

23、发明效果

24、根据本发明的一个方式可以提供一种能够进行多点测量的半导体装置。根据本发明的一个方式可以提供一种晶体管的电特性不均匀小的半导体装置。此外,根据本发明的一个方式可以提供一种可靠性良好的半导体装置。此外,根据本发明的一个方式可以提供一种具有良好的电特性的半导体装置。此外,根据本发明的一个方式可以提供一种通态电流高的半导体装置。此外,根据本发明的一个方式可以提供一种能够实现微型化或高集成化的半导体装置。此外,根据本发明的一个方式可以提供一种低功耗的半导体装置。

25、注意,这些效果的记载不妨碍其他效果的存在。注意,本发明的一个方式并不需要实现所有上述效果。除上述效果外的效果从说明书、附图、权利要求书等的描述中是显而易见的,并且可以从所述描述中抽出。

- 还没有人留言评论。精彩留言会获得点赞!