成像装置和电子设备的制作方法

本公开涉及一种成像装置和电子设备。

背景技术:

1、传统上,在互补金属氧化物半导体(cmos)型固态成像元件(cmos图像传感器)中,为了增加可以在执行像素部的光电转换的光电二极管中累积的电荷量,可以形成能够在深的区域中累积电荷的电位。在这种情况下,通过使用插入在硅中的纵型栅电极代替通常的传输栅极,调制可以被执行到深的区域,并且施加电场以执行读出。此外,还提出了采用多个纵型栅电极的结构,从而增加调制力。

2、引用文献列表

3、专利文献

4、专利文献1:2018-190797a

技术实现思路

1、技术问题

2、这里,在传统的元件结构中,为了抑制在提取累积在光电二极管中的电荷时传输效率的降低,需要使传输栅电极在沟道长度方向上的宽度大于纵型栅电极的直径。然而,当传输栅电极的宽度增加时,由于通过传输栅电极和浮动扩散区域的接近而形成的强电场,可能发生电子雪崩,因此,存在由于像素信号的振幅饱和而导致的诸如白点等图像质量劣化的问题。

3、因此,本公开提出了一种成像装置和电子设备,其能够在抑制图像质量的劣化的同时抑制传输效率的降低。

4、问题的解决方案

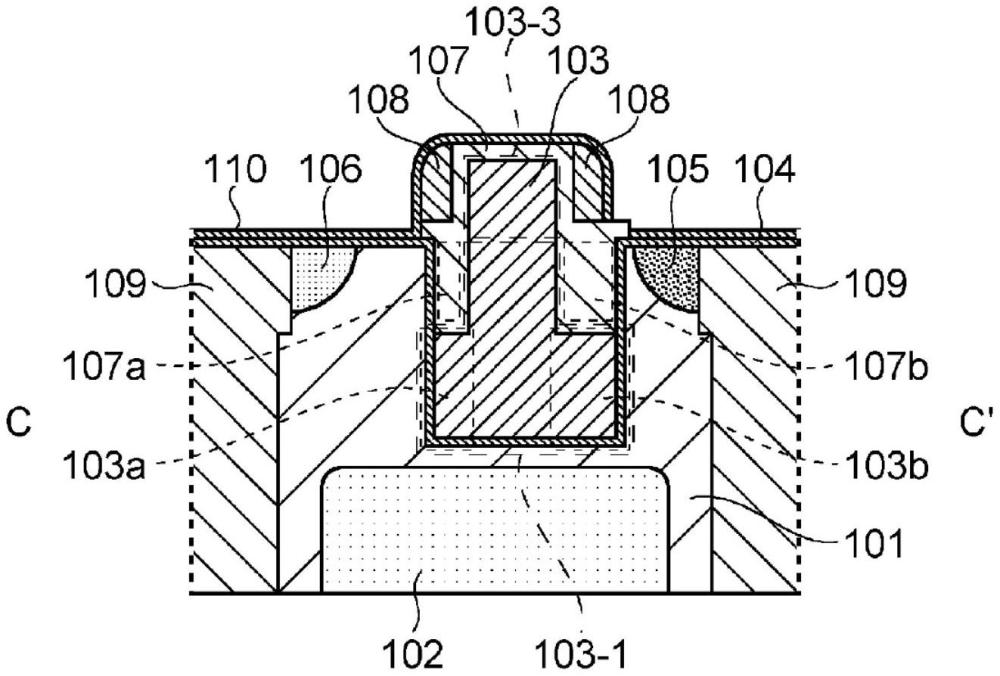

5、为了解决上述问题,根据本公开实施方案的成像装置包括以二维格子状排列的多个像素,其中每个所述像素包括光电转换单元,其设置在半导体基板的第一面侧以执行入射光的光电转换;纵型栅电极,其设置在所述半导体基板上以从与第一面相对的第二面侧靠近所述光电转换单元;栅极绝缘膜,其设置在所述纵型栅电极和所述半导体基板之间;传输栅电极,其在所述半导体基板的第二面上与所述纵型栅电极连接;和第一扩散区域,其设置在所述半导体基板的第二面侧,和所述纵型栅电极具有其中所述光电转换单元侧的底部的直径比所述传输栅电极侧的上部的直径扩大的结构。

技术特征:

1.一种成像装置,包括

2.根据权利要求1所述的成像装置,其中

3.根据权利要求1所述的成像装置,还包括

4.根据权利要求3所述的成像装置,其中

5.根据权利要求4所述的成像装置,其中

6.根据权利要求5所述的成像装置,其中

7.根据权利要求4所述的成像装置,其中

8.根据权利要求4所述的成像装置,其中

9.根据权利要求4所述的成像装置,其中

10.根据权利要求4所述的成像装置,其中

11.根据权利要求3所述的成像装置,其中

12.根据权利要求1所述的成像装置,其中

13.根据权利要求1所述的成像装置,还包括

14.根据权利要求2所述的成像装置,其中

15.根据权利要求1所述的成像装置,其中

16.一种电子设备,其包括根据权利要求1所述的成像装置。

技术总结

本发明在抑制传输效率的降低的同时抑制了图像质量的劣化。根据实施方案的成像装置包括以二维格子状排列的多个像素,其中每个所述像素包括光电转换单元,其设置在半导体基板的第一面侧以执行入射光的光电转换;纵型栅电极,其设置在所述半导体基板上以从与第一面相对的第二面侧靠近所述光电转换单元;栅极绝缘膜,其设置在所述纵型栅电极和所述半导体基板之间;传输栅电极,其在所述半导体基板的第二面上与所述纵型栅电极连接;和第一扩散区域,其设置在所述半导体基板的第二面侧,和所述纵型栅电极具有其中所述光电转换单元侧的底部的直径比所述传输栅电极侧的上部的直径扩大的结构。

技术研发人员:西田庆次,中村祐介,杉本匡隆

受保护的技术使用者:索尼半导体解决方案公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!