半导体器件以及用于制造半导体器件的方法与流程

本技术涉及半导体器件。具体而言,本发明涉及具有层叠结构的半导体器件以及用于制造半导体器件的方法。

背景技术:

1、近年来,为了提高器件的功能性,用于堆叠在单独的半导体衬底上制造的具有不同功能的器件的技术的发展已经取得了进展。在这个堆叠期间,有必要在将半导体衬底键合在一起之后将上部器件和下部器件电连接。例如,提出了一种半导体器件,其中堆叠各自包括半导体衬底的晶片和裸片,并且晶片上的器件和裸片上的器件通过贯通过孔电连接(例如,参见ptl 1)。当制造这种半导体器件时,在堆叠裸片之后,形成包括蚀刻停止层的隔离膜,然后形成贯通过孔。

2、[引文列表]

3、[专利文献]

4、[ptl 1]

5、美国专利说明书no.9806055

技术实现思路

1、[技术问题]

2、上述现有技术促进使用后过孔(via-last)工艺来堆叠大量裸片。但是,在上面提到的半导体器件中,当在蚀刻至蚀刻停止层之后执行附加蚀刻时,附加的被蚀刻部分会凸起并变成弓形,并且在形成贯通过孔时,在弓形部分中会出现金属嵌入缺陷。

3、本技术是鉴于这种情况而提出的,并且本技术的目的是防止其中形成有贯通过孔的半导体器件中的金属嵌入缺陷。

4、[问题的解决方案]

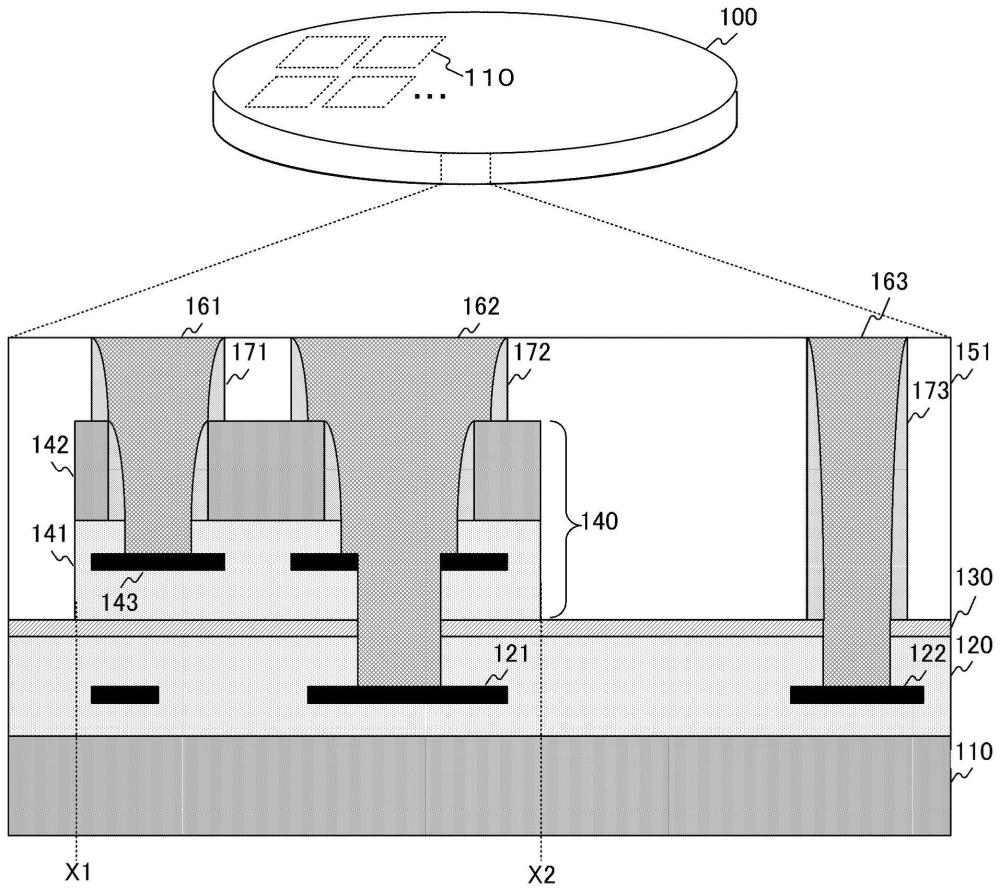

5、本技术是为了解决上面提到的问题而开发的,并且其第一方面提供了一种半导体器件及其制造方法,该半导体器件包括其上形成有重新布线层的衬底;形成在重新布线层的键合表面上的蚀刻停止层;隔着蚀刻停止层键合到键合表面的部分区域的裸片;以及覆盖裸片和蚀刻停止层的隔离膜。这提供了防止金属嵌入缺陷的效果。

6、另外,在这个第一方面中,半导体器件还可以包括衬底侧过孔,其穿透隔离膜和蚀刻停止层并且其一端连接到重新布线层中的布线;以及裸片侧过孔,其穿透隔离膜、裸片和蚀刻停止层并且其一端连接到重新布线层中的布线。这提供了衬底电连接到裸片并且衬底电连接到外部的效果。

7、另外,在这个第一方面中,裸片侧过孔可以形成在不与裸片的端部对应的位置处。这提供了裸片和衬底在不与端部对应的位置处电连接的效果。

8、另外,在这个第一方面中,裸片侧过孔可以形成在裸片的端部处。这提供了减小贯通过孔的裸片侧面积和裸片侧电极焊盘的面积的效果。

9、另外,在这个第一方面中,当用预定的蚀刻气体对蚀刻停止层进行蚀刻时的蚀刻速率可以低于当用该蚀刻气体对隔离膜进行蚀刻时的蚀刻速率。这提供了当蚀刻隔离膜时蚀刻被蚀刻停止层停止的效果。

10、另外,在这个第一方面中,隔离膜可以是氧化硅膜,并且蚀刻停止层可以是氮化硅、碳化硅或碳氮化硅的层。这提供了当蚀刻隔离膜时蚀刻被蚀刻停止层停止的效果。

11、本技术的第二方面还提供了一种半导体器件及其制造方法,该半导体器件包括其上形成有重新布线层的衬底;键合到重新布线层的键合表面的部分区域的裸片;覆盖裸片和重新布线层的第一隔离膜;第二隔离膜;以及形成在第一隔离膜与第二隔离膜之间并且在裸片的端部附近具有台阶的蚀刻停止层。这提供了防止金属嵌入缺陷的效果。

12、另外,在第二方面中,半导体器件还可以包括衬底侧过孔,其穿透第一隔离膜和第二隔离膜以及蚀刻停止层,并且其一端连接到重新布线层中的布线;以及裸片侧过孔,其穿透第一隔离膜和第二隔离膜、蚀刻停止层以及裸片,并且其一端连接到重新布线层中的布线。这提供了衬底电连接到裸片并且衬底电连接到外部的效果。

13、而且,在这个第二方面中,裸片侧过孔可以形成在不与裸片的端部对应的位置处。这提供了裸片和衬底在不与端部对应的位置处电连接的效果。

14、而且,在这个第二方面中,裸片侧过孔可以形成在裸片的端部处。这提供了减小贯通过孔的裸片侧面积和裸片侧电极焊盘的面积的效果。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,还包括:

3.根据权利要求2所述的半导体器件,其中

4.根据权利要求2所述的半导体器件,其中

5.根据权利要求1所述的半导体器件,其中

6.根据权利要求5所述的半导体器件,其中

7.一种半导体器件,包括:

8.根据权利要求7所述的半导体器件,还包括:

9.根据权利要求8所述的半导体器件,其中

10.根据权利要求8所述的半导体器件,其中

11.一种用于制造半导体器件的方法,包括:

12.一种用于制造半导体器件的方法,包括:

技术总结

为了防止在其中形成有贯通过孔的半导体器件中出现金属埋入缺陷。该半导体器件包括衬底、蚀刻停止层、裸片和隔离膜。在该半导体器件中,在衬底上形成有重新布线层。蚀刻停止层形成在重新布线层的键合表面上。裸片隔着蚀刻停止层键合到键合表面的部分区域。隔离膜覆盖裸片和蚀刻停止层。

技术研发人员:藤井宣年

受保护的技术使用者:索尼半导体解决方案公司

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!