一种基于厚薄膜电路基板的大功率合成器实现方法与流程

1.本发明涉及微波射频技术领域,尤其涉及一种基于厚薄膜电路基板的大功率合成器实现方法。

背景技术:

2.大功率合成器是提高固态电路输出功率的主要方法,通过若干单元相干工作,叠加单个固态电路的输出功率,就可以获得最终的高输出功率。而大功率3db电桥常用来作为功率合成电路的主要组件。其中宽边耦合的电桥插损小、耐功率高、带宽宽等优点,常用来设计大功率3db电桥。宽边耦合电桥的介质板厚度和相对介电常数确定了其耦合线的特征阻抗。3db电桥的耦合部分电长度是工作频率的四分之一波长,因此采用厚膜陶瓷基板因为有较高的相对介电常数,其物理尺寸较小,容易实现小型化。但是,陶瓷基板相对介电常数越高,耦合线的线宽就越窄,其等阻抗越高,根据功率p和感应电压u以及阻抗z之间的关系,在相同输入功率条件下,线上感应电压就越大,即导致耦合器的导体损耗更大,发热量更多,不利于实现低插损,不利于承受大功率。同时,导线间距太小,在大功率、高插损条件下还会局部打火,引起介质击穿。

技术实现要素:

3.本发明提供了一种基于厚薄膜电路基板的大功率合成器实现方法,以解决上述现有技术的不足,采用厚膜工艺,将二维电路变成三维电路,将负载通过厚膜工艺直接设置在内部的厚膜导体层,表层电路层设置限幅器、低噪放和射频传输线。各层之间的连接通过金属化过孔来实现,通过高度集成的方式,使得整个系统尺寸大大减小。

4.为了实现本发明的目的,拟采用以下技术:一种基于厚薄膜电路基板的大功率合成器实现方法,包括:提供一层薄膜电路层,薄膜电路层上具有第一3db电桥、第二3db电桥、第一射频传输线、第二射频传输线、第一低噪放、第二低噪放、第一限幅器及第二限幅器,第一3db电桥与第一限幅器及第二限幅器连接,第一限幅器连接于第一低噪放,第二限幅器连接于第二低噪放,第一低噪放及第二低噪放连接于第二3db电桥,第一3db电桥连接于电路的输入端,第二3db电桥连接于电路的输出端;提供一层牺牲层,牺牲层设于薄膜电路层的下侧;提供多层陶瓷基板,相邻两层陶瓷基板之间、位于顶层的陶瓷基板上侧、及位于底层的陶瓷基板下侧均设有厚膜电路层,位于顶层的厚膜电路层设于牺牲层的下侧,位于底层的厚膜电路层的下侧设有钼铜层。

5.进一步地,第一3db电桥、第二3db电桥、第一射频传输线及第二射频传输线的下层分别设有薄膜介质层,薄膜介质层设于薄膜电路层上。

6.进一步地,牺牲层包括位于上层的薄膜基板,薄膜基板的下侧至少设有一层厚膜牺牲层。

7.进一步地,厚膜电路层至少包括由上至下设置的第一厚膜电路层、第二厚膜电路层、第三厚膜电路层、第四厚膜电路层及第五厚膜电路层;第一厚膜电路层设于牺牲层的下侧;第五厚膜电路层设于钼铜层的上侧;第二厚膜电路层上设有第一负载与第二负载。

8.进一步地,陶瓷基板至少包括第一陶瓷基板、第二陶瓷基板、第三陶瓷基板及第四陶瓷基板;第一陶瓷基板设于第一厚膜电路层的下侧;第二陶瓷基板设于第二厚膜电路层的下侧;第三陶瓷基板设于第三厚膜电路层的下侧;第四陶瓷基板设于第四厚膜电路层的下侧;第五厚膜电路层设于第四陶瓷基板的下侧。

9.进一步地,薄膜电路层上开设有多个散热孔,散热孔依次贯穿牺牲层、多层陶瓷基板、多层厚膜电路层及钼铜层。

10.进一步地,第一低噪放及第二低噪放分别通过第一信道连接至第四厚膜电路层上;第一射频传输线与第二射频传输线分别通过第二信道连接至第一负载与第二负载上;第一负载与第二负载上分别通过第三信道连接至第三厚膜电路层上;第一3db电桥与第二3db电桥分别通过第四信道连接至第一厚膜电路层上。

11.进一步地,薄膜电路层上设有一对第一过孔;牺牲层上设有一对第一金属过孔;第一厚膜电路层、第二厚膜电路层及第三厚膜电路层上分别设有一对第二过孔;第一陶瓷基板、第二陶瓷基板及第三陶瓷基板上分别设有一对第二金属过孔;第一信道由第一过孔、第一金属过孔、第二过孔及第二金属过孔连通形成。

12.进一步地,薄膜电路层上设有一对第三过孔;牺牲层上设有一对第三金属过孔;第一厚膜电路层上设有一对第四过孔;第一陶瓷基板上设有一对第四金属过孔;第二信道由第三过孔、第三金属过孔、第四过孔及第四金属过孔连通形成;第二厚膜电路层上设有一对第五过孔;第二陶瓷基板上设有一对第五金属过孔;第三信道由第五过孔及第五金属过孔连通形成。

13.进一步地,薄膜电路层上设有一对第六过孔;牺牲层上设有一对第六金属过孔;第四信道由第六过孔与第六金属过孔连通形成。

14.上述技术方案的优点在于:一、由于采用基于厚膜的多层结构,布线层数较多,设计走线可以更加灵活,多层走线避免连接线出现跨连、交叉等问题。

15.二、每个不同的模块均设置有独立的接地层,而其中需要实现良好屏蔽的器件周围是通过金属过孔及过孔与对应的接地层连接,从而形成了类似于腔体的隔离状态,从而提高对杂散信号的屏蔽效果,进而提高整个电路的电磁兼容性能。

16.三、用于形成薄膜电路层及厚膜电路层的基板均采用氮化硅陶瓷材料制成,而该材料具有相对介电常数高、导热性能良好等特点,从而可以使系统满足小型化和大功率散热的需要。

17.四、牺牲层的表层由氮化硅陶瓷薄膜基板和薄膜金属层构成,并且在氮化硅薄膜基板下还设置了两层氮化硅厚膜基板作为牺牲层,在操作加工时,需要将两层氮化硅厚膜基板减薄、打磨及抛光等,进而使氮化硅厚膜基板保持表面平整,从而消除了氮化硅厚膜基板在烧制过程中由于受热不均而引发的收缩、膨胀等弯曲问题。并且氮化硅厚膜基板平整后还能使氮化硅陶瓷薄膜基板可以和其之间具有良好的叠合效果。

18.五、薄膜电路层采用的是光刻技术,从而可以实现薄膜电路层的精细化加工,同时采用的这种技术其加工精度可以小于等于0.5微米,因此能够满足高密度集成后的小型化加工精度要求。同时,通过薄膜工艺的精度控制,能使得薄膜电路层的表面光滑,进而解决了厚膜由于加工精度不高、表面金属不平整,从而给射频信号传输带来较大损耗的问题,并解决了大功率信号下引发的发热、射频线间打火、介质击穿等问题。

19.六、厚薄膜混合一体化电路,将大功率的3db电桥直接光刻在薄膜电路层上,因此不需要另外制作3db电桥再安装到电路上,从而避免出现安装空隙,进而切断散热路径,不利于散热的现象。而一体化的电路设计不存在安装空隙,并且氮化硅陶瓷基板的高导热特性也使该电路具有良好的散热效果。

20.七、为了提高薄膜电路层的性能,因此薄膜电路层采用的是加厚的金属导体层,由于加厚的金属导体层横截面积增加,因此其电阻将减小,相应地,其可承受的电流强度将提升,此外,加厚的金属导体层还会提供水平方向的散热。

21.八、为了提高第一3db电桥、第二3db电桥、第一射频传输线及第二射频传输线区域处的电场击穿阈值,并增加功率容量,因此在此区域采用薄膜工艺印刷了薄膜介质层。

22.九、其中钼铜层的设置能够提高整个电路的散热效果,其中的钼铜层是连接在金属壳体上的,与此同时,钼铜层还通过金属过孔及过孔连通至薄膜电路层上,从而提高了散热效果。由于其中的各个厚膜电路层是由钨合金制成的,因此各个厚膜电路层和壳体的热膨胀系数不一样的,进而不能直接将厚膜电路层连接在壳体上,而采用钼铜层不仅能够将壳体和厚膜电路层连接在一起,还能够有效地提高了散热效果。

附图说明

23.为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明做进一步的详细描述。

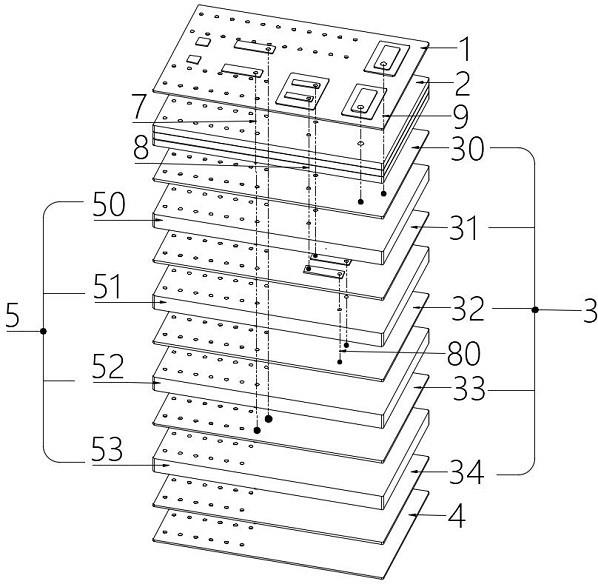

24.图1示出了其中一种实施例的立体结构图。

25.图2示出了薄膜电路层的立体结构图。

26.图3示出了第二厚膜电路层的立体结构图。

27.图4示出了薄膜电路层各电子器件连接关系图。

28.图5示出了3db电桥的结构图。

29.附图标记说明:1-薄膜电路层、10-薄膜介质层、11-第一3db电桥、12-第二3db电桥、13-第一射频传输线、14-第二射频传输线、15-第一低噪放、16-第二低噪放、17-第一限幅器、18-第二限幅器、2-牺牲层、3-厚膜电路层、30-第一厚膜电路层、31-第二厚膜电路层、32-第三厚膜电路层、33-第四厚膜电路层、34-第五厚膜电路层、310-第一负载、311-第二负载、4-钼铜层、5-陶瓷基板、50-第一陶瓷基板、51-第二陶瓷基板、52-第三陶瓷基板、53-第四陶瓷基板、6-散热孔、7-第一信道、8-第二信道、80-第三信道、9-第四信道。

具体实施方式

30.如图5所示,为其中一种3db电桥的结构图。而该3db电桥的耦合部分电长度是工作频率的四分之一波长,因此若采用介电常数相对较高、物理尺寸较小的厚膜陶瓷基板,则容易实现电路的小型化设计。但是,陶瓷基板相对介电常数越高,耦合线的线宽就越窄,其等阻抗就越高,根据功率p和感应电压u以及阻抗z之间的关系,在相同输入功率条件下,线上感应电压就越大,即导致耦合器的导体损耗更大,发热量更多,不利于实现低插损,不利于承受大功率。同时,产品小型化后,导线间距太小,对加工精度要求较高,而厚膜工艺不能实现高精度的加工要求,因此就需要结合薄膜工艺,需要在表层采用氮化硅薄膜基板就可以实现加工精度的要求,同时采用薄膜工艺加工3db电桥,形成一体化电路,同时还可以实现高精度要求。同时一体化设计的电路能够提供均匀的热传导,从而有利于散热。同时将所有微带线弯折部分圆角化,那么也就不会形成尖端放电,使得电场分布更加均匀。另外,在局部电场强度过大的区域,在其导体表面镀一层薄膜介质层,可以提高其功率容量,从而防止局部空气或介质被击穿。

31.如图1~图3所示,一种基于厚薄膜电路基板的大功率合成器实现方法,包括:提供一层薄膜电路层1,薄膜电路层1采用薄膜工艺镀金属层的方法制备而成,并且薄膜电路层1为加厚的金属层。加厚金属层的使用增加了薄膜电路层1的横截面积,那么其电阻将会减小,相应地,其承受的电流强度也就有所提升,另外,加厚的薄膜电路层1会提供水平方向的散热,由于采用面散热的方式,因此提高了散热效果。薄膜电路层1上具有第一3db电桥11、第二3db电桥12、第一射频传输线13、第二射频传输线14、第一低噪放15、第二低噪放16、第一限幅器17及第二限幅器18,第一3db电桥11与第一限幅器17及第二限幅器18连接,第一限幅器17连接于第一低噪放15,第二限幅器18连接于第二低噪放16,第一低噪放15及第二低噪放16连接于第二3db电桥12,第一3db电桥11连接于电路的输入端,第二3db电桥12连接于电路的输出端。如图4示出了第一3db电桥11、第二3db电桥12、第一低噪放15、第二低噪放16、第一限幅器17及第二限幅器18之间的连接关系。其中,第一3db电桥11、第二3db电桥12、第一低噪放15、第二低噪放16、第一限幅器17及第二限幅器18均分别通过第一射频传输线13、第二射频传输线14进行导通,并且对应的第一射频传输线13和第二射频传输线14上还连接有第一负载310与第二负载311。并且第一射频传输线13和第二射频传输线14分别连接在电路的输入端和输出端上。其中,为了提高第一3db电桥11、第二3db电桥12、第一射频传输线13及第二射频传输线14的功率容量,从而防止局部空气或介质被击穿,因此在第一3db电桥11、第二3db电桥12、第一射频传输线13及第二射频传输线14的下层分别设有薄膜介质层10,薄膜介质层10设于薄膜电路层1上。

32.提供一层牺牲层2,牺牲层2设于薄膜电路层1的下侧,牺牲层2包括位于上层的薄

膜基板,薄膜基板的下侧至少设有一层厚膜牺牲层。在制备时,进行薄膜基板的减薄、打磨及抛光,然后和与厚膜牺牲层叠合。其中打磨、抛光是为了确保其表面平整,解决了厚膜工艺烧制过程中由于受热不均或者收缩带来的弯曲或表面不平整等问题。厚膜牺牲层也采用氮化硅陶瓷是为了保持整个系统基板的一致性,以使整个系统具有相同的热膨胀系数、导热系数等,从而保证了良好的叠合效果。同时氮化硅陶瓷的高导热特性可以保证快速散热,满足大功率需要。

33.提供多层陶瓷基板5,相邻两层陶瓷基板5之间、位于顶层的陶瓷基板5上侧、及位于底层的陶瓷基板5下侧均设有厚膜电路层3,位于顶层的厚膜电路层3设于牺牲层2的下侧,位于底层的厚膜电路层3的下侧设有钼铜层4。

34.其中,厚膜电路层3至少包括由上至下设置的第一厚膜电路层30、第二厚膜电路层31、第三厚膜电路层32、第四厚膜电路层33及第五厚膜电路层34。第一厚膜电路层30设于牺牲层2的下侧。第五厚膜电路层34设于钼铜层4的上侧。第二厚膜电路层31上设有第一负载310与第二负载311。

35.陶瓷基板5至少包括第一陶瓷基板50、第二陶瓷基板51、第三陶瓷基板52及第四陶瓷基板53。第一陶瓷基板50设于第一厚膜电路层30的下侧。第二陶瓷基板51设于第二厚膜电路层31的下侧。第三陶瓷基板52设于第三厚膜电路层32的下侧。第四陶瓷基板53设于第四厚膜电路层33的下侧。第五厚膜电路层34设于第四陶瓷基板53的下侧。

36.薄膜电路层1上开设有多个散热孔6,散热孔6依次贯穿牺牲层2、多层陶瓷基板5、多层厚膜电路层3及钼铜层4。散热孔6的设置提高了该电路的散热效果,尤其大功率器件第一3db电桥11和第二3db电桥12引入后,该电路的散热效果。

37.详细地,第一低噪放15及第二低噪放16分别通过第一信道7连接至第四厚膜电路层33上。第一射频传输线13与第二射频传输线14分别通过第二信道8连接至第一负载310与第二负载311上。第一负载310与第二负载311上分别通过第三信道80连接至第三厚膜电路层32上。第一3db电桥11与第二3db电桥12分别通过第四信道9连接至第一厚膜电路层30上。

38.具体地,薄膜电路层1上设有一对第一过孔,牺牲层2上设有一对第一金属过孔,第一厚膜电路层30、第二厚膜电路层31及第三厚膜电路层32上分别设有一对第二过孔,第一陶瓷基板50、第二陶瓷基板51及第三陶瓷基板52上分别设有一对第二金属过孔,第一信道7由第一过孔、第一金属过孔、第二过孔及第二金属过孔连通形成。

39.具体地,薄膜电路层1上设有一对第三过孔,牺牲层2上设有一对第三金属过孔,第一厚膜电路层30上设有一对第四过孔,第一陶瓷基板50上设有一对第四金属过孔,第二信道8由第三过孔、第三金属过孔、第四过孔及第四金属过孔连通形成。

40.具体地,第二厚膜电路层31上设有一对第五过孔,第二陶瓷基板51上设有一对第五金属过孔,第三信道80由第五过孔及第五金属过孔连通形成。

41.具体地,薄膜电路层1上设有一对第六过孔,牺牲层2上设有一对第六金属过孔,第四信道9由第六过孔与第六金属过孔连通形成。

42.且从上述描述中可知,第一厚膜电路层30为第一3db电桥11、第二3db电桥12所对应的金属地层。

43.第三厚膜电路层32为第一负载310与第二负载311所对应的金属地层。

44.第四厚膜电路层33为第一低噪放15与第二低噪放16所对应的金属地层。

45.第五厚膜电路层34下面再加一层钼铜层4,钼铜层4作为散热层和薄膜电路层1通过散热孔6连接,而钼铜层4与外部金属壳体底部相连。由于第五厚膜电路层34采用钨合金制成,因此其和壳体热膨胀系数不同,因此不能很好地进行连接,而钼铜层4的使用不仅起到散热作用,还能很好地和壳体相连。

46.以上所述仅为本发明的优选实施例,并不用于限制本发明,显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1