一种半导体大容值电容结构的制造方法与流程

本发明涉及半导体,尤其涉及一种半导体大容值电容结构的制造方法。

背景技术:

1、射频芯片工作时需要多个大容值旁路电容作为电源滤波或射频旁路。实际应用中一般是通过外接单层陶瓷电容实现。对该器件的要求常常是,需要承受高的直流电压,射频等效串联寄生电阻和电感小,散热性能好,体积小。受材料和工艺限制,单层陶瓷电容难以对以上要求进行折中,并给出满意的解决方案。近年来,也有使用多层陶瓷电容的例子,缩小了一定的体积。但总的来说,在固定耐压下体积较大,串联寄生电阻不理想,片外互连带来的寄生电感较大,多元件安装带来的耐压和工艺问题突出。因此,开发新的电容制造工艺来适应大容值旁路的片上集成成为关键。

技术实现思路

1、本发明的目的在于克服现有技术中大容值旁路电容的片上集成问题,提供了一种半导体大容值电容结构的制造方法。

2、本发明的目的是通过以下技术方案来实现的:

3、主要提供一种半导体大容值电容结构的制造方法,所述方法包括:

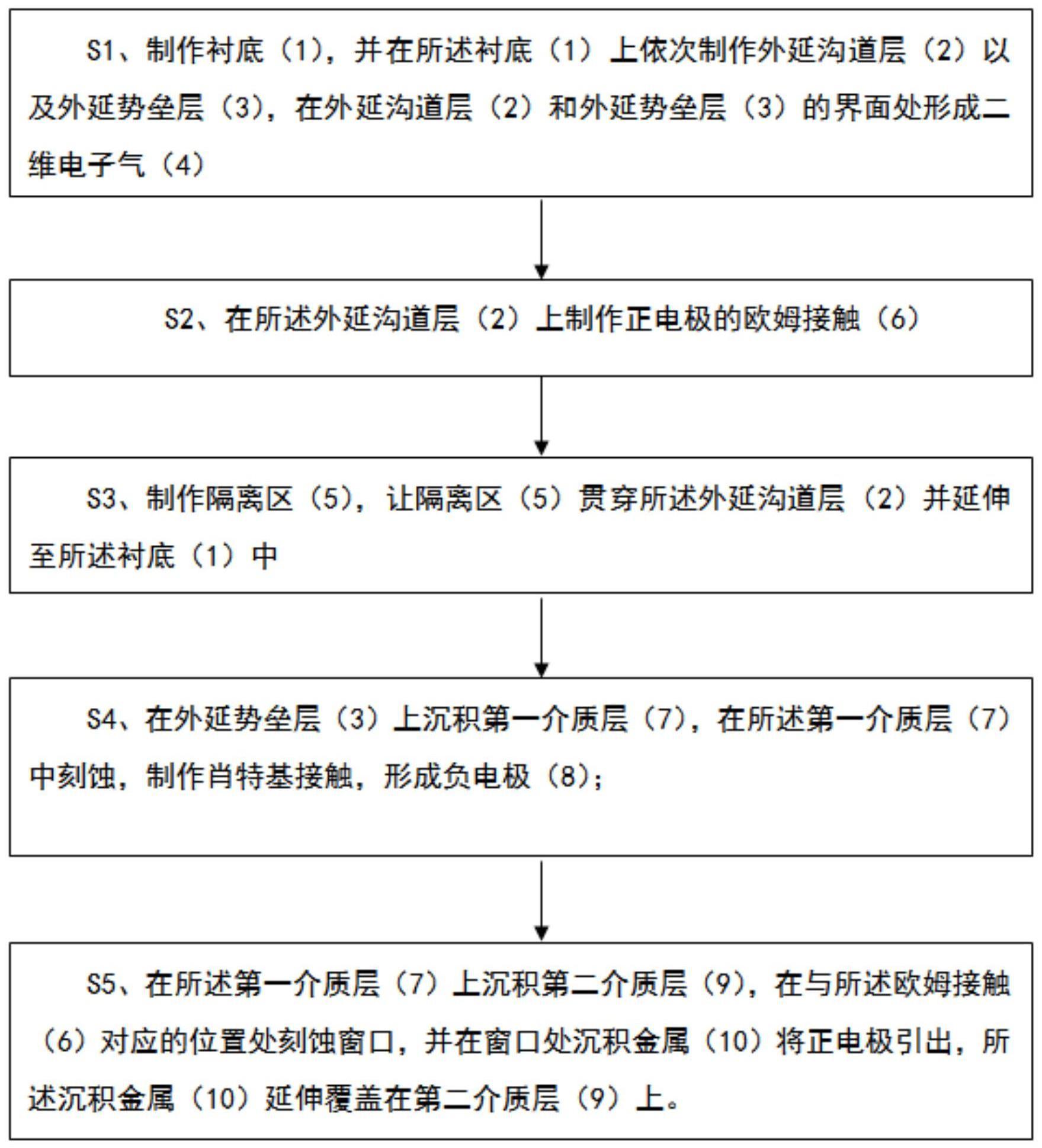

4、s1、制作衬底,并在所述衬底上依次制作外延沟道层以及外延势垒层,在外延沟道层和外延势垒层的界面处形成二维电子气;

5、s2、在所述外延沟道层上制作正电极的欧姆接触;

6、s3、制作隔离区,让隔离区贯穿所述外延沟道层并延伸至所述衬底中;

7、s4、在外延势垒层上沉积第一介质层,在所述第一介质层中刻蚀,制作肖特基接触,形成负电极;

8、s5、在所述第一介质层上沉积第二介质层,在与所述正电极的欧姆接触对应的位置处刻蚀窗口,并在窗口处沉积金属将正电极引出,所述沉积金属延伸覆盖在第二介质层上。

9、其中,将二维电子气作为电容的内部电极实现电极的横向引出,选用反型的薄层外延势垒层作为电容介质层。

10、作为一优选项,一种半导体大容值电容结构的制造方法,所述负电极为长条状结构。

11、作为一优选项,一种半导体大容值电容结构的制造方法,所述衬底为碳化硅衬底。

12、作为一优选项,一种半导体大容值电容结构的制造方法,所述外延沟道层为gan外延沟道层。

13、作为一优选项,一种半导体大容值电容结构的制造方法,所述外延势垒层为alxga1-xn外延势垒层。

14、作为一优选项,一种半导体大容值电容结构的制造方法,所述外延势垒层的厚度为10nm~100nm。

15、作为一优选项,一种半导体大容值电容结构的制造方法,所述第一介质层为sinx介质层。

16、作为一优选项,一种半导体大容值电容结构的制造方法,所述第二介质层为sinx介质层。

17、作为一优选项,一种半导体大容值电容结构的制造方法,所述负电极对应的外延沟道层下方制作有背面金属化孔。

18、作为一优选项,一种半导体大容值电容结构的制造方法,所述隔离区呈方型环状。

19、需要进一步说明的是,上述各选项对应的技术特征在不冲突的情况下可以相互组合或替换构成新的技术方案。

20、与现有技术相比,本发明有益效果是:

21、(1)本发明通过将半导体外延层的二维电子气作为电容的内部电极实现集成电容器的引出,并利用极薄的半导体反型层作介质,实现大比容量片上电容;用二维电子气实现电容电极横向引出,保持了反型层介质的晶格有序和理想性,具有较高的击穿强度,耐压高;同时,不需要片外互连使得寄生电感较小;且由于电容上电极(负电极)和反型层之间是肖特基接触,具有极性。

22、(2)本发明的制作方法与大多数化合物半导体工艺兼容,易于集成,尤其适合gan工艺,不存在增加掩膜、增加工序或调整工艺顺序的情况,成本低。

23、(3)本发明制作的电容结构在50v下实现1500pf/mm2以上的比容值。

24、(4)在一个示例中,本发明的电容结构能够结合其它方式进一步提高比容,例如负电极对应的外延层下方制作有背面金属化孔,用以实现更大比容的旁路电容,具有较高的实际应用价值。

技术特征:

1.一种半导体大容值电容结构的制造方法,其特征在于,所述方法包括:

2.根据权利要求1所述的一种半导体大容值电容结构的制造方法,其特征在于,所述负电极(8)为长条状结构。

3.根据权利要求1所述的一种半导体大容值电容结构的制造方法,其特征在于,所述衬底(1)为碳化硅衬底。

4.根据权利要求1所述的一种半导体大容值电容结构的制造方法,其特征在于,所述外延沟道层(2)为gan外延沟道层。

5.根据权利要求1所述的一种半导体大容值电容结构的制造方法,其特征在于,所述外延势垒层(3)为alxga1-xn外延势垒层。

6.根据权利要求5所述的一种半导体大容值电容结构的制造方法,其特征在于,所述外延势垒层(3)的厚度为10nm~100nm。

7.根据权利要求5所述的一种半导体大容值电容结构的制造方法,其特征在于,所述第一介质层(7)为sinx介质层。

8.根据权利要求7所述的一种半导体大容值电容结构的制造方法,其特征在于,所述第二介质层(9)为sinx介质层。

9.根据权利要求1所述的一种半导体大容值电容结构的制造方法,其特征在于,所述负电极(8)对应的外延层(2)下方制作有背面金属化孔(11)。

10.根据权利要求1所述的一种半导体大容值电容结构的制造方法,其特征在于,所述隔离区(5)呈方型环状。

技术总结

本发明公开了一种半导体大容值电容结构的制造方法,包括:制作衬底,并在所述衬底上依次制作外延沟道层以及外延势垒层,在外延沟道层和外延势垒层的界面处形成二维电子气;在所述外延沟道层上制作正电极的欧姆接触;制作隔离区,让隔离区贯穿所述外延沟道层并延伸至所述衬底中;在外延势垒层上沉积第一介质层,在所述第一介质层中刻蚀,制作肖特基接触,形成负电极;在所述第一介质层上沉积第二介质层,在与所述正电极的欧姆接触对应的位置处刻蚀窗口,并在窗口处沉积金属将正电极引出,所述沉积金属延伸覆盖在第二介质层上。本发明将二维电子气作为电容的内部电极实现电极的横向引出,选用反型的薄层外延势垒层作为电容介质层,实现大比容量片上电容,且工艺简单,易于集成。

技术研发人员:何泽涛,黎明,蒲云霄

受保护的技术使用者:成都海威华芯科技有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!