传感器的制作方法

本技术涉及光电探测器,例如,涉及一种适合应用于雪崩光电二极管的光电探测器。

背景技术:

1、雪崩光电二极管(apd)具有盖革模式(geiger mode)和线性模式,在盖革模式中,雪崩光电二极管在低于击穿电压的偏置电压下工作,而在线性模式中,它在击穿电压附近以稍高的偏置电压工作。盖革模式下的雪崩光电二极管也被称为单光子雪崩光电二极管(spad)。

2、spad是一种能够通过如下处理以像素为基础检测单个光子的设备,在该处理中,通过光电转换产生的载流子在以像素为基础设置的高电场pn结区域中被倍增。

3、在专利文献1中,为了提高spad像素的灵敏度,提出了一种用于形成高电场区域的层被嵌入并且被偏压耗尽的技术。在专利文献2中,提出了一种通过具有像素之间的隔离的结构来实现减少由于高电场区域中的光发射而对相邻像素的串扰的技术。

4、[引用列表]

5、[专利文献]

6、[专利文献1]:jp 2015-41746a

7、[专利文献2]:jp 2013-48278a

技术实现思路

1、技术问题

2、在专利文献1中,在载流子倍增时,像素中的高电场区域中的光发射可能导致光子入射到相邻像素上,从而可能意外地在相邻像素中检测到信号。此外,倍增时的电流可能改变阱电位,从而可能改变相邻像素中的电场,并可能改变spad特性。

3、在专利文献2中,为了减少串扰,在像素之间形成隔离区域。通过使用绝缘膜在像素之间进行物理隔离对于减少串扰是最有效的。但是,众所周知,在绝缘膜与硅之间的界面处会产生暗电流。因此,根据专利文献2,可能会产生暗电流。在界面处产生的暗电流的倍增可能会使dcr(暗计数率)变差。

4、本技术是考虑到上述情况而作出的。因此,本技术的目的是旨在提供一种能够减少串扰并抑制dcr的apd。

5、技术方案

6、根据本技术的一个方面,传感器包括具有至少第一像素的第一基板。第一像素包括雪崩光电二极管以将入射光转换成电荷,还包括阳极和阴极。阴极位于第一基板的阱区中。第一像素包括将阱区与相邻于第一像素的至少第二像素隔离的隔离区域。第一像素包括隔离区域与阱区之间的空穴累积区域。空穴累积区域电连接到阳极。

7、根据本技术的第二方面,传感器包括具有至少一个像素的基板。至少一个像素包括雪崩光电二极管以将入射光转换成电荷,还包括第一导电类型的阴极和第二导电类型的阳极。阴极位于第一导电类型的阱区中,阳极位于阱区的周边。所述至少一个像素包括阱区周围的第二导电类型的第一材料。第一材料电连接到阳极。所述至少一个像素包括围绕第一材料和阳极的绝缘材料。

8、根据本技术的第三方面,传感器包括在像素区域中具有至少第一像素的第一基板。第一像素包括雪崩光电二极管以将入射光转换成电荷,还包括第一区域、第二区域和第三区域。第一区域和第三区域是第一导电类型并层叠。第二区域是第二导电类型。第一像素包括将第三区域与至少第二像素隔离的隔离区域,其中,隔离区域贯穿第一基板。第一像素包括位于第三区域与隔离区域之间的第二导电类型的电荷累积区域。电荷累积区域电连接至第二区域。

9、在本技术的至少一个附加方面中,设置有高电场区域、用于与相邻像素隔离的隔离区域、以及累积隔离区域的侧壁上的电子的电子累积区域,并且电子累积区域与阳极电连接。

10、本发明的有利效果

11、根据本技术的方面,能够提供能够减少串扰并抑制dcr的apd。

12、注意,这里描述的效果不一定是限制性的,而且可以获得在此描述的任何效果。

技术特征:

1.一种传感器,其包括:

2.根据权利要求1所述的传感器,其中,所述第一配线和所述第三配线与所述第一雪崩光电二极管重叠。

3.根据权利要求2所述的传感器,其中,所述第二配线和所述第四配线至少部分地与所述第一雪崩光电二极管重叠。

4.根据权利要求1所述的传感器,其中,所述第一隔离区域包括第一金属膜。

5.根据权利要求4所述的传感器,其中,所述第一隔离区域包括间隙区域,所述第一金属膜至少部分地围绕所述间隙区域。

6.根据权利要求1所述的传感器,还包括片上透镜,所述片上透镜位于所述第一半导体层上。

7.根据权利要求6所述的传感器,其中,所述片上透镜位于所述第一半导体层的光入射面上。

8.根据权利要求6所述的传感器,其中,所述片上透镜位于附接至所述第一隔离区域的第一膜上。

9.根据权利要求4所述的传感器,其中,所述第一隔离区域包括附接至所述第一金属膜的第二膜。

10.根据权利要求9所述的传感器,其中,所述第一膜附接至所述第二膜。

11.根据权利要求7所述的传感器,其中,所述第一隔离区域穿透所述第一半导体层的所述光入射面。

12.一种传感器,其包括:

13.根据权利要求12所述的传感器,其中,所述第一配线和所述第三配线与所述第一雪崩光电二极管重叠。

14.根据权利要求13所述的传感器,其中,所述第二配线和所述第四配线至少部分地与所述第一雪崩光电二极管重叠。

15.根据权利要求12所述的传感器,其中,所述第一隔离区域包括第一金属膜。

16.根据权利要求15所述的传感器,其中,所述第一隔离区域包括间隙区域,所述第一金属膜至少部分地围绕所述间隙区域。

17.根据权利要求12所述的传感器,还包括片上透镜,所述片上透镜位于所述第一半导体层上。

18.根据权利要求17所述的传感器,其中,所述片上透镜位于所述第一半导体层的光入射面上。

19.根据权利要求17所述的传感器,其中,所述片上透镜位于附接至所述第一隔离区域的第一膜上。

20.一种传感器,其包括:

21.根据权利要求20所述的传感器,其中,所述第一配线和所述第三配线与所述第一雪崩光电二极管重叠。

22.根据权利要求21所述的传感器,其中,所述第二配线和所述第四配线至少部分地与所述第一雪崩光电二极管重叠。

23.根据权利要求20所述的传感器,其中,所述第一隔离区域包括第一金属膜。

24.根据权利要求23所述的传感器,其中,所述第一隔离区域包括间隙区域,所述第一金属膜至少部分地围绕所述间隙区域。

25.根据权利要求20所述的传感器,其中,所述片上透镜位于所述第一半导体层上。

26.根据权利要求25所述的传感器,其中,所述片上透镜位于所述半导体层的光入射面上。

27.根据权利要求25所述的传感器,其中,所述片上透镜位于附接至所述第一隔离区域的第一膜上。

28.一种飞行时间系统,其包括:

29.根据权利要求28所述的飞行时间系统,其中,所述第一配线和所述第三配线与所述第一雪崩光电二极管重叠。

30.根据权利要求29所述的飞行时间系统,其中,所述第二配线和所述第四配线至少部分地与所述第一雪崩光电二极管重叠。

技术总结

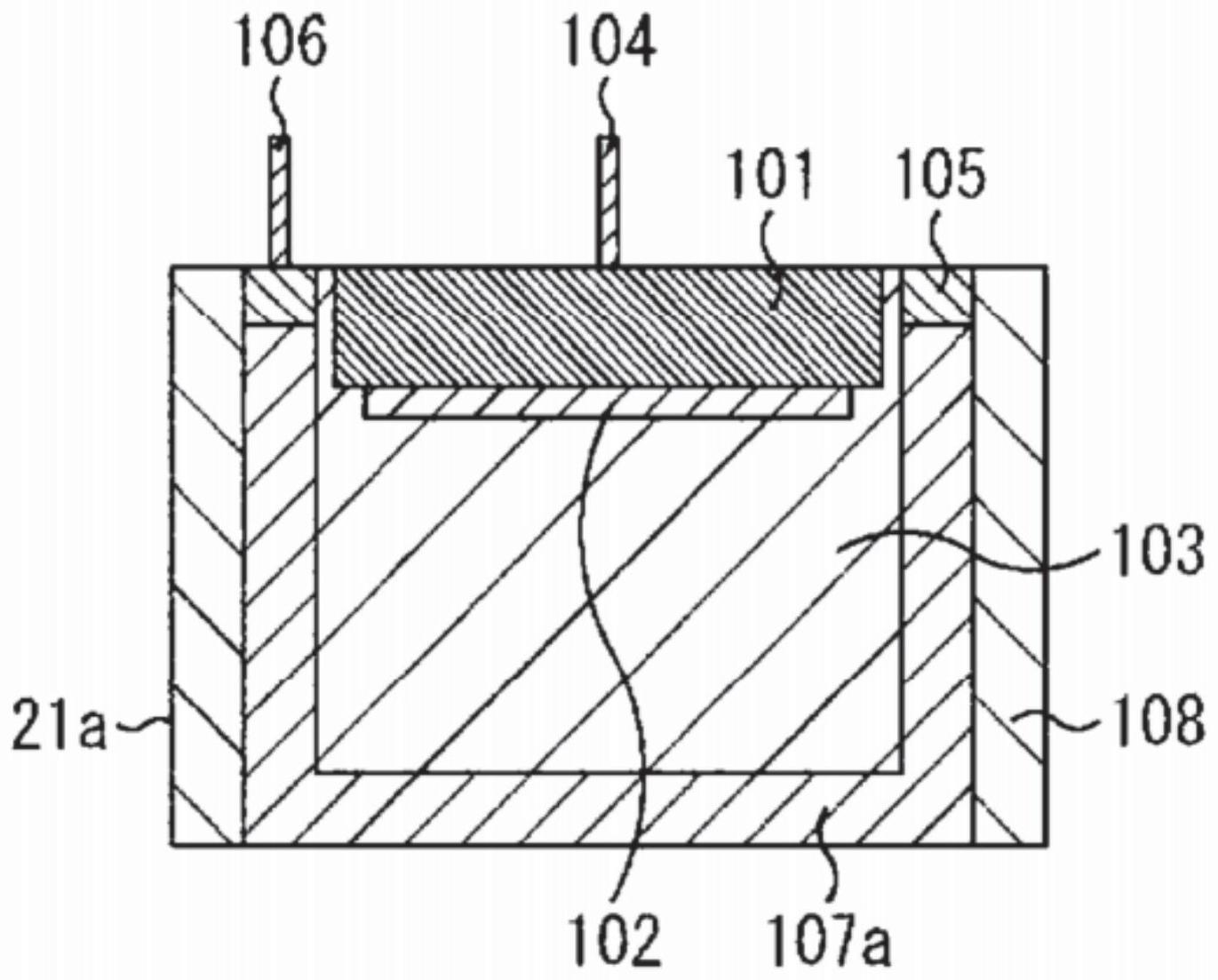

本发明涉及传感器和飞行时间系统。其中,所述传感器可包括:第一基板,包括:第一半导体层,所述第一半导体层包括:第一雪崩光电二极管,其包括第一阴极区域和第一阳极区域;和第一隔离区域,第一配线层,所述第一配线层包括:第一配线;第一通孔,第一阴极区域通过所述第一通孔电连接至第一配线;第二配线;和第二通孔,第一阳极区域通过所述第二通孔电连接至所述第二配线;以及第二基板,所述第二基板层叠在所述第一基板上,所述第二基板包括:第二配线层,所述第二配线层包括:直接接合至所述第一配线的第三配线;直接接合至所述第二配线的第四配线;和第二半导体层,所述第一阳极区域位于所述第一阴极区域和所述第一隔离区域之间。

技术研发人员:大竹悠介,松本晃,山元纯平,内藤隆诚,中沟正彦,若野寿史

受保护的技术使用者:索尼半导体解决方案公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!